EMBEDDED

# **SYSTEMS**

# PROGRAMMING

# <u>WITH</u> <u>THE</u>

# <u>PIC16F877</u>

Second Edition

By Timothy D. Green

Copyright 2008 by Timothy D. Green All Rights Reserved.

# Table of Contents

| Preface                                                  | 5    |

|----------------------------------------------------------|------|

| List of Figures                                          | 6    |

| Abbreviations and Acronyms                               | . 7  |

| Trademarks                                               | . 10 |

|                                                          |      |

| Chapter 1 Introduction to ESP and the PIC                |      |

| Chapter 2 Microcontrollers and the PIC16F877             | . 15 |

| Section 2.0 Chapter Summary                              |      |

| Section 2.1 Memory and Memory Organization               | 15   |

| Section 2.2 The PIC16F877                                | 16   |

| Section 2.3 Programming the PIC                          |      |

| Chapter 3 Simple PIC Hardware & Software ("Hello World") | 20   |

| Section 3.0 Chapter Summary                              | . 20 |

| Section 3.1 A Simple Example System                      |      |

| Section 3.2 Summary of Instructions and Concepts         | . 25 |

| Chapter 4 The PIC Instruction Set (Part I)               | . 27 |

| Section 4.0 Chapter Summary                              | 27   |

| Section 4.1 The PIC16F877 Instruction Set                | 27   |

| Section 4.2 Summary of Instructions and Concepts         | . 33 |

| Chapter 5 The PIC Instruction Set (Part II)              | . 34 |

| Section 5.0 Chapter Summary                              | . 34 |

| Section 5.1 Introduction                                 | . 34 |

| Section 5.2 Keypad and Display Interface                 | . 35 |

| Section 5.3 The STATUS Register and Flag Bits            | . 39 |

| Section 5.4 The Keypad Software                          |      |

| Section 5.5 The LED Display Software                     | . 43 |

| Section 5.6 Improved Display and Indirect Addressing     | . 46 |

| Section 5.7 Odds & Ends                                  | . 50 |

| Section 5.8 Using KEY_SCAN and DISPLAY Together          | 54   |

| Section 5.9 A Last Look at the Advanced Security System  |      |

| Section 5.10 Summary of Instructions and Concepts        | . 57 |

| Chapter 6 Fundamental ESP Techniques                     | . 59 |

| Section 6.0 Chapter Summary                              |      |

| Section 6.1 Introduction                                 |      |

| Section 6.2 Software Readability                         |      |

| Section 6.3 Software Maintainability                     |      |

| Chapter 6                                              |     |

|--------------------------------------------------------|-----|

| Section 6.4 Software Fundamentals                      | 60  |

| Section 6.5 The Background Routine                     | 61  |

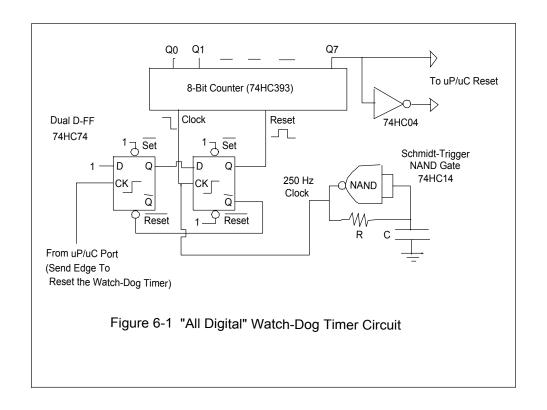

| Section 6.6 The Watch-Dog Timer                        | 61  |

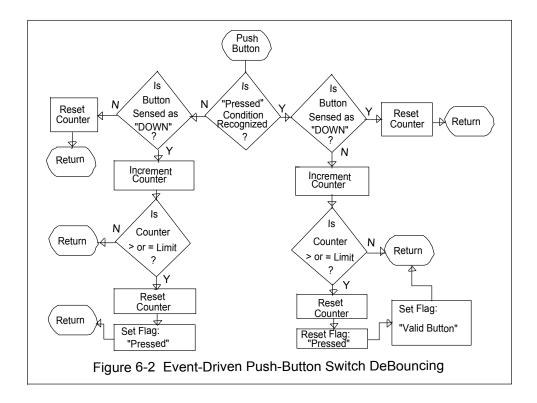

| Section 6.7 Event-Driven Software                      |     |

| Section 6.8 Interrupts                                 | 65  |

| Section 6.9 Slow Inputs and Outputs                    | 65  |

| Section 6.10 Software Time Measurement                 | 66  |

| Section 6.11 Hashing                                   | 67  |

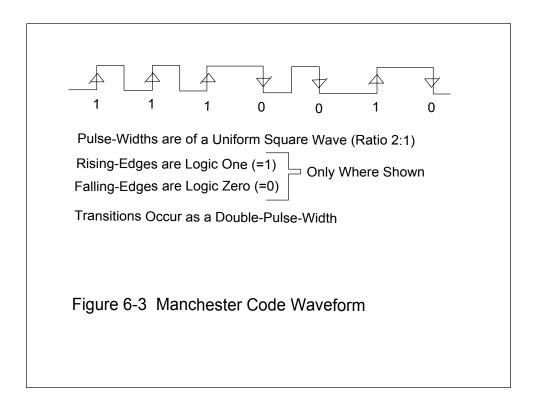

| Section 6.12 Waveform Encoding                         |     |

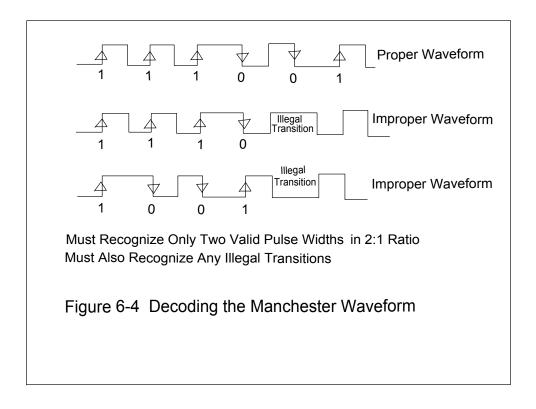

| Section 6.13 Waveform Decoding                         |     |

| Section 6.14 RAM, ROM, and Time Tradeoffs              |     |

| Section 6.15 ROM States                                |     |

| Section 6.16 Limitations of C/C++                      | 76  |

| Chapter 7 Advanced ESP                                 | 78  |

| Section 7.0 Chapter Summary                            | 78  |

| Section 7.1 Introduction                               | 78  |

| Section 7.2 Sine Wave Generation                       | 78  |

| Section 7.3 Dual-Tone-Multi-Frequency (DTMF) Signaling | g81 |

| Section 7.4 Pulse-Width Modulation                     |     |

| Section 7.5 ADPCM Data Compression                     | 84  |

| Section 7.6 Test Functions and System Ideas            | 87  |

| Chapter 8 PIC Peripherals and Interrupts               | 91  |

| Section 8.0 Chapter Summary                            | 91  |

| Section 8.1 Overview of the PIC Peripherals            | 91  |

| Section 8.2 Input/Output Ports                         | 93  |

| Section 8.2.1 Port A                                   | 93  |

| Section 8.2.2 Port B, Port C, Port D                   | 95  |

| Section 8.2.3 Port E                                   | 95  |

| Section 8.3 Interrupts                                 | 95  |

| Section 8.4 ADC and Analog MUX                         |     |

| Section 8.5 Watch-Dog Timer                            |     |

| Section 8.6 Timer 0                                    | 103 |

| Section 8.7 Timer 1                                    | 105 |

| Section 8.8 Timer 2                                    | 106 |

| Section 8.9 Capture Mode                               |     |

| Section 8.10 Compare Mode                              |     |

| Section 8.11 Pulse-Width Modulation (PWM)              |     |

| Section 8.12 Parallel Slave Port                       |     |

| Chapter 8                                                    |     |

|--------------------------------------------------------------|-----|

| Section 8.13 EEPROM Data Memory                              | 116 |

| Section 8.14 FLASH Program Memory                            |     |

| Section 8.15 FLASH Code & Data EEPROM Protection             |     |

| Section 8.16 The CONFIGURATION Word                          | 119 |

| Section 8.17 Sleep Modes & Reset Modes                       | 120 |

| Chapter 9 PIC Peripherals, Serial Communications Ports       | 122 |

| Section 9.0 Chapter Summary                                  | 122 |

| Section 9.1 Introduction                                     | 122 |

| Section 9.2 USART (Overview)                                 | 122 |

| Section 9.2.1 USART (Asynchronous Mode, Full-Duplex).        | 123 |

| Section 9.2.2 USART (Synchronous, Master Mode)               | 127 |

| Section 9.2.3 USART (Synchronous, Slave Mode)                | 128 |

| Section 9.3 Serial Peripheral Interface (Master Mode)        | 128 |

| Section 9.4 Serial Peripheral Interface (Slave Mode)         | 132 |

| Section 9.5 I2C System Overview                              |     |

| Section 9.5.1 I2C Slave Mode                                 |     |

| Section 9.5.2 I2C Master Mode                                | 139 |

| Chapter 10 DSP Fundamentals                                  | 147 |

| Section 10.0 Chapter Summary                                 |     |

| Section 10.1 Introduction                                    |     |

| Section 10.2 An Example: A Low-Pass Filter                   |     |

| Section 10.3 An Example: A High-Pass Filter                  | 148 |

| Section 10.4 DSP Filters in General                          |     |

| Section 10.5 Aliasing and the Nyquist Sampling Theorem       |     |

| Section 10.6 DSP Cookbook I: A Simple LPF/HPF                |     |

| Section 10.7 DSP Cookbook II: A Simple BPF                   |     |

| Section 10.8 DSP Cookbook III: A Median Filter               |     |

| Section 10.9 DSP Example I: Standard DTMF Decoding           |     |

| Section 10.10 DSP Example II: Alternative DTMF Decodir       | •   |

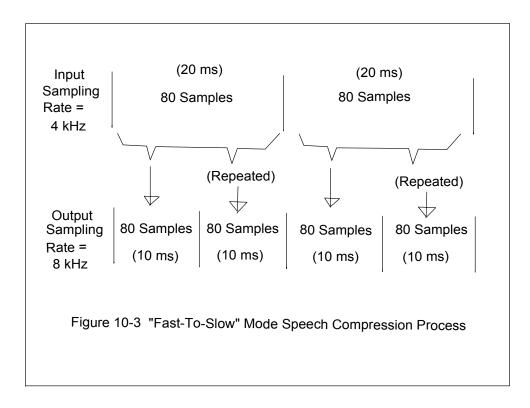

| Section 10.11 DSP Application: Speech Compression            |     |

| Appendix A The PIC16F877 Instruction Set                     |     |

| Appendix B Useful C++ Programs for PIC ASM Applications      |     |

| Appendix C Special Function Registers (RAM Addresses & Bits) |     |

| Appendix D PIC16F877 Register File Map                       |     |

| Appendix E PIC16F877 Pin Function Map                        |     |

| Appendix F Save/Restore Registers on Interrupt               |     |

| References                                                   | 195 |

## Preface

This book is intended for use by Junior-level undergraduates, Senior-level undergraduates, and Graduate students in electrical engineering as well as practicing electrical engineers and hobbyists and seeks to provide a gentle introduction to embedded systems programming with the Microchip PIC16F877 microcontroller. After introducing the PIC16F877 and its programming, this book covers the fundamental techniques and advanced level techniques of embedded systems programming in a general sense. The general sense ESP techniques can be applied to *any* microcontroller. There is also an introduction to the fundamentals of digital signal processing (DSP) using the PIC16F877.

I would like to thank Dr. Dan Simon of the Cleveland State University Electrical Engineering Department for his kind and valuable help and suggestions in the preparations for this book. I would also like to thank John R. Owerko and James R. Jackson, both of A.R.F Products, Inc., for their expertise in the security systems market. I owe them both a great debt for my knowledge of security systems and for expanding my knowledge of the techniques of embedded systems programming in general.

Special thanks also go to Sister Renee Oliver who proofread the manuscript and offered many helpful suggestions. Thanks go to my friends Damian Poirier, Jim Strieter, Greg Glazer, Zarif Bastawros, Brian McGeever, Ted Seman, and Jim Chesebrough who offered many helpful suggestions.

Any errors that remain in the text are mine and I will correct them in the next edition.

Timothy D. Green November 2005 Cleveland, Ohio

# List of Figures

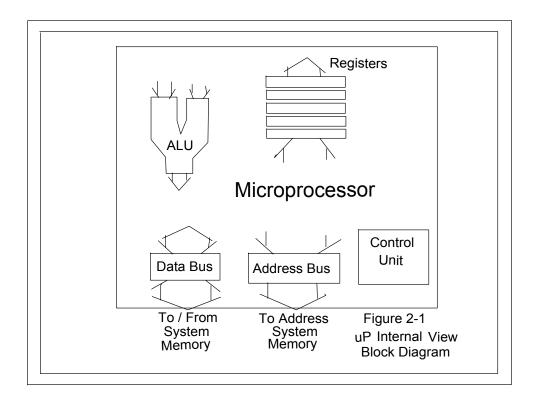

- 2-1 uP Internal View Block Diagram

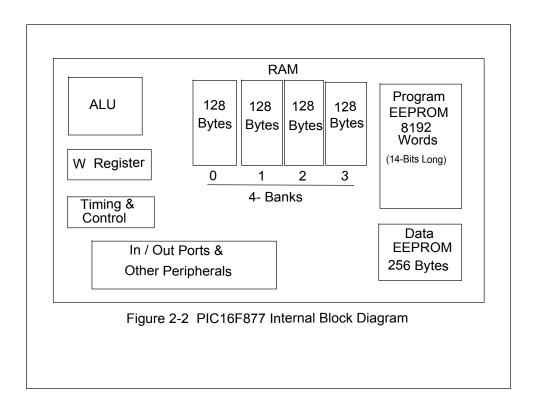

- 2-2 PIC16F877 Internal Block Diagram

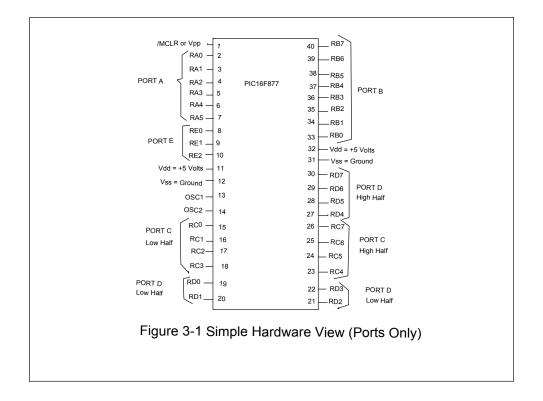

- 3-1 Simple Hardware View (Ports Only)

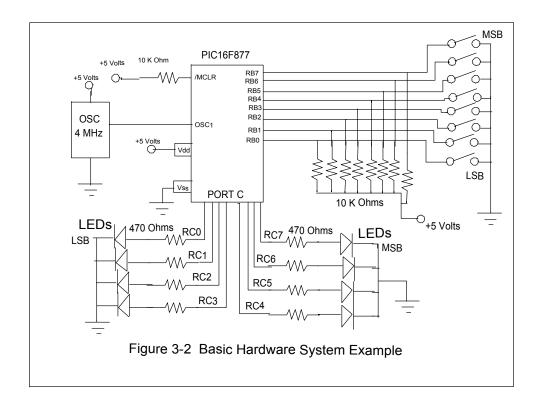

- 3-2 Basic Hardware System Example

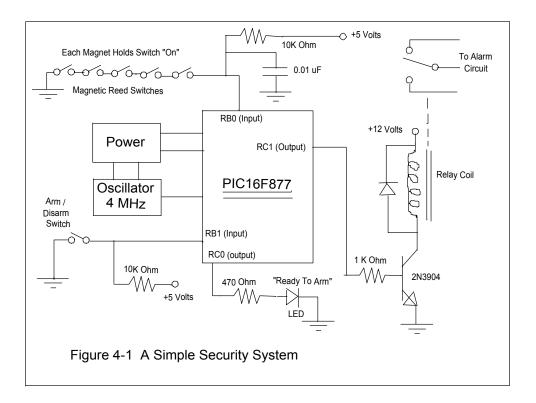

- 4-1 A Simple Security System

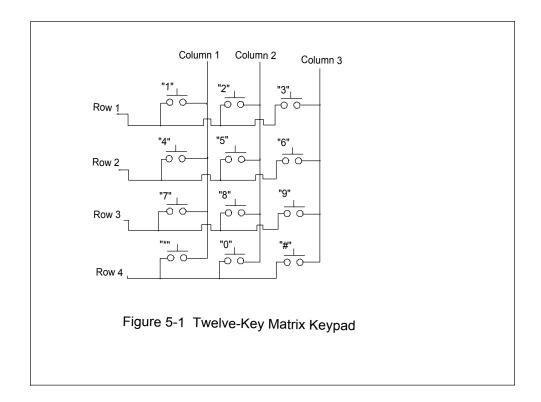

- 5-1 Twelve-Key Matrix Keypad

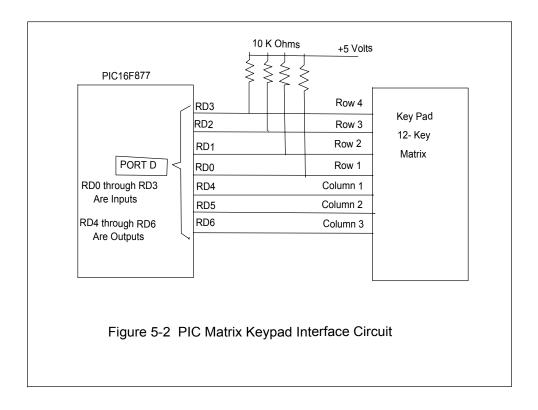

- 5-2 PIC Matrix Keypad Interface Circuit

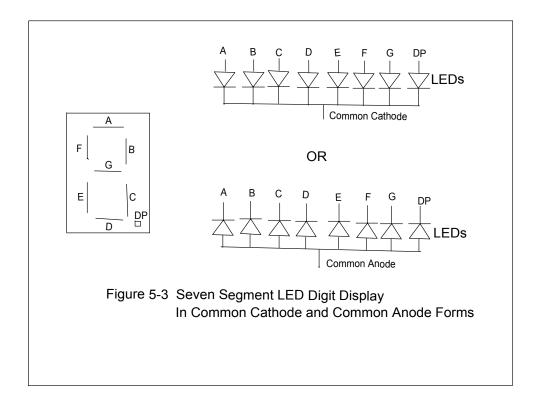

- 5-3 Seven Segment LED Digit Display in Common Cathode and Common Anode Forms

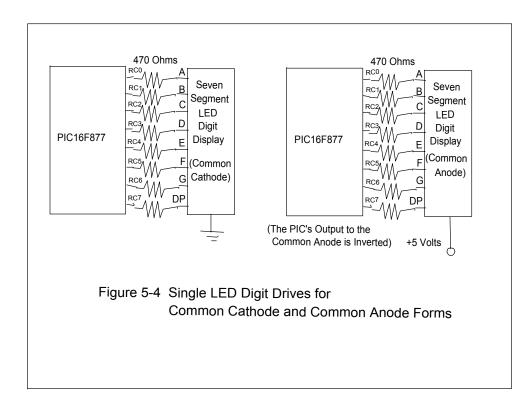

- 5-4 Single LED Digit Drives for Common Cathode/Anode Forms

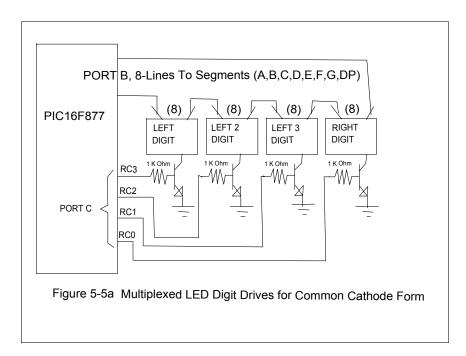

- 5-5a Multiplexed LED Digit Drives for Common Cathode Form

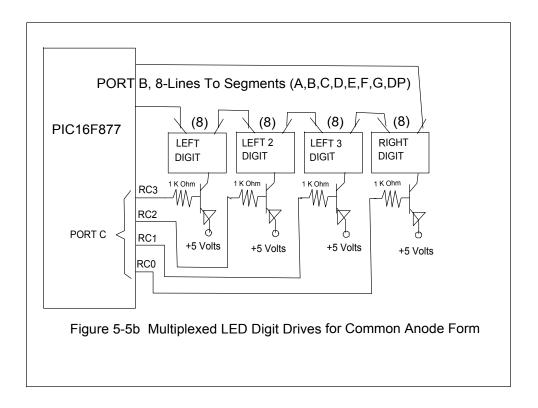

- 5-5b Multiplexed LED Digit Drives for Common Anode Form

- 5-6 Illustration of Indirect RAM Addressing

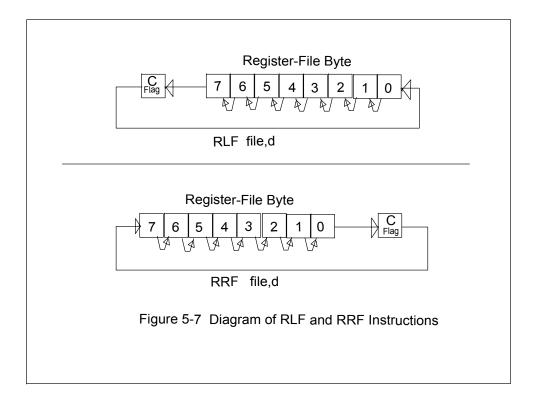

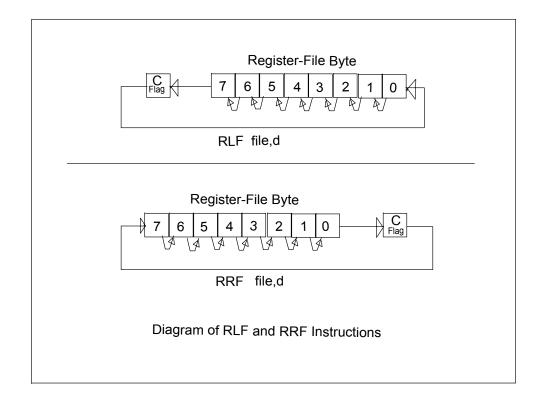

- 5-7 Diagram of RLF and RRF Instructions

- 6-1 "All Digital" Watch-Dog Timer Circuit

- 6-2 Event-Driven Push-Button Switch DeBouncing

- 6-3 Manchester Code Waveform

- 6-4 Decoding of Manchester Waveform

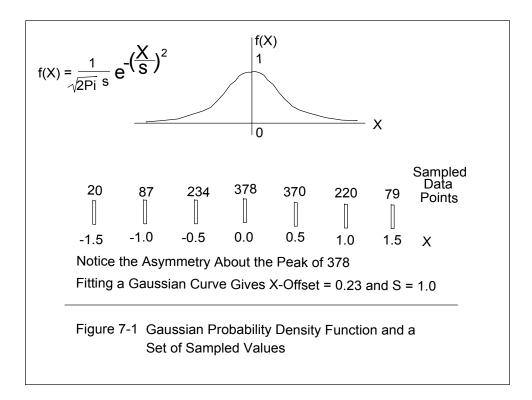

- 7-1 Gaussian Probability Density Function and a Set of Sampled Values

- 8-1 ADCON1 "Analog vs Digital" Selection Codes

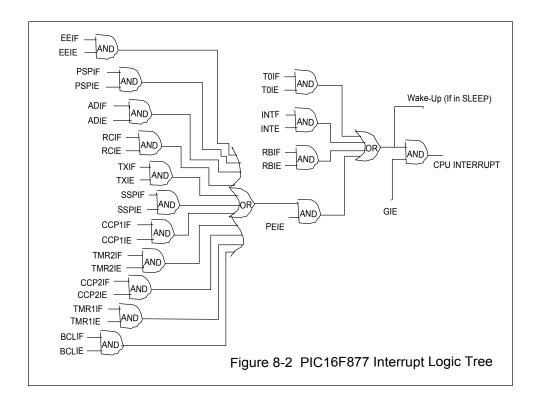

- 8-2 PIC16F877 Interrupt Tree

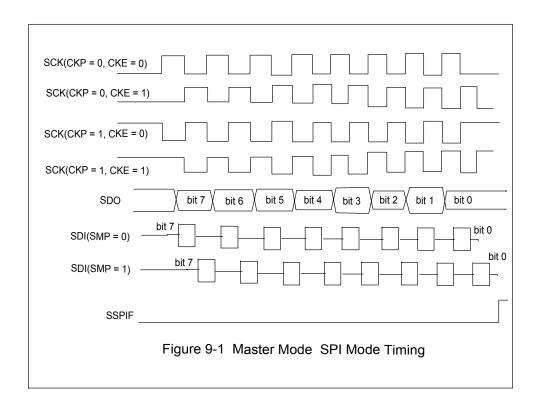

- 9-1 Master Mode SPI Mode Timing

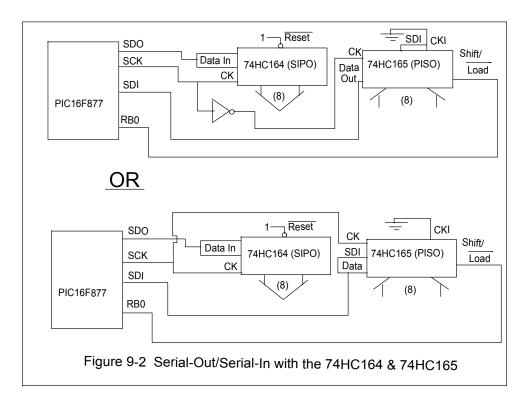

- 9-2 Serial-Out/Serial-In with the 74HC164 and 74HC165

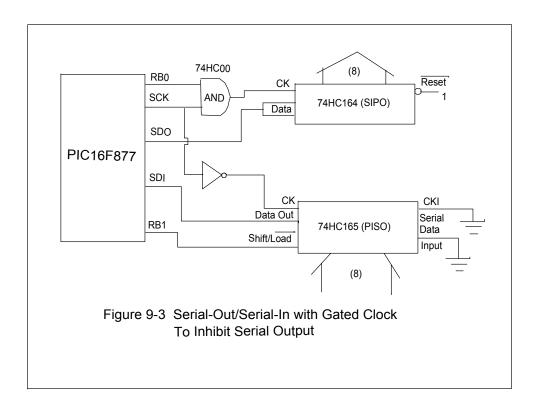

- 9-3 Serial-Out/Serial-In with Gated Clock to Inhibit Serial Out

- 9-4 SPI Mode Timing (Slave Mode, CKE = 0)

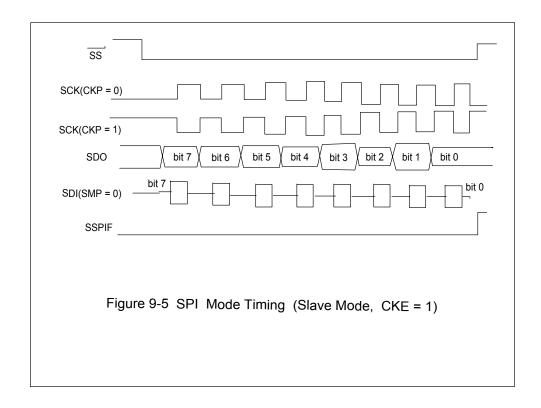

- 9-5 SPI Mode Timing (Slave Mode, CKE = 1)

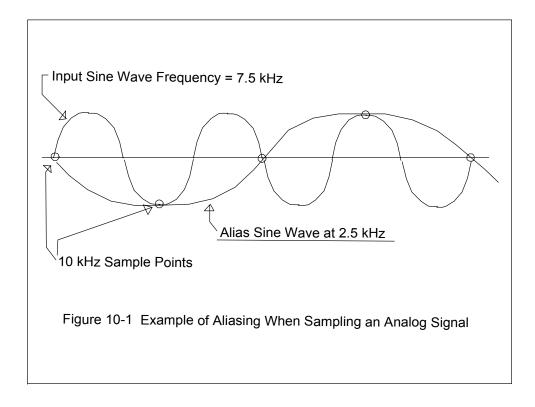

- 10-1 Example of Aliasing When Sampling an Analog Signal

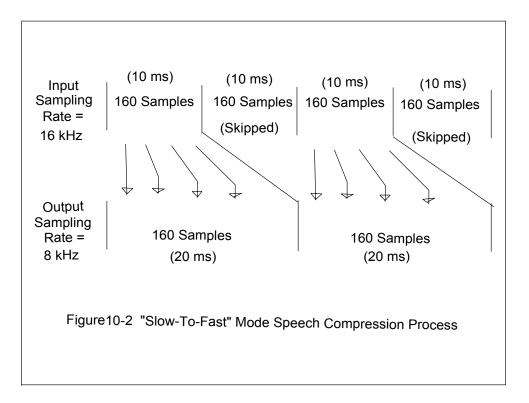

- 10-2 "Slow-to-Fast" Mode Speech Compression Process

- 10-3 "Fast-to-Slow" Mode Speech Compression Process

Appendix A Figure: Diagram of RLF and RRF Instructions

# Abbreviations and Acronyms

| ABS<br>ACCUM<br>ADC<br>ADPCM<br>ALU  | <ul> <li>= Absolute Value</li> <li>= Accumulator</li> <li>= Analog-to-Digital Converter</li> <li>= Adaptive Differential Pulse Code Modulation</li> <li>= Arithmetic Logic Unit</li> </ul>                                   |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arccos<br>ASCII<br>ATM<br>BOR<br>BPF | <ul> <li>Arc-Cosine</li> <li>American Standard Code for Information Interchange</li> <li>Automatic Teller Machine</li> <li>Brown Out Reset</li> <li>Band Pass Filter</li> </ul>                                              |

| CK<br>Cos<br>CPU<br>D<br>DAC         | <ul> <li>= Clock</li> <li>= Cosine</li> <li>= Central Processing Unit</li> <li>= Data</li> <li>= Digital-to-Analog Converter</li> </ul>                                                                                      |

| dB<br>DC<br>DDS<br>DIP<br>DPSK       | <ul> <li>Decibels</li> <li>Direct Current</li> <li>Direct Digital Synthesis</li> <li>Dual Inline Package</li> <li>Differential Phase Shift Keying</li> </ul>                                                                 |

| DSP<br>DTMF<br>EEPROM<br>EMC<br>EMI  | <ul> <li>Digital Signal Processing</li> <li>Dual Tone Multi-Frequency</li> <li>Electrically Erasable Programmable Read Only Memory</li> <li>Electro-Magnetic Compatibility</li> <li>Electro-Magnetic Interference</li> </ul> |

| EPROM<br>ESP<br>Fmax<br>Fosc<br>Freq | <ul> <li>= Erasable Programmable Read Only Memory</li> <li>= Embedded Systems Programming</li> <li>= Maximum Frequency</li> <li>= Oscillator Frequency (of the PIC)</li> <li>= Frequency</li> </ul>                          |

| FSK<br>HPF<br>Hz<br>IIC or I2C<br>INT   | <ul> <li>Frequency Shift Keying</li> <li>High Pass Filter</li> <li>Hertz</li> <li>Inter-Integrated Circuit</li> <li>Interrupt</li> </ul>                                                                       |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O<br>ISR<br>kHz<br>LED<br>LPF         | <ul> <li>Input/Output</li> <li>Interrupt Service Routine</li> <li>Kilohertz</li> <li>Light Emitting Diode</li> <li>Low Pass Filter</li> </ul>                                                                  |

| Max<br>MHz<br>Min<br>ms<br>MSSP         | <ul> <li>Maximum</li> <li>Megahertz</li> <li>Minimum</li> <li>Milliseconds</li> <li>Master Synchronous Serial Port</li> </ul>                                                                                  |

| OSC<br>PC<br>PIC<br>PISO<br>PLL         | <ul> <li>= Oscillator</li> <li>= Personal Computer or Program Counter</li> <li>= Peripheral Interface Controller</li> <li>= Parallel-In, Serial-Out (Shift Register)</li> <li>= Phase-Locked Loop</li> </ul>   |

| POR<br>PROM<br>PSP<br>PWM<br>Q          | <ul> <li>Power-On Reset</li> <li>Programmable Read Only Memory</li> <li>Parallel Slave Port</li> <li>Pulse Width Modulation</li> <li>Flip-Flop, Counter, or Shift Register Output State (Data Out)</li> </ul>  |

| RAM<br>RC<br>RF<br>RFI<br>ROM           | <ul> <li>Random Access Memory (A Read/Write Memory)</li> <li>Resistor/Capacitor (Time Constant or Circuit)</li> <li>Radio Frequency</li> <li>Radio Frequency Interference</li> <li>Read Only Memory</li> </ul> |

| Sin or sin<br>SIPO<br>SPI<br>sqrt<br>SR | <ul> <li>Sine</li> <li>Serial-In, Parallel-Out (Shift Register)</li> <li>Serial Peripheral Interface</li> <li>Square Root</li> <li>Sampling Rate</li> </ul>                                                    |

| uC    | = Microcontroller                                         |

|-------|-----------------------------------------------------------|

| uP    | = Microprocessor                                          |

| USART | = Universal Synchronous/Asynchronous Receiver/Transmitter |

| WDT   | = Watch-Dog Timer                                         |

| XTAL  | = Quartz Crystal (Sets Oscillator Frequncy)               |

## **Trademarks**

IBM and IBM-PC are registered trademarks of International Business Machines, Inc.

PIC, PIC16F87X, PIC16F877, MPLAB, MPASM, In-Circuit Debugger, In-Circuit Serial Programmer are registered trademarks of Microchip Technology, Inc.

CTI and CTI Speech Compressor are registered trademarks of Compressed Time, Inc.

Touch Tone, Unix, C, and C++ are registered trademarks of AT&T, Inc.

Linux is a registered trademark of the Free Software Foundation.

I2C, IIC, and Inter-Integrated Circuit are registered trademarks of Philips Corp.

The PIC Instruction Set, Assembly Keywords, and Mnemonics are Copyrighted by Microchip Technology, Inc.

Maxim and MAX690CPA are registered trademarks of Maxim Corporation.

Borland, Turbo, Turbo C++ are registered trademarks of Inprise, Inc.

# Chapter 1: Introduction to ESP and the PIC

An embedded system is a product which uses a computer to run it but the product, itself, is not a computer. This is a very broad and very general definition. Embedded systems programming, therefore, consists of building the software control system of a computer-based product. ESP encompasses much more than traditional programming techniques since it actually controls hardware in advance of real time. ESP systems often have limitations on memory, speed, and peripheral hardware. The goals of ESP programmers are to get the "maximum function and features in the minimum of space and in minimum time".

Embedded systems are everywhere! Name almost any appliance in your home or office and it may have a microprocessor or a microcomputer to run it. A watch, microwave oven, telephone, answering machine, washer, dryer, calculator, toy, robot, test equipment, medical equipment, traffic light, automobile computer, VCR, CD player, DVD player, TV, radio, and printer all have computers in them to run them.

These examples of embedded systems are simple but the concept of embedded systems applies to much larger systems as well. Overall, there are four levels of size, option, and complexity in embedded systems. These levels are:

- 1) High Level

- 2) Medium Level

- 3) Low level with hardware

- 4) Low level without hardware

A good example of a high level embedded system is an air-traffic control system. It would use a main-frame computer with many terminals and many users on a timesharing basis. It would connect to several smaller computers, run the radar, receive telemetry, get weather information, have extensive communications sub-systems, and coordinate all of these function in an orderly, systematic way. It is necessarily a highreliability system and may, therefore, have extensive backup systems. It would have a custom-built operating system that would be completely dedicated to controlling airtraffic.

An example of a medium level embedded system is a typical automatic teller machine (ATM) at any bank or bank terminal. It may use a more advanced microprocessor with many peripheral functions. Consider that it contains a video terminal, a keyboard, a card-reader, a printer, the money-dispensing unit, a modem, and many input/output ports. The ATM probably doesn't use a custom operating system but would use something off the shelf, like Unix or Linux. The controlling software is probably written in a high-level language like C or C++.

The appliances and other things given on page 11 are all examples of the lowlevel-with-hardware embedded systems. They do not use microprocessors but do use microcontrollers, which are complete computers on a single chip. Microcontrollers have a CPU, RAM, ROM, and, typically, several peripheral hardware modules which are builtin and are under software control. The PIC16F877 is such a microcontroller. Any of the example products and applications on page 11 could be controlled by the PIC. They could be programmed in C or C++ but care would be needed so as not to use too much RAM or ROM inadvertently. The process or program also must not need very high speed operation – it should not be timing-critical. More control, stability, memory management, and speed can be gained by programming in assembly languages. The programming at the low-level will interact with the hardware in much finer detail than in the medium-level or the high-level systems.

The low-level-without-hardware embedded systems are almost identical to the low-level-with-hardware systems and can run exactly the same products, devices, and applications. The differences which are present in the low-level-without-hardware systems are that the microcontroller and the system have an absolute minimum of hardware peripheral functions. At this level, the software must mimic the desired hardware peripheral functions. This puts a much greater challenge on the ESP programmer. (Assembly language is a MUST.)

There are several characteristics in ESP that separate it from traditional programming techniques. They are as follows:

- 1) ESP is all about process control and control systems. ESP is what runs a given product.

- 2) ESP systems must run in "real-time". The program must keep pace or stay ahead of the real world and its timing. For example, a telephone answering machine may use a complex algorithm to compress, expand, encode, and decode speech signals. The ESP program must be able to run these processes as speech is coming in or going out. There must be no delays. A traditional program would not be sensitive to the requirements of speed that are needed here.

- 3) ESP software must run with infinity-loops. If they didn't, the products could not run at all! In contrast, infinity-loops are the cardinal sin of traditional programming.

- ESP software often uses "event-driven" techniques, especially at the lowlevels. These techniques are highly structured and save operating time. Traditional programming may also use "event-driven" techniques but it is not critical.

- 5) Low-level ESP software systems must sometimes mimic the hardware that the product needs. There is no parallel to this in traditional programming.

- 6) Embedded systems usually have far less memory than traditional programming environments. This eliminates heavy nesting of subroutines and recursive subroutine calls.

7) The arithmetic/logic unit of a microcontroller is much smaller than ones in a traditional setting, and, consequently, ESP is not as mathematically oriented as a traditional program.

Embedded systems programming at the low levels is necessarily a multi-disciplinary field. The programmers and designers must consider hardware issues, manufacturing issues, electromagnetic interference/electromagnetic compatibility problems, and noise limitations.

Low-level code doesn't just consist of algorithms but the code, itself, is, at times, a great function of the code geometry. Getting optimum performance of low-level embedded code depends very much on how the instructions are placed in program memory.

The C/C++ language *may* be used in low-level embedded systems programming but not where "fine controls" or "high speeds" are required. The blanket statement that a "C compiler can produce code that is nearly as good as an assembly language program" is OK for traditional programs, high-level ESP, and medium-level ESP. It is *not true* for low-level ESP! Low-level ESP is special and has very exacting demands on its code. (This fact will be explained in detail in Chapter 6.)

The overall scope of this book is to show the reader how to program the PIC, use its peripheral functions, and provide the fundamentals of general ESP techniques.

The plan of this book is as follows:

Chapter 2 introduces microcontrollers in general and details the basic structure of the PIC16F877.

Chapter 3 introduces the most fundamental elements of programming the PIC in assembly language using a simple circuit and program. Several instructions are introduced here. (Chapter 3 is the "Hello World" Chapter.)

Chapter 4 covers the first half of the PIC instruction set by considering the design of a very simple home security system. This method illustrates not only what the instructions are but, also, how to use them in a practical way.

Chapter 5 covers the rest of the PIC instruction set in the same way as in Chapter 4 with a more advanced security system design which includes a keypad and a digit display interface.

Chapter 6 covers the fundamentals of general ESP and shows the reader the style, technique and art of ESP. These techniques and ideas apply to all processors and are the main-stay of all of low-end embedded systems programming. Examples of coding and programs are given in the PIC assembly language.

Chapter 7 covers more advanced ESP techniques, such as sine-wave generation, DTMF signaling, data compression, pulse-width modulation, and testing techniques.

Chapter 8 covers the PIC peripherals with complete examples of how to use them. These include counters, timers, interrupts, the analog-to-digital converter, the pulse-width modulators, measurement hardware, and event generation hardware.

Chapter 9 covers the PIC peripherals for serial data communications. These are the USART, a shift-register interface, and the "Inter-Integrated Circuit" serial interface.

Chapter 10 is an introduction to the fundamentals of Digital Signal Processing (DSP) in an intuitive way and with detailed examples. Filter designs and programs are given in a cookbook fashion. Some advanced and exotic DSP applications and techniques are given.

Appendix A is a detailed view of the PIC instruction set.

Appendix B is a set of useful C++ programs which help the reader design projects for the PIC.

Appendix C is a list of special-function registers and their bit-settings.

Appendix D is a register-file map.

Appendix E shows the PIC16F877 external pins and their functions.

Appendix F shows the sequence of instructions to save registers and restore them when doing a processor interrupt.

## 2.0 Chapter Summary

Section 2.1 covers the types of memories used in the general sense and their organization with respect to the data and addressing. Section 2.2 discusses the memories used in the PIC. Section 2.3 introduces the most fundamental elements of programming at the assembly language level.

### 2.1 Memory and Memory Organization

A microcontroller is a complete computer system on a single chip. It is more than just a microprocessor: It also contains a Read-Only Memory (ROM), a Read-Write Memory (RAM), some input/output ports, and some peripherals, such as, counters/timers, analog-to-digital converters, digital-to-analog converters, and serial communication ports.

The internal view of a typical microprocessor is shown in Figure 2-1 and is composed of three things: an arithmetic/logic unit (ALU) which performs calculations on data; a set of registers which hold the user's data and the system's data; and a control unit which orchestrates everything and interprets and executes the user's instructions. As far as the microprocessor is concerned, it assumes that there are sets of data memories and program memories (RAM and ROM) in the system. The only thing the microprocessor has to do is run a cycle of getting new instructions and executing them from the memories.

Both the RAM and the ROM are organized as indexed sets of data words, where each "index" is the "address" of its corresponding data. Both the data and its address codes are numbers represented in binary or hexadecimal.

The RAM is a read-write memory which can rapidly read and write the data. It is a volatile memory which means that it loses its memory when power is removed (turned off). The ROM is for program memory and is "read-only" except in modern variants, such as Electrically Erasable Programmable Read Only Memory (EEPROM) and Flash Memory, which allow data words to be written as well as read. The writing of an EEPROM is not the same as a RAM since the data-writing time of the EEPROM is about ten thousand times as long as the data-writing time of the RAM. The ROM and its variants are non-volatile memories that preserve their memories when the power is removed (turned off).

## 2.2 The PIC16F877

The PIC16F877's internal block diagram is shown in Figure 2-2. The PIC contains an ALU, which does arithmetic and logic operations, the RAM, which is also called the "register-file", the program EEPROM (Flash Memory), the data EEPROM, and the "W" register. The "W" register is not a part of the register-file but is a stand-alone, working register (also called an "accumulator").

The ALU, the RAM, the "W" register, and the data EEPROM each manipulate and hold 8-bit-wide data, which ranges in value from zero to 255 (or, in hexadecimal, from 0x00 to 0xFF).

The program EEPROM (Flash Memory) works with 14-bit-wide words and contains each of the user's instructions.

It is not uncommon for microcontrollers to have different sizes of data memory and program memory (in the PIC: 8-bits for data and 14-bits for program words). More than that, the key is that the data and program memories occupy separate spaces. This allows access to each at the same time.

The PIC's RAM addresses range from zero to 511 but the user can only access a RAM byte in a set of four "banks" of 128 bytes each and only one bank at a time. Not all of this RAM is available to the user as read-write memory, however. Many addresses are dedicated to special functions within the processor but they "look-like" RAM and are accessed the same way.

The PIC's program EEPROM (Flash Memory) has addresses that range from zero to 8191 (0x1FFF). The user's program occupies this memory space.

### 2.3 Programming The PIC

All types of computer programs can be broken-down into four main sets of actions:

- 1) Top-Down Execution

- 2) Conditional Branching

- 3) Loops

- 4) Subroutine Calls

Programming the PIC in assembly language is no exception but it is more difficult to work with than high-level languages, like BASIC and C++.

Assembly language uses a one-to-one correspondence of mnemonic words with the binary machine codes that the processor uses to code the instructions. The user writes the program using the mnemonic words called the "source" program and gives this to the program on the PC called the "assembler" which converts it into the machine code of the PIC in the form of a list of hexadecimal numbers. This set of numbers is called the "object" program. The user then writes the object program into the PIC in the downloading process of programming the PIC. When this is done, the PIC is ready to run its new program.

Understanding how to code a program in assembly language is contingent upon understanding how the PIC works at the machine level.

The PIC executes instructions from program memory in sequential addresses, starting from address zero, when the PIC is reset upon power-up. The address of the current instruction being executed is given in a special register called, the "program-counter" (PC). The PIC's control unit automatically increments the program-counter (PC), gets the next instruction, decodes that instruction, and then executes it. If this is done on sequential addresses, this is called, "top-down" execution. There are also ways to do non-sequential-address executions. This is done with special instructions which load new addresses into the program-counter. This is how conditional-branching, loops, and subroutines are done at the machine language level.

Each line of source program code in assembly language has up to four parts: A label, an op-code, an operand, and a comment. This is shown as follows:

## LABEL: OPCODE OPERAND(S) ; COMMENT

The label is an arbitrary name the user picks to mark a program address, a RAM address, or a constant value. If the label has its first character (a letter) that starts in column one of the text, the colon is optional. Otherwise, the colon separates the label from the "Op-Code". The "Op-Code" is short for, "Operation-Code", and is the mnemonic name for the instruction to be executed. The operand or operands are the data or the address that the instruction uses when it is to be executed. This is where labels come into play such as when an instruction needs a new address. Comments are optional and must begin with a semi-colon. Comments are for documenting the source program so that it will be easy to read and understand. For example, the following lines are valid source program code lines:

LOOP:BSFFLAGS,2; Set Alarm Flag BitMAIN:CALLSORT\_SUB; Sort the Data

DECFSZ TEMP,F

; This is an example of a line which consists of only a comment

MAIN CALL SORT\_SUB ; Sort the Data (No Colon in Label)

# <u>Chapter 3: Simple PIC Hardware</u> <u>& Software ("Hello World")</u>

#### 3.0 Chapter Summary

Section 3.1 introduces a simple PIC system and analyzes its controlling program. It looks at each instruction, examines its structure and coding, and sets a foundation for proper usage of assembly language. Section 3.2 summarizes the instructions and concepts covered in Section 3.1.

## 3.1 A Simple Example System

An external view of the PIC with its pins is shown in Figure 3-1. This is the most basic view of the PIC's functions. Most pins have a second use, or, even a third use: to run the PIC's peripherals, such as the ADC, the timers, and the serial ports, to name a few. These other functions will be shown later as they are needed.

The basic function of these pins is for digital inputs and digital outputs. The individual bits on each of the input/output ports (A-through-E) can each be selected as "input" or "output" by special configuration registers in the RAM. The software must set these bits before the ports can be used. This will be shown in more detail shortly.

An example circuit which uses the input/output (I/O) ports "B" and "C" is shown in Figure 3-2. This is a simple, bare minimum, PIC example circuit that serves to introduce some simple software and instructions. Port "B" has a set of 8 DIP switches with resistor pull-ups on it to allow data from these switches to be read into the PIC. Port "C" drives a set of 8 LEDs through resistors to allow the PIC to send out and display its data. The power supply must drive both sets of power pins as shown in Figure 3-2. The clock input, OSC1, is driven by an external oscillator module as shown. Also, a 10K Ohm pull-up resistor is used on Pin 1 (/MCLR) to keep the PIC out of its "Reset" state.

The following program can be used to run the circuit of Figure 3-2:

| LIST P = 16<br>INCLUDE "P | -                             |                                     |

|---------------------------|-------------------------------|-------------------------------------|

| ORG<br>NOP                | 0x0000                        | ; Program starts at address zero.   |

| BANKSEL<br>MOVLW<br>MOVWF | PORTC<br>B'00000000'<br>PORTC | ; Select Bank Zero<br>; Reset PORTC |

|      | BANKSEL | TRISC       | ; Select Bank One                   |

|------|---------|-------------|-------------------------------------|

|      | MOVLW   | B'0000000'  | ; Make PORTC All Outputs            |

|      | MOVWF   | TRISC       |                                     |

|      | MOVLW   | B'11111111' | ; Make PORTB All Inputs             |

|      | MOVWF   | TRISB       |                                     |

|      | BANKSEL | PORTC       | ; Select Bank Zero                  |

| MAIN | :       |             |                                     |

|      | MOVF    | PORTB,W     | ; Read DIP Switches into W-Register |

|      | MOVWF   | PORTC       | ; Write W-Register to LEDs          |

|      | GOTO    | MAIN        | ; Loop To Address "MAIN"            |

|      | END     |             |                                     |

After setting up Port "C" as an "output" and Port "B" as an "input", this program reads the value of the switches on Port "B" and sends it back out to the LEDs on Port "C" in a continuous loop. This may seem like a very trivial program but it is still useful as a test and a simple demonstration of the PIC.

This program is an example of an assembly language program. The MPLAB assembler on the IBM-PC takes this ASCII coded text and converts it into machine code for the PIC to use.

The major part of this program uses the I/O ports and their configuration registers and we can now look at the RAM or register-file bytes in extensive detail. Appendix D shows the addresses and names of the registers and RAM bytes used by the PIC.

The RAM or Register-File is divided into four banks of 128 bytes each. Only one bank can be used at a time. Not all of the bytes in a bank can be used as user memory because some bytes have special purposes, such as I/O ports. However, all of these bytes work like RAM: They can be read from, and written to, just like a memory byte.

Each register-file byte has a unique address within its bank which ranges from zero to 127 (0x00 to 0x7F). The register, PORTC, for example, is located in Bank zero and has the address 0x07. Notice that some register-file bytes in Appendix D are repeated across each of the banks at the same corresponding addresses. For example, STATUS, PCL, FSR, PCLATH, and INTCON all occupy the same line addresses in each of the four banks. This is so that they can be accessed and have the same values contained in them independent of the bank which is currently selected. For the other registers which are not repeated, the proper bank must be selected before they can be used. For example, storing data in the register byte at address 0x30 in Bank Zero, changing the current bank to Bank One, and then trying to read the right data in the register byte at address 0x30 will not give the same data that was stored even though the addresses were both 0x30. Bank Zero must be selected again as the current bank to get

the right data. However, the RAM addresses from 0x70 through 0x7F can be used in any bank to reference the same data *without* switching banks. This is a very valuable feature!

The usage of the register files will be made more clear as we analyze the program and consider how the instructions are coded and used.

The program starts with the statements, "LIST" and "INCLUDE". These are not instructions in that they are not translated into machine code. They are "assembler directives" which tell the assembler (MPLAB) where to get information about the PIC chip being used (PIC16F877). All of your programs must start with these statements, in this order, as shown.

The statement, "ORG 0x0000", is an assembler directive which tells the assembler at what address the following instructions will start. Here they will start at address zero where "0x0000" indicates "hexadecimal zero".

The next statement is the "NOP" instruction. It is a true instruction that gets translated into machine code. "NOP" stands for "No Operation" (it does nothing). It is coded as 14 zero bits, or, 0x0000 in hexadecimal. Remember that all of the instructions are each 14 bits long.

The next statement is "BANKSEL PORTC". This is not a true instruction, per se, but it does get translated into two machine instructions which select the current register file bank to be used. Here, "PORTC" is interpreted as "Bank Zero". Later "BANKSEL TRISC" will be interpreted as "Bank One". In general, the operand of BANKSEL will select the lowest bank number where the operand name is found in Appendix D.

The next statement is the "MOVLW" instruction which means "move the literal value that follows into the W register". Remember that the W register is not a part of the RAM but is an "accumulator" or "working register" within the PIC. The instruction:

MOVLW B'0000000'

Says, "move the binary value of all zeros to W". The general machine coding of the "MOVLW" instruction is:

11 0000 kkkk kkkk

where the "k"s are the single binary bits of the literal data (the data byte). The instruction:

MOVLW B'0000000'

Would be coded as:

11 0000 0000 0000 or 0x3000.

Later in the program is the instruction

MOVLW B'11111111'

Which is coded as:

11 0000 1111 1111 or 0x30FF.

The next instruction is, "MOVWF PORTC", which means, "move the value in the W register to the register-file byte at the address given (address given here is PORTC)". That is, "Move W to RAM". In general, this is coded as:

00 0000 1fff ffff

where the "f"s are the binary bits of the address for the desired register-file byte. Since Port C has the address 0x07 the coding of "MOVWF PORTC" would be:

00 0000 1000 0111 or 0x0087.

It would be perfectly legal in the assembly language program to say, "MOVWF 7" to mean, "MOVWF PORTC" and it would be translated in exactly the same way. However, it would be very confusing to anyone who tried to read the program and, for this reason, it is better to let the assembler keep track of the register-file names and let the assembler translate them to the proper addresses. In general, it is best to let the assembler translate all of the label names (RAM or ROM) in the program to their values. Never use translated numbers directly in the ASCII text of the program. Always use label names. This is a very good programming practice.

At the bottom of the program there is the label, "MAIN", and the instruction, "MOVF PORTB,W". The label "MAIN" is there to mark the address of the "MOVF" instruction so that we can come back to that address. The "MOVF" instruction stands for, "move the register-file byte value to the W register". Specifically, it moves the value in Port B to the W register. (It is also possible to say, "MOVF PORTB,F", which would mean, "move the value in Port B to Port B". This sounds absurd but there is a reason that this is allowed.)

The next new instruction is the, "GOTO MAIN", which means, "put the addressvalue at MAIN into the program-counter to transfer to that address". This causes a "loop" to occur in the program. The instruction at the address "MAIN" is the "MOVF". The last statement is the, "END", which is an assembler directive that means, "end the program".

Now that the program directives and instructions are understood, we can come to a better understanding of how the program works.

The first step in the program is to send zeros to Port C in preparation for setting up Port C to be an output port. This may seem backwards (sending data to a port before it is declared to be an output port) but there is a good reason for it: When the declaration is made as "output", whatever data that is in the port output buffer is immediately sent out. If there is garbage in the port output buffer, that garbage will be the first output from the port. This is why zeros were sent to the port first.

The next steps are to declare Port C and Port B to be as "output" and "input", respectively, by using the TRISC and TRISB registers. If a "1" is sent to a TRISC bit, the corresponding Port C bit will be an "input". If a "0" is sent, the Port C bit will be an "output". This rule applies to all of the ports (A, B, C, D, and E) and their corresponding TRIS registers. (Ports "A" and "E" need additional configurations, however.)

In the "MAIN" loop, the data from the DIP switches on Port B is moved to the W register as an intermediary and is then moved to Port C to display the data on the LEDs. Then the "GOTO" closes the loop to form an infinite loop.

The thing for you to do now is to enter this program in an ASCII text editor and run a simulation of it in the MPLAB. See if you can enter and run this program.

## 3.2 Summary of Instructions and Concepts

- 1) When you are using MPLAB, your programs must start with: LIST P=16F877 INCLUDE "P16F877.INC"

- 2) The register-file map in Appendix D shows where each special function register-file is and which RAM banks restrict its use.

- 3) RAM addresses from 0x70 through 0x7F may be freely used by the user and are accessible as the "same" data in any bank.

- 4) The "ORG" assembler directive tells the program where the current program memory address is. Use, "ORG 0xhex-number".

- 5) The "NOP" instruction means "No Operation". It does take time for the PIC to run it, however.

- 6) The "BANKSEL" directive selects the RAM bank for the current use. Consult Appendix D to get the right RAM bank.

- 7) The "MOVLW" instruction means "Move the Literal value that follows into the W register".

- 8) The "MOVWF" instruction means "Move the W register's data into RAM". The data in the W register remains unchanged after doing this instruction.

- 9) The "MOVF" instruction means "Move data from the RAM into the W register".

- 10) The "GOTO" instruction "Loads the Program Counter with the address (label) that follows" to "Jump" to a new, non-sequential address in program memory.

- 11) Labels are used to reference addresses in program memory so that "GOTO" instructions can use them.

- 12) The "END" directive is the last line of any program and is used to signal the end of the assembly process.

- 13) Always use label-names to reference RAM or program memory.

- 14) Send zeros to a port before you declare the port as "output" so that garbage will not initially corrupt the port's output.

- 15) Use the appropriate "TRISx" register to declare a port as "input" or "output".

## Chapter 4: The PIC Instruction Set (Part I)

#### 4.0 Chapter Summary

Section 4.1 covers the PIC instruction set by building a simple security system. It covers the RAM and ROM in more detail, looks at instruction timing, and introduces the use of subroutines. Section 4.2 summarizes the instructions and concepts.

#### 4.1 The PIC16F877 Instruction Set

The PIC16F877 only has 35 instructions and it would be easy to list them all at once. It would, then, be harder to explain them and give examples of how they are used. A much more natural way is to pick a specific application for the PIC then illustrate the instruction set, show how the instructions are used, and show how a program uses sequences of instructions to accomplish the desired tasks.

Let's consider the design of a home security system or a burglar alarm using the PIC. A simple security system circuit is shown in Figure 4-1. The main alarm sensor that is used in this system is the magnetic reed switch. Figure 4-1 shows five of these in series, tied to ground, and connected with a pull-up to the PIC input port pin. Suppose that Port B is configured as an input port and that this line connects to RB0 (bit zero). The magnetic reed switch has two parts: The switch, itself, which is mounted to a door frame or a window frame, and a magnet, which is mounted to the door or the window. When the door or the window is closed, the magnetic field is broken and the reed switch turns "OFF" or "open". This is the mechanism that trips the alarm.

The software segment that would sense an alarm is:

| ALARM_TEST: |            |

|-------------|------------|

| BTFSS       | PORTB,0    |

| GOTO        | ALARM_TEST |

Where "BTFSS" means, "Bit-Test-File-Skip-if-Set". That is, if Port B, bit zero (RB0) is sensed as a "one" ("set"), the next instruction will be skipped. When each reed switch is closed, the Port B, bit zero line will read as "zero" since it is tied to ground. When any reed switch is opened, the Port B, bit zero line will be pulled high ("one") and this will be the alarm condition.

The general format for the "BTFSS" instruction is:

BTFSS Register-File,Bit-Number

Where the bit-number selects one of eight (8) bits as 0-through-7. There is also a "BTFSC" instruction that is identical to "BTFSS" except that it skips when the tested bit is "Clear" ("zero").

When the alarm condition is sensed, the alarm will be activated by setting Port C, bit one (RC1) to a "one" ("1") as:

BSF PORTC,1

Which means, "Bit-Set-File". This will turn the transistor "ON", turn the relay "ON", and the relay contacts will switch on the alarm. The alarm can be reset with:

BCF PORTC,1

Which means, "Bit-Clear-File". Both "BSF" and "BCF" specify one of eight (8) bits as 0-through-7 for any RAM byte or register-file.

The alarm circuit has two other hardware elements that need to be controlled. One is an "Arm/Disarm" switch input on Port B, bit one (RB1) and the other is a "Ready-To-Arm" LED on Port C, bit zero (RC0).

The software that would control this system is as follows:

LIST P=16F877 INCLUDE "P16F877.INC"

| REED<br>ARM:<br>LED:<br>ALAR |                      | EQU<br>EQU<br>EQU<br>EQU                                | 1 ; Arm/DisArm Switch is PORTB, Bit One                                   |                                 |

|------------------------------|----------------------|---------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|

|                              | ORG<br>NOP           |                                                         | 0X00                                                                      | 00                              |

|                              | BANK<br>MOVI<br>MOVI | WF                                                      | PORT<br>0X00<br>PORT                                                      | ; Before Set-Up                 |

|                              | MOVI<br>MOV          | WF                                                      | TRISE<br>0XFF<br>TRISE                                                    | ; Port B is to be Input         |

|                              | MOVI<br>MOV<br>BANK  |                                                         | 0X00<br>TRIS(<br>PORT                                                     | , 1                             |

| MAIN                         | :                    |                                                         |                                                                           |                                 |

| BTFSS<br>GOTO<br>RESET:      |                      | PORTB,REED; Test Reed Switches, Skip if "Open"<br>READY |                                                                           |                                 |

| NL OL                        | BCF<br>BCF<br>GOT(   | C                                                       | PORTC,LED ; Reset "Ready-To-Arm" LED<br>PORTC,ALARM ; Reset Alarm<br>MAIN |                                 |

| READ                         | )Y:<br>BSF           |                                                         |                                                                           | ГС,LED ; Set "Ready-To-Arm" LED |

|                              | BTFS                 |                                                         | PORTB,ARM; Test "Arm/DisArm" Switch, Skip if Set<br>MAIN                  |                                 |

| ALAR                         | M_SE<br>BTFS         |                                                         | PORTB,REED; Test Reed Switches, Skip if "Set"<br>; (Alarm)                |                                 |

|                              | GOT                  | C                                                       | ALAR                                                                      | M_SENSE                         |

|                              | BTFS                 | S                                                       | PORTB,ARM; Test "Arm/DisArm" Switch, Skip if Set                          |                                 |

| GOTO       | MAIN                                |

|------------|-------------------------------------|

| SET_ALARM: |                                     |

| BSF        | PORTC,ALARM ; Activate Alarm        |

| BTFSC      | PORTB,ARM; Test "Arm/DisArm" Switch |

| GOTO       | SET ALARM; Still Set, Stay in Alarm |

| GOTO       | RESET ; Not Set, Reset Alarm        |

| END        |                                     |

This program uses a new assembler directive called, "EQU", or "Equate" to define constants, such as bit positions and data, as label names. Its usage is:

Label: EQU "data"

It is good programming practice to use EQUs to make programs more readable.

This alarm system program is fine if the "Arm/DisArm" switch and the "Ready-To-Arm" LED are located on the outside of the house. If they are located on the inside of the house, this program has a serious problem: It is impossible to leave the house after the system is armed since the alarm will be tripped when the door is opened!

This problem is usually solved by adding a delay of thirty (30) seconds before activating the alarm so that the user can leave the house and not trip the alarm. An external timer could be attached to the PIC to provide this delay but the better solution is to let the PIC generate its own delays in software.

The PIC runs with a clock frequency of 4 MHz and this controls instruction execution speed. The instruction execution speed is one-fourth of the clock frequency. Each instruction executes in one or two instruction cycles, or, in one or two microseconds. Each instruction that "skips", such as, "BTFSS", executes in two instruction cycles when it "skips" and one instruction cycle when it doesn't. The "GOTO" instruction always executes in two instruction cycles.

Let's see how to build a 30-second software delay. The first step is to build a one-millisecond delay as follows:

| D'250'   | ; Load W with Decimal 250 |

|----------|---------------------------|

| TIME     | ; Initialize RAM "TIME"   |

|          |                           |

|          | ; (1) Cycle               |

| TIME,F   | ; (1) Cycle               |

| LOOP_ONE | _MS ;(2) Cycles           |

|          | TIME<br>TIME,F            |

This program segment uses the "DECFSZ" instruction, which means, "Decrement-File-Skip-if-Zero". When the Byte's data is decremented, it may be stored back in the RAM or it may be stored in the W register. Specify the RAM as the destination with the "F" or specify the W register with the "W". This instruction decrements the RAM byte ("TIME", in this case) and skips the next instruction if the result was zero. The initial value of "TIME" is 250 and the loop has a length of four instruction cycles. As the loop counts down from 250 each count adds four microseconds of delay which, when multiplied by 250, gives a total time of about one millisecond.

A loop can then be formed around this loop that counts down from 250 to give a delay of 250 milliseconds. Then another loop can be placed around it that counts down from 120 to give a total delay of 30 seconds!

(There is also an "INCFSZ" instruction which increments a register-file and skips the next instruction if the result is zero. Either "INCFSZ file,F" or "INCFSZ file,W".)

The total nested-loop structure for a 30-second delay is:

| MOVLW<br>MOVWF | D'120'<br>TIME2 | ; Count 120 of 250 millisecond delays |

|----------------|-----------------|---------------------------------------|

| LOOP_30_SEC:   |                 |                                       |

| MOVLW          | D'250'          | ; Count 250 of one millisecond delays |

| MOVWF          | TIME1           |                                       |

| LOOP_250_MS:   |                 |                                       |

| MOVLW          | D'250'          | ; Count of 250 Loops of four cycles   |

| MOVWF          | TIME            |                                       |

| LOOP_ONE_MS:   |                 |                                       |

| NOP            |                 |                                       |

| DECFSZ         | TIME,F          |                                       |

| GOTO           | LOOP_ONE_MS     |                                       |

|                |                 |                                       |

| DECFSZ         | TIME1,F         |                                       |

| GOTO           | LOOP_250_MS     |                                       |

|                |                 |                                       |

| DECFSZ         | TIME2,F         |                                       |

| GOTO           | LOOP_30_8       | SEC                                   |

This code must be put into two places in the alarm software: Once just before the "ALARM\_SENSE" loop and once just after it. This will allow the user 30 seconds to enter and leave before the alarm goes off.

This is a lot of code to make two copies of and insert into a relatively simple software loop. The resulting code would be much more complicated, much more difficult to follow, and the probability of making a mistake would be much higher. Are there any easier alternatives?

There are. The solution is to use subroutines with the "CALL" and "RETURN" instructions. The "CALL" instruction works just like a "GOTO" instruction except that

the PIC automatically saves the address of the next instruction after the "CALL" in a special memory. This action is automatic and invisible to the user. When you are finished with the subroutine, you use the "RETURN" instruction to tell the PIC to go back to the part of the program where you left off. That is, to get the address out of the special memory and "GOTO" it automatically. The "CALL" and "RETURN" instructions each take two instruction cycles to execute.

For example, the one-millisecond delay can be accomplished with the following subroutine:

DELAY\_ONE\_MS: MOVLW D'250' ; Count 250 Loops MOVWF TIME LOOP\_ONE\_MS: NOP ; Four Cycle Loop DECFSZ TIME,F GOTO LOOP\_ONE\_MS RETURN

This would give a delay of one millisecond each time it was called, as follows:

CALL DELAY\_ONE\_MS

We could also make a 250-millisecond delay subroutine as follows:

| DELAY_250_MS: |              |                          |  |

|---------------|--------------|--------------------------|--|

| MOVLW         | D'250'       | ; Count 250 Milliseconds |  |

| MOVWF         | TIME1        |                          |  |

| LOOP_250_MS:  |              |                          |  |

| CALL          | DELAY_ONE_MS |                          |  |

| DECFSZ        | TIME1,F      |                          |  |

| GOTO          | LOOP_250_    | MS                       |  |

| RETURN        |              |                          |  |

Notice that this subroutine calls the "one-millisecond" subroutine 250 times. There is no law that says you can't have one subroutine that calls another subroutine – you can – it's called "nesting" subroutines. The PIC allows you to nest subroutines up to only eight (8) levels, however.

The 30-second delay can then be formed as the following subroutine:

| DELAY_30_SEC: |        |                                |

|---------------|--------|--------------------------------|

| MOVLW         | D'120' | ; Count 120 of 250-Millisecods |

| MOVWF         | TIME2  |                                |

| LOOP_30_SEC:  |        |                                |

CALL DELAY\_250\_MS DECFSZ TIME2,F GOTO LOOP\_30\_SEC RETURN

## 4.2 Summary of Instructions and Concepts

- 1) Subroutines may be nested up to eight (8) levels deep.

- 2) Each instruction takes either one or two instruction-cycles to run.

- Each instruction-cycle time runs in the period of the PIC's oscillator frequency, Fosc, divided by four (4). If Fosc = 4 MHz, each instruction-cycle will run in one microsecond.

- 4) The "EQU" directive is used to make user-defined labels for RAM addresses, constants, and bit-positions.

- 5) The "GOTO", "CALL", and "RETURN" instructions each take two instruction-cycles to run. Also, anytime an instruction "skips" it takes two instruction-cycles to run.

- 6) New Instructions Covered:

| BTFSS | file,bit |

|-------|----------|

| BTFSC | file,bit |

| BSF   | file,bit |

| BCF   | file,bit |

DECFSZ file,destination INCFSZ file,destination CALL address RETURN

## Chapter 5: The PIC Instruction Set (Part II)

### 5.0 Chapter Summary

Section 5.1 discusses the need for a more advanced security system. Section 5.2 introduces the keypad and display interfaces. Section 5.3 introduces the processor status flags. Section 5.4 details the keypad software. Section 5.5 details the LED digit display software. Section 5.6 explains indirect RAM addressing. Section 5.7 covers more advanced general features of the PIC processor. Section 5.8 shows how the keypad and the display software work in harmony with each other. Section 5.9 is a last look at the security system. Section 5.10 summarizes the instructions and concepts of Chapter 5.

#### 5.1 Introduction

The basic PIC instructions were introduced in Chapter 4 with an example of a simple security system. In a similar way, the remaining instructions will be introduced with an example of a more complex security system.

A more complex system is needed for a large house or an industrial user. If there are many rooms, doors, and windows, a single "Ready-To-Arm" LED is not enough to give the location of the "insecure" site when the user desires to set the alarm. Also, a single "Arm/DisArm" switch presents no difficulty to a thief who knows where the switch is and wants to disable the alarm. The security system should also offer the user a, "Home/Away" setting so that a remnant of the system can still work while the user is at home (i.e., when he or she is asleep or wants to use the bathroom without triggering the alarm).

These problems could be solved by having many "Ready-To-Arm" LEDs and many "Arm/DisArm" switches but this is not practical when flexible and compact software is available. The solution is to use a twelve-key keypad and a set of seven-segment LED digits to get and display more complex information to run the security system. For example, the LED digits could display a message like, "Zone 3 Not Ready To Arm", or, "Office 407 Not Ready". These messages could be static, or constantly displayed, or they could repeatedly scroll across the display over a few seconds. Code numbers could be entered on the keypad to set-up and run the system. An "Arm/DisArm" switch is not a problem for a would-be thief but entering a four-digit security-code that could be changed daily is much more formidable!

Before we can introduce more instructions and show the software that could do these things, we need to show how the keypad and the LED digits are interfaced to the PIC.

## 5.2 Keypad And Display Interface

A twelve-key keypad usually consists of a matrix of twelve switches, as shown in Figure 5-1. Three lines connect the columns while four lines connect the rows. When a key is pressed, one column and one row are connected. The PIC must use its software to scan each column-line and look for a row-line that is connected, if, and when, a switch is pressed. The PIC keypad interface circuit is shown in Figure 5-2.

A typical seven-segment LED digit is shown in Figure 5-3. The digit consists of eight (8) LEDs: Seven for the segments and one for the decimal point. The LEDs are connected together in a "common-anode" or a "common-cathode" form. If only one digit is to be used, the common-cathode is tied to ground or the common-anode is tied to five volts, and the PIC would drive each segment LED through a 470 Ohm resistor, as shown in Figure 5-4. If more than one digit is to be used, the digits are usually multiplexed, as shown in Figure 5-5. Multiplexing digits is a way of saving PIC output port lines by time-sharing them. Let's see how this works.

For digit multiplexing, the corresponding segments of each digit are wired together in parallel, as shown in Figure 5-5. Each common-anode or common-cathode of a single digit is driven by a transistor. The idea is to turn on one transistor at a time and supply that digit's segments for a few milliseconds at a time and then turn it off. Then repeat this for each transistor and digit's segments for the whole display, over and over. The overall effect on the human eye is that all of the digits appear to be "on" at the same time! Each digit gets the right information and there is no blurring or garbage.

# 5.3 The STATUS Register and Flag Bits

We are almost ready to begin a full discussion of how the keypad and the LED digits are run in software. First, is should be noted that the instructions that are needed to do this affect flag bits in the status register. Three flag bits are affected automatically as a result of doing each of these instructions.

The STATUS register is shown in Appendix C. The bits RP1 and RP0 are set by the user to select one of the four banks of the RAM registers. This can be done with the BCF and BSF instructions or with the BANKSEL directive. The BANKSEL directive produces the right combinations of BCF and BSF instructions for the STATUS register to select the appropriate RAM bank.

The three flag bits that interest us most are the "Z", the "DC", and the "C" bits. The "Z" bit is set if the instruction produces a result of zero. The "C" bit is the "carry" bit and shows the carry-out of the seventh bit of the result (The result bits range from zero-through-seven). The "DC" bit shows the "carry-out" of the third bit of the result (this is used for binary-coded-decimal arithmetic). A complete list of which instructions affect the flag bits, and how, can be found in Appendix A. The "MOVF f,d" instruction is the only instruction that we have seen so far (Chapter 3) that affects a flag bit. Specifically, it only affects the "Z" bit, showing if the value or data that is moved is zero (Z = 1) or not (Z = 0).

We are now ready to write the software to control the keypad and the LED digits.

# 5.4 The Keypad Software

Look again at Figure 5-2. The row lines are pulled-up to five volts (Logic "1") and are connected through the key-switches to the column lines. The idea is to set the column lines low (Logic "0"), one-at-a-time, and search for a low (Logic "0") on the row lines. If a row line is low, a key has been pressed, and the scanning software subroutine returns a number code corresponding to the key. If no key is pressed, the routine returns a code of zero.

The scanning subroutine is as follows:

| KEY_SCAN:<br>BCF<br>BSF<br>BSF                                       | PORTD,4<br>PORTD,5<br>PORTD,6                                 | -                                                               |

|----------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|

| BTFSS<br>RETLW<br>BTFSS<br>RETLW<br>BTFSS<br>RETLW<br>BTFSS<br>RETLW | PORTD,0<br>1<br>PORTD,1<br>4<br>PORTD,2<br>7<br>PORTD,3<br>10 | ; Key = "1"<br>; Row 2<br>; Key = "4"                           |

| BSF<br>BCF                                                           | PORTD,4<br>PORTD,5                                            | ; Column 2 = LOW                                                |

| BTFSS<br>RETLW<br>BTFSS<br>RETLW<br>BTFSS<br>RETLW<br>BTFSS<br>RETLW | PORTD,0<br>2<br>PORTD,1<br>5<br>PORTD,2<br>8<br>PORTD,3<br>11 | ; Key = "2"<br>; Row 2<br>; Key = "5"<br>; Row 3<br>; Key = "8" |

| BSF<br>BCF                                                           | PORTD,5<br>PORTD,6                                            | ; Column 3 = LOW                                                |

| BTFSS | PORTD,0 | ; Row 1          |

|-------|---------|------------------|

| RETLW | 3       | ; Key = "3"      |

| BTFSS | PORTD,1 | ; Row 2          |

| RETLW | 6       | ; Key = "6"      |

| BTFSS | PORTD,2 | ; Row 3          |

| RETLW | 9       | ; Key = "9"      |

| BTFSS | PORTD,3 | ; Row 4          |

| RETLW | 12      | ; Key = "#"      |

| RETLW | 0       | ; No Key Pressed |

The new instruction used in this subroutine is "RETLW k", which means, "Return from subroutine with the W register containing the eight-bit value, k". Thus, when KEY\_SCAN returns, the key-code will be in the W register. The "RETLW" instruction runs in two instruction cycles.

The KEY\_SCAN routine can be improved by eliminating the repeated code to scan the rows and replacing them with subroutine calls to a "ROW\_SCAN" routine. Notice that each of the row scans in KEY\_SCAN return values as:

(1,4,7,10) (2,5,8,11) and (3,6,9,12).

These are additions of zero, one, and two on the base values of (1,4,7,10). Assume that the ROW\_SCAN routine will also return a zero if no keys are pressed. The improved KEY SCAN routine is as follows:

| KEY_ | SCAN:<br>BCF<br>BSF<br>BSF       | PORTD,4<br>PORTD,5<br>PORTD,6          | ; Column 1 = LOW<br>; Others = HIGH                             |

|------|----------------------------------|----------------------------------------|-----------------------------------------------------------------|

|      | CALL<br>ADDLW<br>BTFSS<br>RETURN | ROW_SCAN<br>0<br>STATUS,Z              | ; (W) = Code<br>; Add Zero to Set Zero Flag<br>; (W) = 1,4,7,10 |

|      | BSF<br>BCF                       | PORTD,4<br>PORTD,5                     | ; Column 2 = LOW                                                |

|      | CALL<br>ADDLW<br>BTFSC<br>GOTO   | ROW_SCAN<br>0<br>STATUS,Z<br>KEY_SCAN2 | ; (W) = Code<br>; Add Zero to Set Zero Flag                     |

|      | ADDLW<br>RETURN                  | 1                                      | ; Adjust (W)<br>; (W) = 2,5,8,11                                |

| KEY_SCAN2:<br>BSF<br>BCF | PORTD,5<br>PORTD,6        | ; Column 3 = LOW                              |

|--------------------------|---------------------------|-----------------------------------------------|

| CALL<br>ADDLW<br>BTFSS   | ROW_SCAN<br>0<br>STATUS,Z | N ; (W) = Code<br>; Add Zero to Set Zero Flag |

| ADDLW<br>RETURN          | 2                         | ; Adjust (W)<br>; (W) = 3,6,9,12 OR (W) = 0   |

| ROW SCAN:                |                           |                                               |

| BTFSS                    | PORTD,0                   |                                               |

| RETLW                    | 1                         | ; Key "1"                                     |

| BTFSS                    | PORTD,1                   | 1.4 (( 4.1)                                   |

| RETLW<br>BTFSS           | 4<br>PORTD,2              | ; Key "4"                                     |

| RETLW                    | 7                         | ; Key "7"                                     |

| BTFSS                    | PORTD,3                   | , -,                                          |

| RETLW                    | 10                        | ; Key "*"                                     |

| RETLW                    | 0                         | ; No Key Found                                |

The new instruction used in the new KEY\_SCAN routine is, "ADDLW k", which means, "Add the W register and the eight-bit value, k, and put the result in the W register". The "ADDLW" instruction affects the "Z", "DC", and "C" status flag bits.

Addition can also be done between a RAM byte (register-file) and the W register with the "ADDWF f,d" instruction. This does, "W = (file) + W" or "(file) = (file) + W" and it also affects the "Z", "DC", and "C" status flag bits.

Using the "ADDLW" instruction it is possible to make more improvements in the KEY\_SCAN and ROW\_SCAN routines. In the original KEY\_SCAN each set of row value codes had a difference of three (i.e., From "1", "4" = "1" + 3, "7" = "4" + 3, ...). What if the ROW\_SCAN routine were called with the first row code in W and each time the key test failed, we add three to W? Also, the "Z" flag can be set within the ROW\_SCAN routine so we don't have to check it in the KEY\_SCAN routine. Can you write an improved version of the KEY\_SCAN and ROW\_SCAN routines using these techniques? Can you think of even more improvements?

# 5.5 The LED Display Software

Let's now look at the software controls for the four-digit, multiplexed, sevensegment display shown in Figure 5-5a. Port B of the PIC controls the segments while Port C, bits (0,1,2,3), control the digit-drives.

The display subroutine software is as follows:

| DISPLAY:<br>CLRF<br>CLRF<br>MOVF<br>MOVWF<br>BSF<br>CALL               | LEFT_DIGIT,W ; Get Left Digit's Segment Codes<br>PORTB ; Set-Up Segments for Activation                  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| CLRF<br>CLRF<br>MOVF<br>MOVWF<br>BSF<br>CALL                           | PORTB<br>LEFT_DIGIT2,W ; Get Left2's Segments<br>PORTB<br>PORTC,2                                        |

| CLRF<br>CLRF<br>MOVF<br>MOVWF<br>BSF<br>CALL                           | PORTB<br>LEFT_DIGIT3,W ; Get Left3's Segments<br>PORTB<br>PORTC,1                                        |

| CLRF<br>CLRF<br>MOVF<br>MOVWF<br>BSF<br>CALL<br>CLRF<br>CLRF<br>RETURN | PORTB<br>RIGHT_DIGIT,W ; Get Right-Digit's Segments<br>PORTB<br>PORTC,0<br>DELAY_5_MILLISECONDS<br>PORTC |

One new instruction used is, "CLRF f", which means, "Clear Register-File f". There is also, "CLRW", which means, "Clear W". Both of these set the "Z" (Zero) flag so that Z = 1. The "C" and "DC" flags are not affected. The "DISPLAY" routine must not have very much delay between calls, otherwise the digits will appear dim or flicker.

The use of the "DISPLAY" routine presupposes that the proper display codes are already in the digit RAM spaces (LEFT\_DIGIT, ..., RIGHT\_DIGIT). What are these display codes and how do we get them? Each display segment shown in Figure 5-3 corresponds to a bit position on Port B as:

| Segment | Port B Bit |

|---------|------------|

| ''a''   | 0          |

| "b"     | 1          |

| "c"     | 2          |

| "d"     | 3          |

| "e"     | 4          |

| "f"     | 5          |

| "g"     | 6          |

| "d.p."  | 7          |

If we were to make a table of base-ten digits to display and their display codes, it would look like:

| Digit | Display Code |

|-------|--------------|

| 0     | 0x3F         |

| 1     | 0x06         |

| 2     | 0x5B         |

| 3     | 0x4F         |

| 4     | 0x66         |

| 5     | 0x6D         |

| 6     | 0x7D         |

| 7     | 0x07         |

| 8     | 0x7F         |

| 9     | 0x6F         |

This table would be used, directly, by the following subroutine:

| GET_DISPLAY | CODE: |                                      |

|-------------|-------|--------------------------------------|

| ADDWF       | PCL,F | ; Add (W) to PCL, With Result in PCL |

| RETLW       | 0x3F  | ; "0"                                |

| RETLW       | 0x06  | ; "1"                                |

| RETLW       | 0x5B  | ; "2"                                |

| RETLW       | 0x4F  | ; "3"                                |

| RETLW       | 0x66  | ; "4"                                |

| RETLW       | 0x6D  | ; "5"                                |

| RETLW       | 0x7D  | ; "6"                                |

| RETLW       | 0x07  | ; "7"                                |

| RETLW       | 0x7F  | ; "8"                                |

RETLW 0x6F ; "9"

When this routine is called, the user puts the digit to find in the W register. The first instruction, "ADDWF PCL,F", adds the digit in W to the low-half of the programcounter, PCL, and puts the sum in PCL. In effect, this does a "GOTO"-like instruction and goes to the corresponding RETLW instruction where W is filled with the proper display code upon returning.

For example, suppose that W = 1 when "GET\_DISPLAY\_CODE" is called. When control is transferred to the "ADDWF PCL,F" instruction, the whole programcounter is incremented, automatically, to get to the next instruction, and then W is added to the low-half of the program-counter to point to the proper RETLW instruction. This is the, "RETLW 0x06", which has the display code for "1", and this code is in the W register when the subroutine returns.

Remember that the program counter is the register where the PIC keeps track of the address of the current instruction being executed. It is actually composed of two registers: A "high" half and a "low" half. This is because the PIC can address 8 K of program memory and it needs 13 bits to do this. These must be split into two 8-bit bytes. When the program counter is incremented, the low half is incremented first, and, if a carry is generated, it is automatically added to the high half. The low half is the register "PCL". The high half is not directly accessible but it can be set-up through the register "PCLATH" (We will see more of this later.)

Any table look-up routine, like "GET\_DISPLAY\_CODE", can be used with a number of entries up to or equal to 255. Some care must be taken, however, for *any* table, large or small. The "ADDWF PCL,F" instruction *only* adds to the *low-half* of the program-counter. There is *no* carry propagation to the high-half. If, for example, the "ADDWF PCL,F" instruction is located at the address 0x01FC and the table extends for ten entries, a value in W equal to four (4) will transfer control to the address 0x0100 and whatever is in that location will be treated as if it were an instruction (it may be) and the program will continue there! You *must* make sure, by using the "ORG" directive, to set an address that allows a large enough space to fit the table.

If the CALL to a table look-up routine is *not* within the same 256-byte address block as the table itself, the table's high-half address must be loaded into the PCLATH register before the CALL is made. For example,

| ORG   | 0x0100                |