# $\begin{array}{c} {\rm UNIVERSITY~OF~CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

The X-Legion A Compiler-Approach to Exploit Locality and Portability of Divide-And-Conquer Algorithms

### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in Information and Computer Science

by

Paolo Nicola D'Alberto

Dissertation Committee: Professor Alexandru Nicolau, Chair Professor Alexander Veidenbaum Professor Nikhil Dutt The dissertation of Paolo Nicola D'Alberto is approved and is acceptable in quality and form for publication on microfilm:

| _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _  | _ | _ | _   |     |    | _ | _ | _ | _ | _  | _  |

|---|---|---|---|---|---|---|---|---|---|---|----|---|---|-----|-----|----|---|---|---|---|----|----|

| _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _  | _ | _ |     |     |    | _ | _ | _ | _ | _  | _  |

|   |   |   |   |   |   |   |   |   |   |   |    |   |   |     |     |    |   |   |   |   |    |    |

| _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _  | _ | _ | _   |     |    | _ | _ | _ | _ | _  | _  |

| _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _  | - | _ | -   |     |    | _ | _ | _ | _ | _  | _  |

|   |   |   |   |   |   |   | ( | 7 | O | n | าา | m | i | t.t | 1.6 | 96 | į | ( | 7 | h | a. | iı |

University of California, Irvine 2005

#### Lame Deer, Seeker of Visions

John (Fire) Lame Deer and Richard Erdoes Medicine, Good and Bad, pag 162-163.

Even animals of the same kind - two deer, two owls - will behave differently from each other. Even your daughter's little pet hamsters, they all have their own ways. I have studied many plants. The leaves of one plant, on the same stem -none is exactly alike. On all the earth there is not one leaf that is exactly like another. The Great Spirit likes it that way. He only sketches out the path of life roughly for all the creatures on earth, shows them where to go, where to arrive at, but leaves them to find their own way to get there. He wants them to act independently according to their nature, to the urges in each of them.

[...]

I believe that being a medicine man, more than anything else, is a state of mind, a way of looking at and understanding this earth, a sense of what it is all about. Am I a wićaśa wakan? I guess so. What else can or would I be? Seeing me in my patched-up, faded shirt, with my down-at-the-heels cowboys boots, the hearing aid whistling in my ear, looking at the flimsy shack with its bad-smelling outhouse which I call my home - it all doesn't add up to a white man's idea of a holy man. You have seen me drunk and broke. You heard me curse or tell sexy jokes. You know I am not better and wiser than other men. But I've been up on the hilltop, got my vision and my power; the rest is just trimmings. That vision never leaves me - not in jail, not while I'm painting funny signs advertising some hash house, not when I am in a saloon, not while I am with a woman, especially not then.

# TABLE OF CONTENTS

| LI           | ST (                      | OF FIGURES                                               | ix   |  |  |  |  |  |  |  |  |  |  |

|--------------|---------------------------|----------------------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|

| LI           | ST (                      | OF TABLE                                                 | xi   |  |  |  |  |  |  |  |  |  |  |

| A            | CKN                       | IOWLEDGMENTS                                             | xiii |  |  |  |  |  |  |  |  |  |  |

| $\mathbf{C}$ | URR                       | ICULUM VITAE                                             | xv   |  |  |  |  |  |  |  |  |  |  |

| 1            | The                       | esis Statement and Contribution                          | 3    |  |  |  |  |  |  |  |  |  |  |

|              | 1.1                       | Thesis Statement                                         | 4    |  |  |  |  |  |  |  |  |  |  |

|              | 1.2                       | The Problem                                              | 6    |  |  |  |  |  |  |  |  |  |  |

|              | 1.3                       | Thesis Contribution: The X-Legion Compiler               | 12   |  |  |  |  |  |  |  |  |  |  |

| 2            | Inti                      | roduction and Related Work                               | 17   |  |  |  |  |  |  |  |  |  |  |

|              | 2.1                       | JuliusC and Recursive-DAG                                | 17   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 2.1.1 Recursive-DAG, Related Work                        | 22   |  |  |  |  |  |  |  |  |  |  |

|              | 2.2                       | Recursive D&C Algorithms: Examples                       | 24   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 2.2.1 LU-factorization                                   | 25   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 2.2.2 Matrix Multiply (MM)                               | 27   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 2.2.3 All Pair Shortest Path (APSP)                      | 29   |  |  |  |  |  |  |  |  |  |  |

|              | 2.3                       | Compiler-Driven Cache-Line Size Adaption                 |      |  |  |  |  |  |  |  |  |  |  |

|              |                           | 2.3.1 An Example and Related Work                        | 36   |  |  |  |  |  |  |  |  |  |  |

|              | 2.4                       | Application-Aware Cache Mapping                          | 39   |  |  |  |  |  |  |  |  |  |  |

| 3            | JuliusC and Recursion-DAG |                                                          |      |  |  |  |  |  |  |  |  |  |  |

|              | 3.1                       | JuliusC                                                  | 45   |  |  |  |  |  |  |  |  |  |  |

|              | 3.2                       | JuliusC: an Overview                                     | 47   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 3.2.1 Static Analysis: the Art of Divide et Impera       | 49   |  |  |  |  |  |  |  |  |  |  |

|              |                           | 3.2.2 Dynamic Analysis: Interpretation and Recursion-DAG |      |  |  |  |  |  |  |  |  |  |  |

|              | 3.3                       | Experimental Results                                     | 53   |  |  |  |  |  |  |  |  |  |  |

| 4            |                           | eursive D&C Examples from Linear Algebra                 | 57   |  |  |  |  |  |  |  |  |  |  |

|              | 4.1                       | LU-factorization                                         |      |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.1.1 LU-factorization with Partial Pivoting             | 58   |  |  |  |  |  |  |  |  |  |  |

|   |            | 4.1.2 Access Complexity of LU Factorization                   | 9 |

|---|------------|---------------------------------------------------------------|---|

|   |            | 4.1.3 Factorization Implementation                            | 1 |

|   |            | 4.1.4 Experimental Result                                     | 7 |

|   | 4.2        | Matrix Multiply                                               | 7 |

|   |            | 4.2.1 Fractal Algorithms for Matrix Multiplication            | 7 |

|   |            | 4.2.2 Register Issues                                         | 4 |

|   |            | 4.2.3 Experimental Results                                    | 5 |

|   | 4.3        | Fast Fourier Transform                                        | 9 |

|   | 4.4        | All Pair Shortest Path and Matrix Multiply                    | 2 |

|   |            | 4.4.1 A Recursive D&C Algorithm, R-Kleene                     | 2 |

|   |            | 4.4.2 Experimental Results                                    | 6 |

|   |            | 4.4.3 APSP Conclusions and Future Work                        | 9 |

|   | 4.5        | Conclusive Remarks                                            | 2 |

| 5 | STA        | AMINA: Static Modeling of Interference And Reuse 10           | 5 |

|   | 5.1        | Notation and Interference Density                             | 6 |

|   | 5.2        | Parameterized Loop Analysis                                   | 0 |

|   |            | 5.2.1 Spatial Reuse vs. Interference: Optimal Cache-Line Size | 2 |

|   |            | 5.2.2 Interference Density per Memory Reference               | 4 |

|   |            | 5.2.3 Interference Density Analysis, STAMINA                  | 6 |

|   | 5.3        | STAMINA Implementation Results                                | 3 |

|   |            | 5.3.1 Case A: SWIM-SPEC 2000                                  | 4 |

|   |            | 5.3.2 Case B: Self Interference                               | 6 |

|   |            | 5.3.3 Case C: Matrix Multiply                                 | 9 |

|   | 5.4        | Stamina Conclusions                                           | 3 |

| 6 | <b>A</b> ( | Cache with Dynamic Mapping 13                                 | 5 |

|   | 6.1        | Spatial Register Allocation                                   | 6 |

|   |            | 6.1.1 The Algorithm                                           | 9 |

|   |            | 6.1.2 Real Case: SWIM from SPEC 2000                          | 0 |

|   |            | 6.1.3 Experimental Results                                    | 3 |

|   |            | 6.1.4 Code Transformations (Appendix)                         | 5 |

|   | 6.2        | Dynamically Mapped Cache                                      | 2 |

|   |            | 6.2.1 General Hardware Mapping                                | 2 |

|   |            | 6.2.2 Hardware Dynamic Mapping                                | 6 |

|   | 6.3        | Dynamic Software Mapping                                      | 0 |

|   |            | 6.3.1 Matrix Multiply                                         | 0 |

|   |            | 6.3.2 Fast Fourier Transform                                  | 3 |

|   |            | 6.3.3 Architecture                                            | 4 |

|   |            | 6.3.4 Experimental Results                                    | 6 |

| 7 | Cor        | nclusions and Future Work 17                                  | 3 |

# LIST OF FIGURES

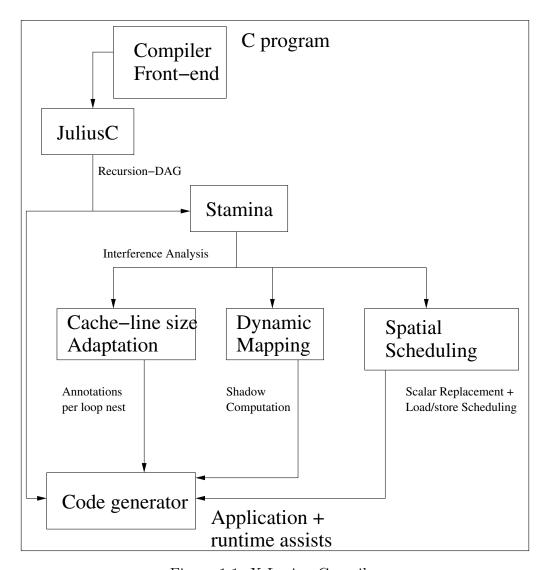

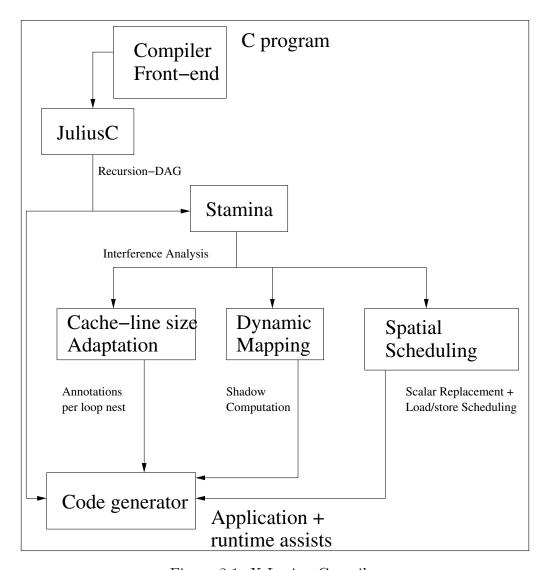

| 1.1        | X-Legion Compiler                                                                                                                                             | 13       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | X-Legion Compiler                                                                                                                                             | 18<br>37 |

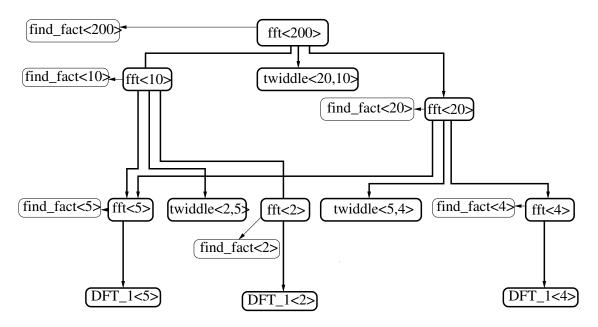

| 3.1        | Fast Fourier Transform. The factorization is determined at run-time and the recursion stops when $n$ is prime or no larger than $LEAF = 5.$                   | 46       |

| 3.2        | Recursion-DAG having $fft(*,*,200,*)$ as root associated with node $fft<200>$ .                                                                               |          |

|            | To simplify the recursion-DAG presentation, <b>find_fact</b> = find_balance_factorizate                                                                       |          |

| 3.3        | and <b>twiddle</b> = distribute_twiddle as in Figure 3.1                                                                                                      | 47       |

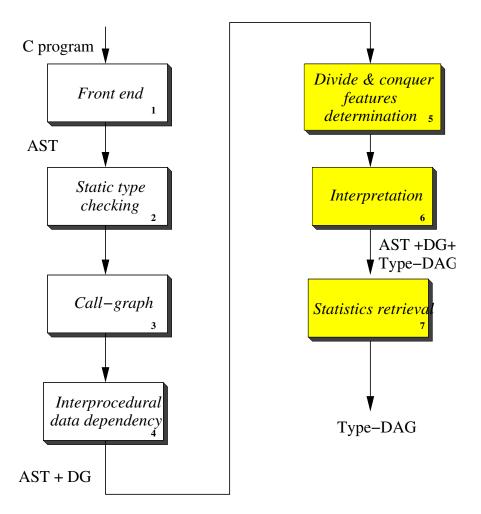

| 0.0        | stract syntax tree = AST, data dependency graph = DG                                                                                                          | 48       |

| 3.4        | Factorial: N is a D&C formal                                                                                                                                  | 49       |

| 3.5        | Update: $M$ is a MO formal                                                                                                                                    | 50       |

| 3.6        | Set: $L$ is a LO formal                                                                                                                                       | 50       |

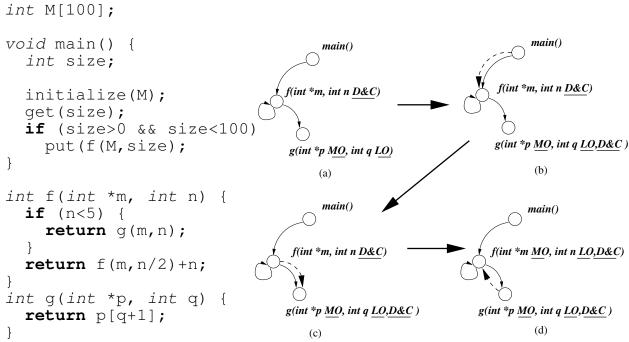

| 3.7        | Example of multiple attributes: $n$ is eventually a D&C and a LO formal, the evaluation process is schematically represented in Figure (a), (b), (c) and (d). | 51       |

| 3.8        | JuliusC's output excerpt for Balanced Cooley-Tookey                                                                                                           | 55       |

| 4.1        | Lower triangular system solver                                                                                                                                | 60       |

| 4.2        | LU factorization                                                                                                                                              | 61       |

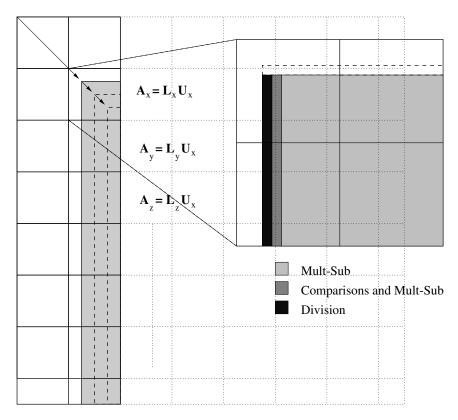

| 4.3        | Visualization of the access pattern when consecutive Gaussian eliminations                                                                                    |          |

|            | are computed                                                                                                                                                  | 64       |

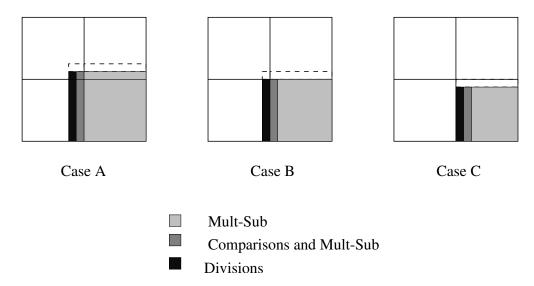

| 4.4        | Case A: The first quadrant has all types of computations. Case B: first quadrant has only a pivot element. Case C: the computation is done only in the        |          |

|            | fourth quadrant                                                                                                                                               | 65       |

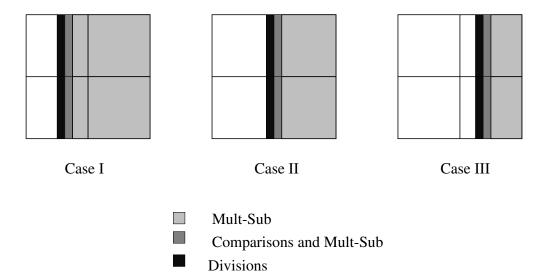

| 4.5        | Case I: in all four quadrants there are multiplication-subtractions. Case II:                                                                                 |          |

|            | divisions are performed in the first and third quadrant and Multiplication-                                                                                   |          |

|            | subtractions in the others. Case III: the computation is limited in the second                                                                                |          |

|            | and fourth quadrants                                                                                                                                          | 66       |

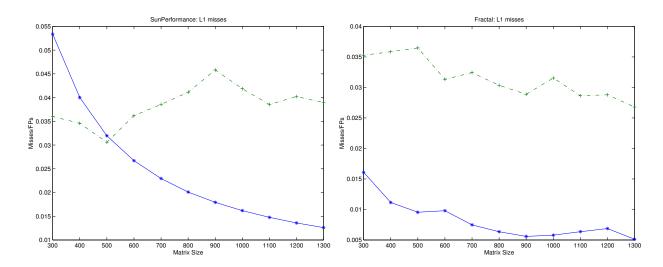

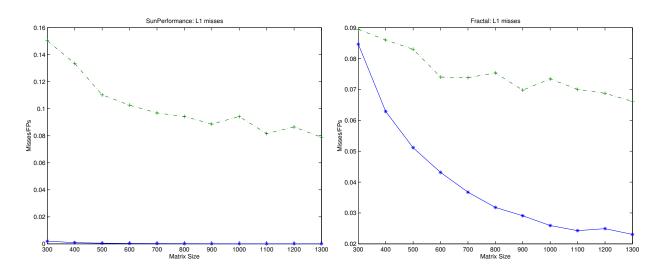

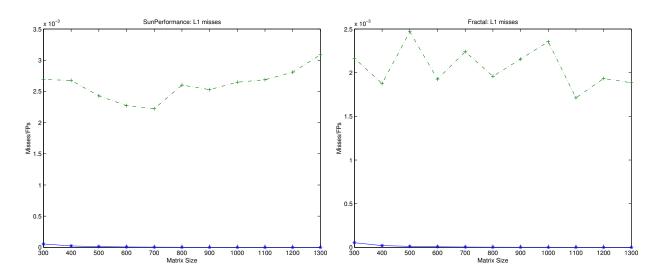

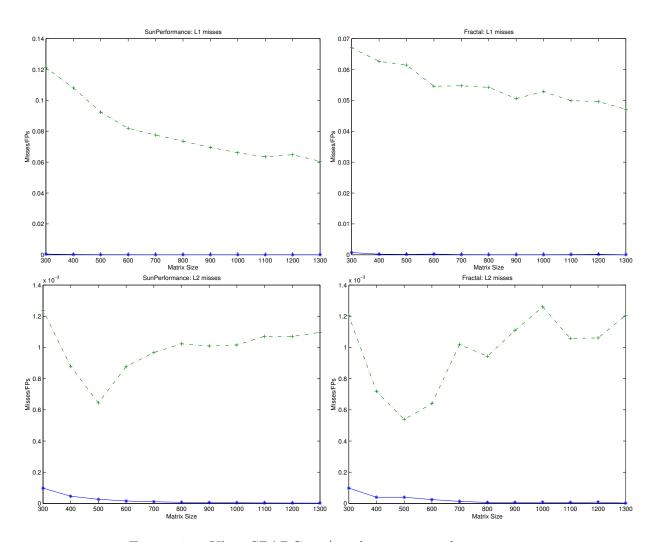

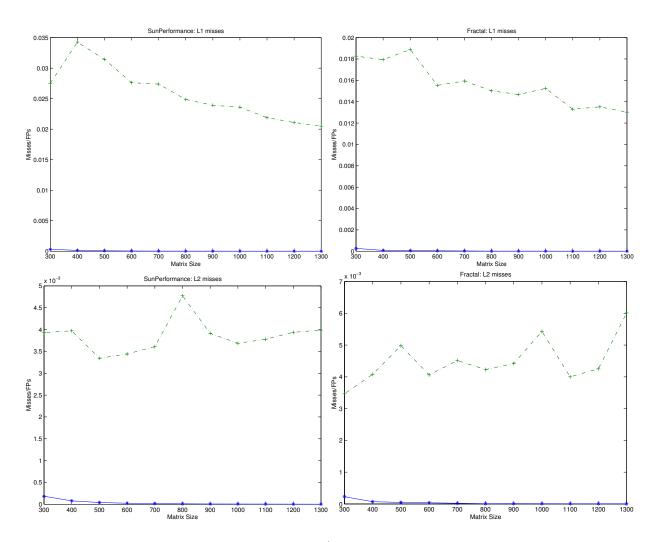

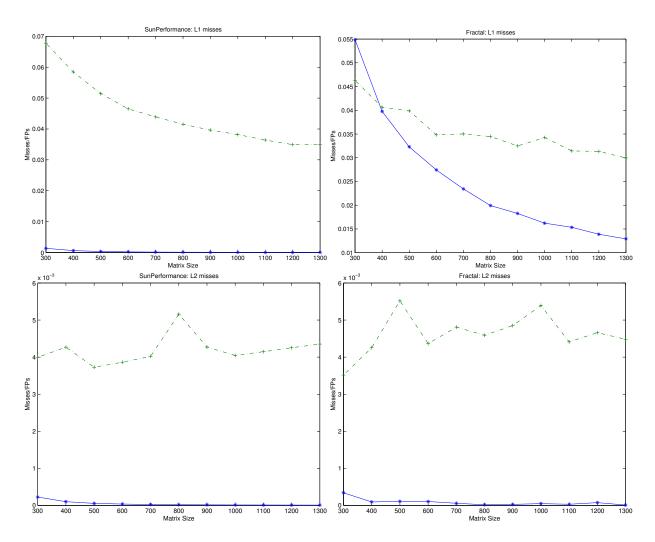

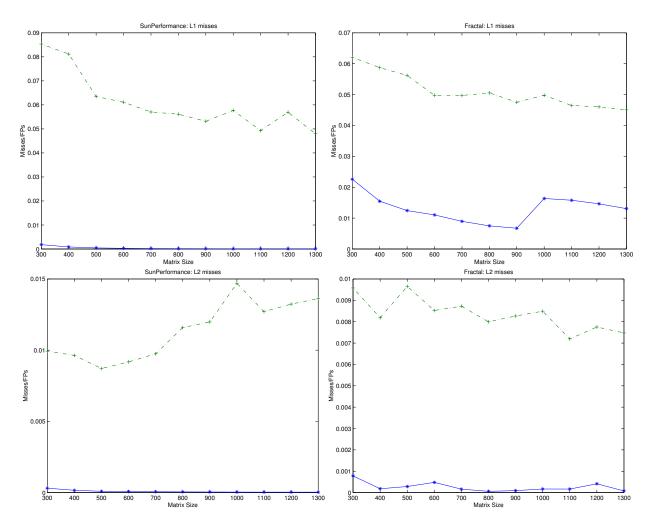

| 4.6        | SPARC 1: * code misses, + data misses                                                                                                                         | 70       |

| 4.7        | SPARC 5: * code misses, + data misses                                                                                                                         | 71       |

| 4.8        | SPARC64: * code misses, + data misses                                                                                                                         | 71       |

| 4.9        | Ultra SPARC 5: * code misses, + data misses                                                                                                                   | 72       |

|      | MIPS R5000: * code misses, + data misses                                           | 73  |

|------|------------------------------------------------------------------------------------|-----|

| 4.11 | Pentium II, * code misses, + data misses                                           | 74  |

| 4.12 | Alpha 21164: * code misses, + data misses                                          | 75  |

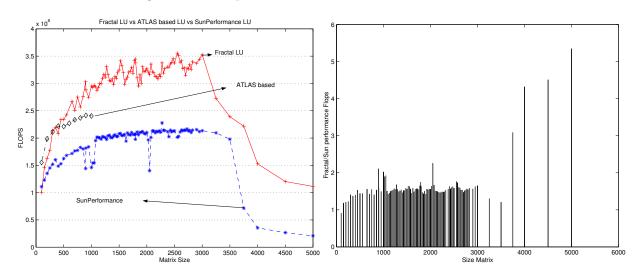

| 4.13 | Ultra Sparc 5: FLOPS and relative performance                                      | 75  |

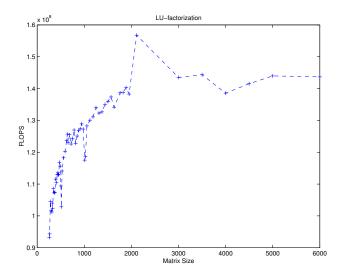

| 4.14 | MIPS R5000: FLOPS                                                                  | 76  |

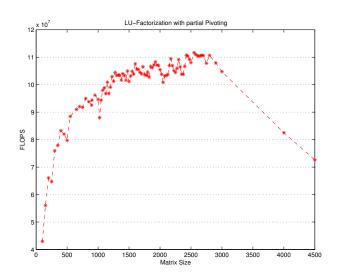

| 4.15 | PentiumII: FLOPS                                                                   | 76  |

|      | SPARC64: FLOPS                                                                     | 77  |

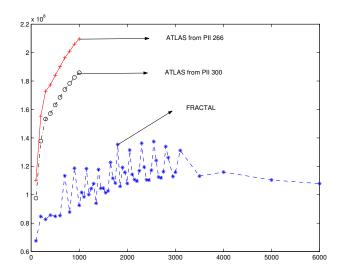

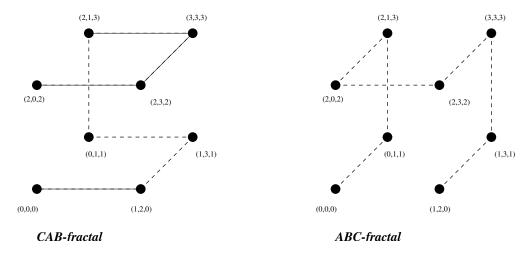

| 4.17 | The cube of calls of the fractal scheme: the Hamiltonian path defining CAB-        |     |

|      | fractal and ABC-fractal                                                            | 79  |

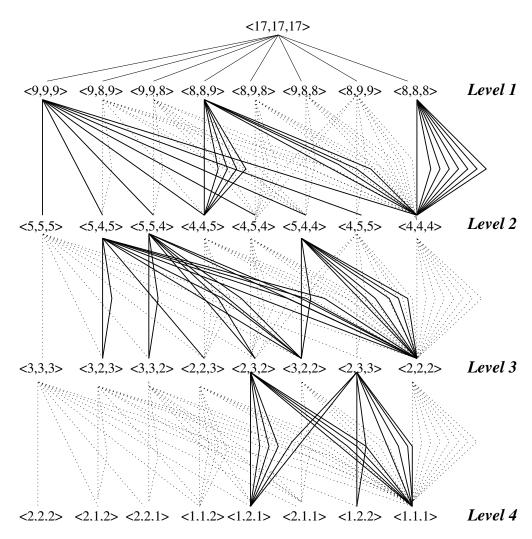

|      | Example of call-recursion-DAG for Matrix Multiplication $< 17, 17, 17 > \dots$     | 82  |

|      | Our implementation of FFT                                                          | 91  |

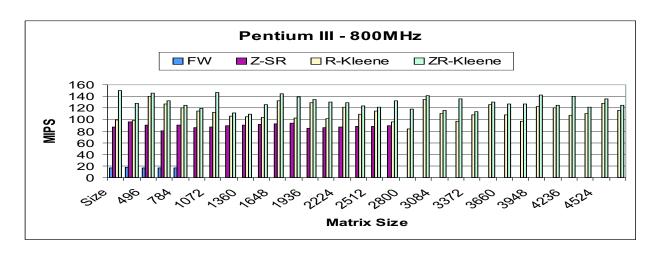

|      | (a) Kleene, (b) R-Kleene and (c) (Self) Matrix Multiply                            | 93  |

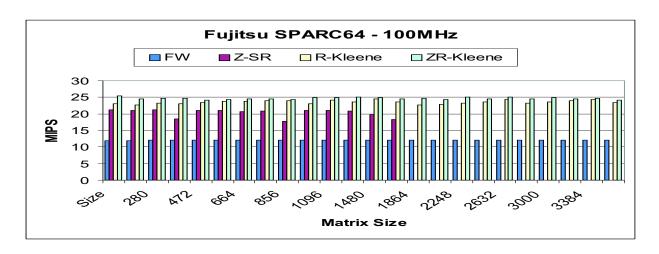

|      | Fujitsu HAL 100: best performance 4 cycles per <i>compadd</i>                      | 100 |

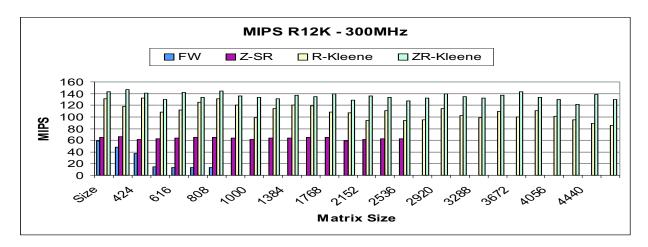

|      | SGI O2: best performance 2 cycles per <i>compadd</i>                               | 100 |

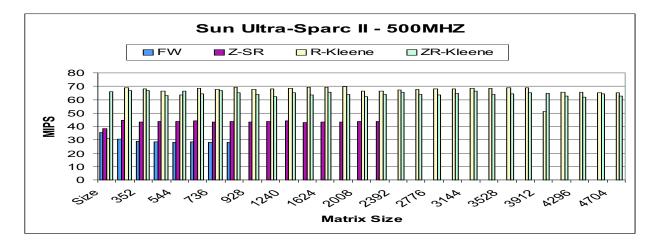

|      | Sun Blade 100: best performance 7 cycles per <i>compadd</i>                        | 100 |

|      | FOSA 3240: best performance 6 cycles per <i>compadd</i>                            | 101 |

| 4.25 | ASUS: best performance 5 cycles per <i>compadd</i>                                 | 101 |

| 5.1  | Parameterized loop bounds and index computation, thus interference                 | 108 |

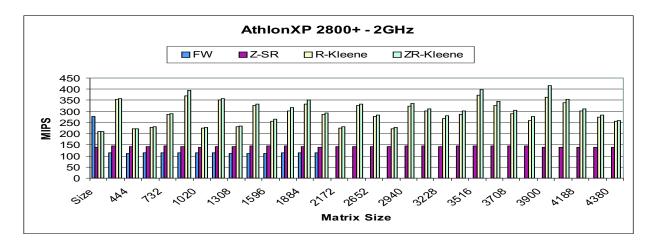

| 5.2  | STAMINA                                                                            | 111 |

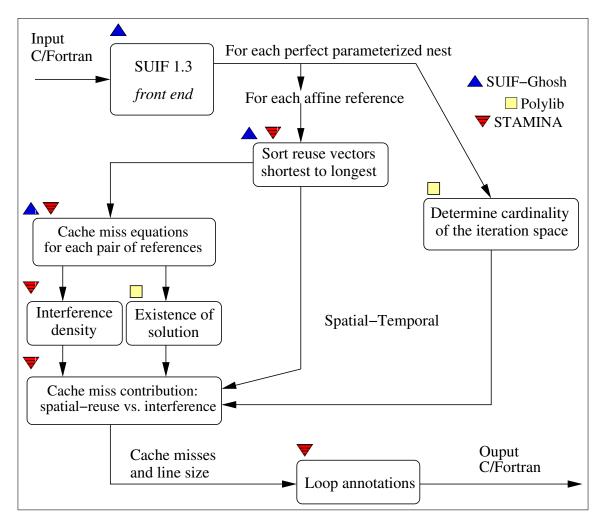

| 5.3  | Grid cells and band cells in a plane. In a 2-dimensional space grid cells and      |     |

|      | band cells are rectangles. Note that three bands pass through a grid cell          | 118 |

| 5.4  | SWIM: calc1() in C code. The comment above an instruction presents the             |     |

|      | reference numbers (RN), and the comment below an instruction presents the          |     |

|      | order in which the memory references are issued.                                   | 125 |

| 5.5  | SWIM: calc2() in FORTRAN. The comment above an instruction presents                |     |

|      | the reference numbers (RN), and the comment below an instruction presents          |     |

|      | the order in which the memory references are issued                                | 127 |

| 5.6  | Case B: Self Interference                                                          | 128 |

| 5.7  | Matrix Multiply. There are two parameters: $n$ and $m$ . The first affects the     |     |

|      | loop bounds and the latter affects the access offset on matrix $A$ . We assume     |     |

|      | that $0 < n, m < 64$                                                               | 130 |

| 5.8  | Tiling Matrix Multiplication. We have 6 parameters: $x$ , $i$ and $k$ are used to  |     |

|      | specify the loop bounds, $m$ , $n$ and $p$ are used to modify the access to matrix |     |

|      | C, $A$ and $B$ respectively                                                        | 132 |

| 6.1  | (a) spatial reuse: each line is fully read before its use. (b) only unrolling      | 143 |

| 6.2  | Loop nest in procedure calc1 using spatial register allocation                     | 146 |

| 6.3  | Loop nest in procedure calc1 using loop unrolling                                  | 147 |

| 6.4  | Loop nest in procedure calc2 using spatial register allocation                     | 148 |

| 6.5  | Loop nest in procedure calc2 using loop unrolling                                  | 149 |

| 6.6  | Loop nest in procedure calc3 using spatial register allocation                     | 150 |

| 6.7  | Loop nest in procedure calc3 using loop unrolling                                  | 151 |

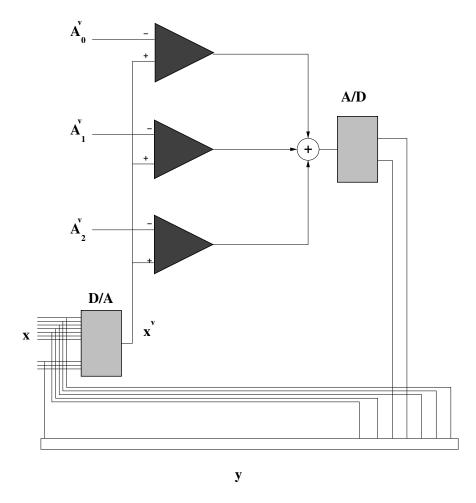

| 6.8  | Line determination by comparators and decoder                                            | 156 |

|------|------------------------------------------------------------------------------------------|-----|

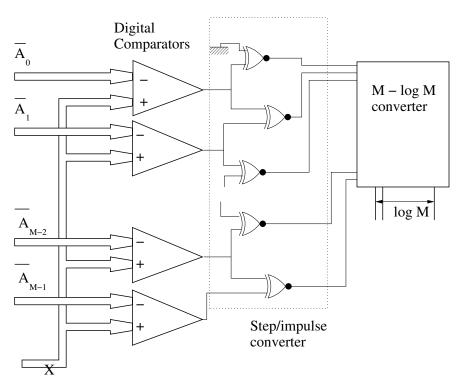

| 6.9  | Data Cache Line mapping determination using Digital Comparators                          | 157 |

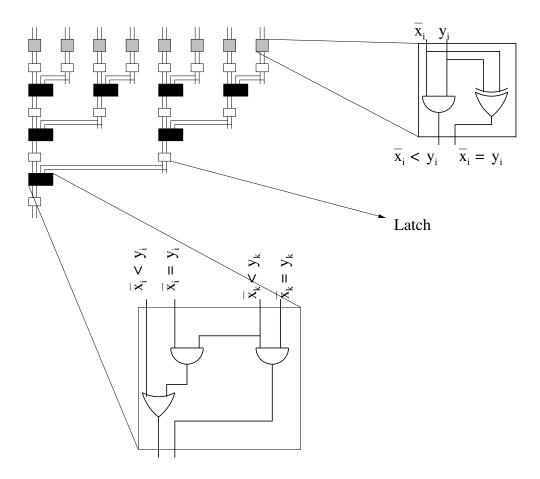

| 6.10 | Digital comparator implemented as prefix tree                                            | 158 |

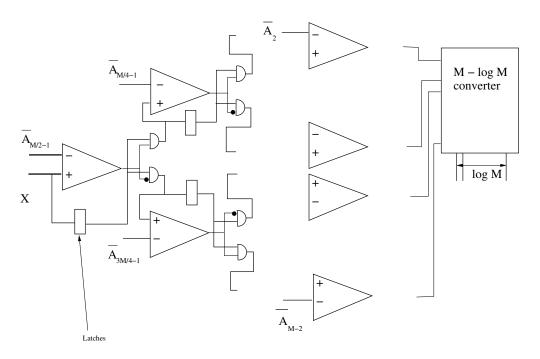

| 6.11 | Data Cache Line mapping determination using Digital Comparators and bi-                  |     |

|      | nary search                                                                              | 160 |

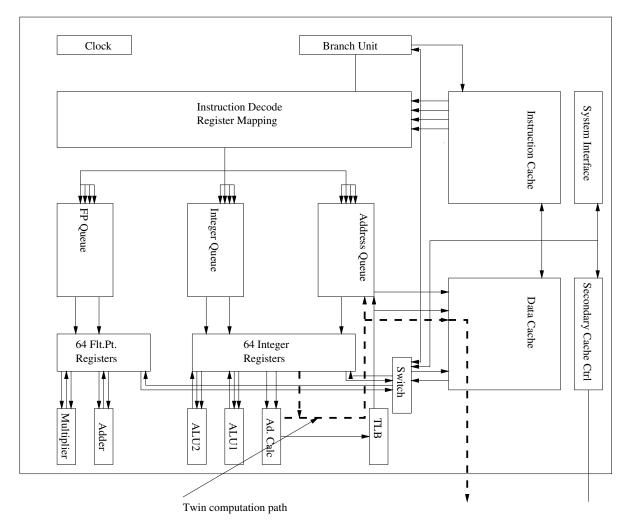

| 6.12 | Proposed architecture, designed based on MIPS R12K                                       | 165 |

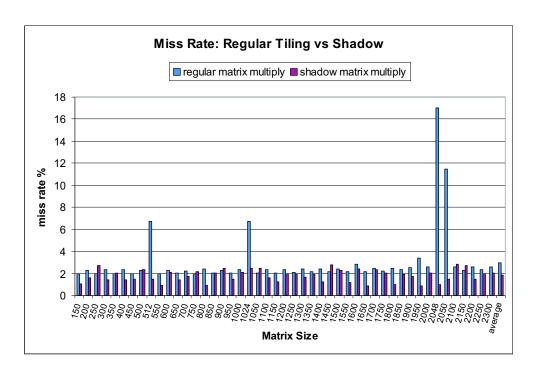

| 6.13 | Matrix Multiply on Blade 100, miss rate comparison                                       | 167 |

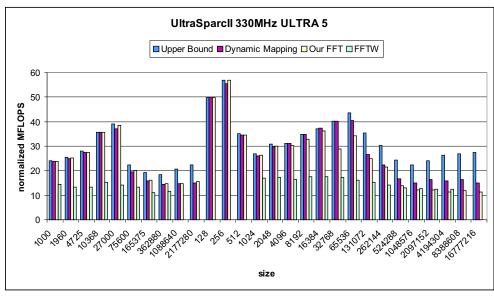

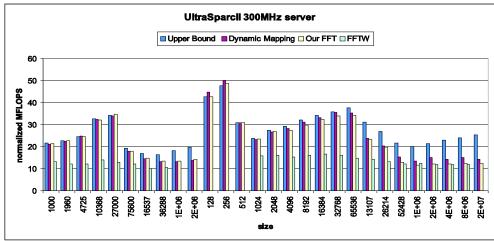

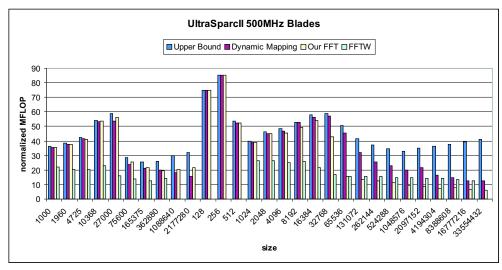

| 6.14 | FFT Ultra 5 (330MHz), Enterprise 250 (300MHz) and Blade 100 (500MHz).                    |     |

|      | Normalized performance: $n*\log n/(10^6*timeOneFFT)$ , where $timeOneFFT$                |     |

|      | is the average running time for one FFT. The bars from left to right: Upper              |     |

|      | Bound, Dynamic Mapping, our FFT and FFTW                                                 | 169 |

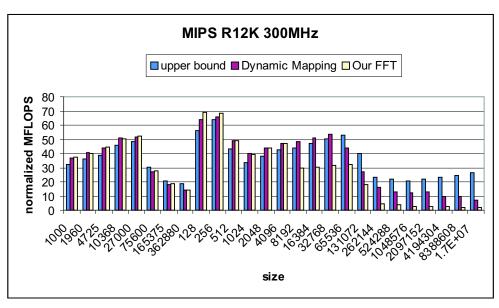

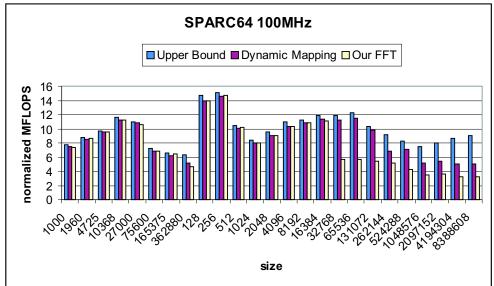

| 6.15 | FFT Silicon Graphics O2 and Fujitsu HAL 300 Normalized performance: $n * \log n/(10^6 *$ |     |

|      | timeOneFFT), where timeOneFFT is the average running time for one FFT. The higher        |     |

|      | the bar the better the performance. The bars from left to right: Upper Bound, Dynamic    |     |

|      | Mapping, our FFT                                                                         | 171 |

# LIST OF TABLE

| 3.1        | Reuse ratio $\mathcal{R}$ is a function of the problem size, the algorithm definition and the static analysis.                                                                                                                                                                                                                                   | 54                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.1 4.2    | Summary of simulated configurations                                                                                                                                                                                                                                                                                                              | 68<br>69          |

| 4.3<br>4.4 | Summary of simulated configurations                                                                                                                                                                                                                                                                                                              | 87<br>88          |

| 5.1        | Simulation of the data-cache misses due to 10 calls to $calc1()$ ; L = cacheline size in Bytes, DCMR = Data Cache Miss Rate. Spatial locality is fully                                                                                                                                                                                           |                   |

| 5.2        | exploited in $calc1()$                                                                                                                                                                                                                                                                                                                           | $\frac{126}{126}$ |

| 5.3        | STAMINA's result for Self interference example. Loop 4 and 5 have no interference for any line size, the output is set to zero. In bold face, we present the optimal $\epsilon$ per cache-line size and loop.                                                                                                                                    | 129               |

| 5.4        | Data cache misses for Matrix Multiply, Fig. 5.7, using <i>shade</i> cache simulator. We present cache misses only for cache-line size 16B, 32B and 64B (cache-line size 8B and 128B are omitted).                                                                                                                                                | 131               |

| 6.1        | Notations: <b>swim</b> $m$ is the execution time of the original application applied to input matrices of size $m \times m$ ; <b>spatialswim</b> $m$ is the execution time of the application optimized to exploit spatial locality; and, <b>unrolled</b> $m$ is the execution time for the application with the basic loop nest simply unrolled | 1.4               |

|            | four times.                                                                                                                                                                                                                                                                                                                                      | 144               |

| 6.2<br>6.3 | Read misses on Sun BLADE 100                                                                                                                                                                                                                                                                                                                     | 145<br>155        |

## ACKNOWLEDGMENTS

The support of my wife Shanyi made this work possible. She is truly everything to me.

In all these years, Prof. Alexandru Nicolau has been the greatest mentor. Our relationship has had both highs and lows, as every relationship, however, now that I look back on my life, I understand that he has always been there to help me, to guide me and to let me grow both personally and professionally. Now, I appreciate it and I know that nobody could do any better.

A heartfelt thanks goes to Prof. Gianfranco Bilardi. He sowed the seed of the recursion-DAG while we were working on the fractal matrix multiplication. Another thank you goes to Prof. Rajesh Gupta, who found ways to support my research emotionally/economically when I needed it and let my teaching experience start in a nice environment such as UCSD.

I would like to thank also Prof. Nikil Dutt and Prof. Alexander Veidenbaum (members of my topic-defense and final-defense committee), for their useful advises during the preparation of my final-defense talk and thesis.

In the following, I also thank who have collaborated with me at any time and anyway since the beginning till the final stages of this thesis. I will also give the context/chapter where they had a remarkable contribution.

#### Acknowledgments: Chapter 3

This work has been supported in part by Phi Beta Kappa Alumni in Southern California, and by NSF Contract Number ACI 0204028 and AMRM DABT63-98-C-0045. I want to thank Arun Kejariwal and Rafael Lopes for their help and time for correcting my presentation(s)/draft(s) of this chapter. I also thank Paul Stodghill for the live discussions from which JuliusC got started.

#### Acknowledgments: Chapter 4

This work has been supported in part by AMRM DABT63-98-C-0045. I thank Prof. Victor Prasanna, who introduced me to the first recursive algorithm for all-pair shortest path. I thank Nicolae Savoiu for making possible the access and the use of Windows systems to collect data, and for introducing me to Unreal Tournament, swimming and other silly things.

I thank Peter Gabi Grun and Ashok Alambi, who have been there answering my questions about scheduling and register renaming, and playing basketball.

#### Acknowledgments: Chapter 5

Financial support has in part been provided by DARPA/ITO under contract DABT63-98-C-0045. A huge thank you goes to Prof. Vincent Loechner, Somnath Ghosh, Prof. Dan Hirschberg and the members of AMRM project. In particular, I thank immensely Arun Kejariwal. They helped on Ehrhart polynomials and the existence test, cache miss equation determination, interference estimation and moral/technical support, respectively.

#### Acknowledgments: Chapter 6

This work is supported in part by NSF, Contract Number ACI 0204028. I want to especially thank Prof. Alexander Veidenbaum and Prof. Tony Givargis for helping me in the hardware organization of a cache with dynamic mapping.

I would also like to thank the following people (in no particular order): Melanie Sanders who made my experience in *using* UCI's facilities painless, I have always appreciated her friendship; Radu Cornea who helped me find my way in learning Linux's secrets and watching silly movies; Weiyu Tang for his advise on how to interpret the simulation results of adaptive memory hierarchies and for helping me out in settling-down in Irvine seven years ago. I also thank Haitao Du and Sanjay Velamparambil for the effort to disclose the *inner beauty* of Methods of Moments (MoM) and for collecting experimental results; Carol Rapp has always been kind to me and made me feel welcome; Patrick Murphy who made me appreciate the quarter final week as well as the teaching practice in a completely different way. I thank all my TAs and graders who put up with my demands and my students' requests.

I thank my mum Angela, my brothers Antonio and Fedele who really supported me and still believe in me unconditionally. Unfortunately, I wish my father Giacomo could see me now receiving my final (and last) degree and having my first real job. I wish my friend Giangiacomo was still riding this planet and, therfore, we could have yet another motorcycle trip.

## CURRICULUM VITAE

#### Paolo Nicola D'Alberto

- 1995 B.S. In Electrical and Computer Engineering, University of Padua. Thesis title: "Space Complexity of DAG Computations in Memory Hierarchies"

- 1997 First modulo of Master in Software Engineering, Tecnopadova and S.E.R.C. Padua, Italy.

#### 1998-2002 Research Assistant,

Department of Computer Science, University of California, Irvine.

#### **2000** Dottorato di Ricerca.

Thesis title: "Performance evaluation of Data exploitation"

Joint collaboration: University of Bologna, Dept. of Compute Science; University of Padua, Dept. of Mathematics Pure and Applied; University of Venice, Dept. of Compute Science

#### 2002-2004 Teaching Assistant,

Department of Computer Science, University of California, Irvine.

#### 2003-2004 Teacher Associate,

Department of Computer Science, University of California, Irvine; Department of Computer Science and Engineering, University of California, San Diego.

#### 2005 Ph.D. in Information and Computer Science,

Department of Computer Science, University of California, Irvine.

#### **PUBLICATIONS**

#### • In Journals

P. D'Alberto, A. Nicolau, A. Veidenbaum and R. Gupta: "Line Size Adaptivity Analysis of Parameterized Loop Nests for Direct Mapped Data Cache". Transactions on Computers, IEEE Society, Feb 2005.

#### • In Book Chapters

1. P. D'Alberto, A. Veidenbaum, A. Nicolau and R. Gupta: "Static Analysis of Parameterized Loop Nests for Energy Efficient Use of Data Caches". Workshop on Compilers and Operating Systems for Low Power 2001 (COLP01) - Chapter in a Kluwer book.

#### • In Conferences/Workshops

- 1. P. D'Alberto and A. Nicolau: "JuliusC: A Practical Approach for the Analysis of Divide-And-Conquer Algorithms". The 17th International Workshop on Languages and Compilers for Parallel Computing, LCPC 2004

- 2. A. Kejariwal, P. D'Alberto, A. Nicolau and C.D. Polychronopoulos: "A Geometric Approach for Partitioning N-Dimensional Non-Rectangular Iteration Space". LCPC 2004

- 3. P. D'Alberto, A. Nicolau and A. Veidenbaum: "A Data Cache with Dynamic Mapping". The 16th International Workshop on Languages and Compilers for Parallel Computing, LCPC 2003.

- G. Bilardi, P. D'Alberto and A. Nicolau: "Fractal Matrix Multiplication: a Case Study on Portability of Cache Performance". Workshop on Algorithm Engineering WAE 2001

- G. Bilardi, A. Pietracaprina and P. D'Alberto: "On the space and access complexity of computation DAGs". Workshop on Graph-Theoretic Concepts in Computer Science 2000

#### • In Technical Reports

- 1. H. Du, P. D'Alberto, R. Gupta, A. Nicolau and A. Veidenbaum: "A quantitative evaluation of adaptive memory hierarchy". UCI Technical Report (2002)

- 2. P. D'Alberto: "MIPS R12000 Processor Performance Evaluation by SPEC2000 Benchmarks and Performance Counters". UCI Technical Report (2001)

- 3. P. D'Alberto: "Fractal LU-decomposition with partial pivoting". UCI Technical Report (2001)

- 4. P. D'Alberto: "Performance Evaluation of Data Locality Exploitation". (2000 University of Bologna Technical Report Thesis)

## ABSTRACT OF THE DISSERTATION

The X-Legion

A Compiler-Approach to Exploit Locality and Portability of Divide-And-Conquer

Algorithms

by

#### Paolo Nicola D'Alberto

Doctor in Philosophy in Information and Computer Science

Department of Computer Science

University of California, Irvine, 2005

Professor Alexandru Nicolau, Chair.

The solution of linear systems is an ancient and inexhaustible problem. In time, the theory and the techniques to solve this problem have evolved and, today, hardware and software technologies thrive to achieve high-performance systems for the efficient solution of systems based on what is now defined as **matrix linear algebra**, and, in turn, efficient matrix computations and matrix algorithms.

My main contribution is in the investigation and implementation of techniques for the analysis of data locality in **divide-and-conquer** (D&C) algorithms, both recursive and non recursive, and their application to drive novel memory-hierarchy adaptations at compile time –i.e., static– or at run time –i.e., dynamic. I show the practicality and benefits of these techniques when applied to algorithms for linear algebra, matrix computation kernels and graph manipulation. In practice, I investigate and propose techniques for code organization through data-layout and computation re-organization in order to exploit data locality. Especially in this work, I present compiler-driven optimizations for the best utilization of the

memory hierarchy starting from the register files to the efficient utilization of the translation look-aside buffer (TLB) and, thus, hard-disk access(es).

These compile-time techniques are deployed in an investigative framework: X-Legion compiler –i.e., the tenth-legion compiler. JuliusC (Julius Caesar) is the leading component of the X-Legion compiler and it analyzes the division process of recursive D&C algorithms. Such an information leads to the modeling of the computation unfolding, the (automatic) reduction of the algorithm division work, and the targeting of optimizations driven by another compiler component, STAMINA. In fact, STAMINA is an analysis tool for the estimation of cache interference due to data memory reference in loop nests. In turn, the interference analysis drives the application of further optimizations to exploit spatial and temporal locality such as cache-line size adaptation and dynamic mapping.

# CHAPTER 1

## Thesis Statement and Contribution

Intuitively in a **Divide-and-Conquer** (D&C) algorithm, a computation has *locality* when we can find a suitable division of the computation into sub-computations, and every sub-computation has a high ratio between number of operations and number of input data. The ratio estimates the computation's inherent ability to amortize the cost of reading the input data over the amount of processing based on the input data. In practice, a high ratio means that the computation exploits data reuse and it spends little time reading data and more time performing *useful* computations. Otherwise, a low ratio means that the computation has little data reuse, and, thus, the same data read are used for few computations.

The exploitation of locality is crucial for any applications executed on modern architectures with deep memory hierarchy. Indeed, if the application has data locality, the architecture is able to store the most frequent data in small and fast caches so reducing the average data access time and speeding up the computation progression. In fact, data locality exploitation must be addressed starting from the design of the algorithm, while building the basic blocks of the application, to the design of the algorithms' data structures and layout.

For a specific application, a developer may devise an estimation-measure and she may use it to guide the design of **cache conscious codes** for the application; that is, codes that are tailored to take advantage of the presence of caches and their specific organization. Though in practice, an estimation often suffices an experienced developer in the design and

implementation of specific codes – e.g., for a first and preliminary solution to a problem; however, an estimation may not suffice an application-specific code generator and, certainly, it will not suffice a general-purpose compiler.

In practice, an estimate must be validated so as to be reliable and truthful, and it should be practical to use and apply. Moreover, an automatic approach needs more than a guideline, it needs a measure, a number, which quantifies the contribution of a technique precisely and concisely. In fact, the capability to quantify an application locality –within a certain accuracy— is essential for any automatic approach. For example, an optimizing compiler needs to determine statically the trade-off among different optimizations for an adaptive processor-cache system, and it may need to choose a particular configuration among several ones (e.g., for optimal performance). A compiler must have a quantitative and precise measure of the benefits, so that it may choose the best solution without any further help from the developer.

This chapter is organized as follows. In Section 1.1, we state our motivation for the investigation and we summarize it by a thesis statement. In Section 1.2, we present the problem in detail and, thus, the compelling reasons for its solution and the effect of such a solution in its context. In Section 1.3, we outline briefly our contribution and our preliminary implementation as an investigative compiler aimed at the implementation of our solution. In this work, we show and enforce the potentiality of compiler-driven approaches such as the ones implemented in X-Legion compiler (pronounced the tenth-legion compiler) <sup>1</sup>

### 1.1 Thesis Statement

The X-Legion Compiler implements hybrid techniques, that is, software optimizations or

<sup>&</sup>lt;sup>1</sup>The name of the compiler emerges from the components and their interaction. In fact, JuliusC is the first component and it stands for Julius Caesar; JuliusC analyzes the application solution strategies and it drives some of the optimizations at the highest level of abstraction. Indeed, in the Gaul's war the tenth legion was under the direct control of Julius Caesar (on the field), it was composed by the most loyal and experienced legionaries who showed the most stamina in action.

hardware adaptations based on compile-time analysis and run-time deployment based on static analysis. Such techniques are tailored to the optimization of recursive divide-and -conquer (D&C) matrix algorithms and they exploit data locality and use direct-mapped data caches.

The contribution of this thesis is based on the importance of the applications and on the importance of the cost/performance/power advantages of using simple data caches and new hybrid techniques.

In practice, matrix algorithms are the core of scientific computing and applied matrix algebra, therefore even a small improvement in one of the basic kernels can be extremely beneficial. The optimal implementation (i.e., with minimum number of cache misses) for a family of matrix algorithms is compelling for performance purpose and for the efficient utilization of complex (and often expensive) systems. We explore the extent of D&C matrix algorithms and their cache obliviousness achieving portable and optimal performance. Moreover, the data locality of these applications yields potential avenues for the automatic exploitation of coarse and fine grain of parallelism.

A simple cache design has the following effects on the trade-off among performance, cost and energy consumption:

• Large caches improve average data reuse and therefore performance, and, with the same cache size, a direct-mapped cache has faster hit access time than an associative cache. However, an associative cache may reduce cache interference, distributing interfering memory accesses to different blocks, reducing average access time.

If we achieve the same cache miss ratio using a direct-mapped and an associative cache, we have better performance using direct-mapped caches only.

• With caches of the same size, direct-mapped caches dissipate less energy per access

than associative caches, because associative caches perform a search for data in every block, either in parallel or sequentially.

If we achieve the same cache miss ratio using a direct-mapped and an associative cache, we obtain better energy consumption using direct-mapped caches only.

- Modern processors have already embedded one or two levels of caches; these caches

occupy the majority of the chip real estate. A direct-mapped data cache will simplify

the design and the saved real estate may be used for other purposes.

- Multiprocessor systems may have thousands of processors and a small cost reduction per processor can be significant overall. A simple memory hierarchy translates into a simple architecture design and in low costs.

We evince our thesis as follows: We show how we can exploit locality by using: only code organization, only memory-hierarchy re-configuration, and a combination of the two. We explain how performance may vary as a function of the input sets and we show how adaptation of code and architecture is key to achieving optimal performance in any input scenario. We propose methods for the estimation of locality and we propose practical approaches for the quantification and exploitation of locality. We show the benefits of our approach by experimental results that are obtained as a combination of the following: direct measurement of performance (e.g. wall clock), by simulation (e.g. cache-processor simulators), and by hardware counters (e.g. MIPS R12K, UltraSparc II). We also discuss an interpretation of such metrics and their interdependencies.

## 1.2 The Problem

If we observe the unfolding of the computation of a D&C matrix algorithm and especially its division in subcomputations, we may measure the locality by counting directly the number of computations and memory accesses. In this way, for a given fixed application and its

execution, we may verify whether or not the computation has optimal locality performance rather quickly -e.g., optimal = the minimum number of cache accesses over the number of arithmetic computations. However, if we want to steer the algorithm division strategy and the computation so as to achieve optimal performance, we face an arduous task because this problem is reducible to the scheduling problem, which, in turn, is an NP-complete problem.

The definition of **optimum** is dependent on the context, and in general it is the minimization of a **goal function**. If the goal is to achieve optimal performance, the application must be reorganized so that it has minimum execution time or minimal number of cycles. When the goal is to achieve **optimal work**, the application must be reorganized in such a way that it has minimum number of (basic) operations. In the literature, the **cache miss ratio**—i.e., the ratio of the number of cache misses over the number of cache accesses— is the common measure for the locality of an application. When the goal is to achieve optimal locality, the application must have minimum cache miss ratio. Also the term **cache miss rate** is commonly used and it is defined as the miss ratio multiplied by 100, that is, the number of misses as the percentage of accesses. Finally, when the goal is the minimization of power consumption, we can show that the optimal implementation minimizes a weighted sum of all of the previous goal functions, such as number of cycles, number of instructions and number of cache hits and misses.

In modern architectures, the relation among these goal functions can be puzzling at best. For example, an optimal application for its work may not be optimal for performance or locality, or vice versa. In general, the choice to optimize an application for one goal function, instead of another, depends on the context. If the technology advancement continues, the CPU's speed will double every 18 months – Moore's law, caches and memory will be twofold faster and larger every two-three years, and batteries lasting power will double only every five years; we can see that caches, memory and battery will be crucial resources: caches will represent the performance bottleneck of an architecture and the battery power will limit

considerably mobile computing. In this work, we address these problems by estimating the effect of our techniques measuring three metrics of performance: execution time (i.e., direct measure of wall clock or synthesized measure of it as mega floating point operations per second MFLOPS), data cache miss rate (ratio), and, sometimes, power consumption.

The problem escalates in proportion and difficulty when we search for an optimal implementation for a family of goal functions (or, even more difficult, a family of applications for a family of goal functions); for example, we may want to find a single implementation of an algorithm that, unchanged, has optimal performance for several different architectures. Even though in general such a *champion* does not exist and we need to select one champion for one application and one architecture, we present examples of algorithms that, *practically unchanged*, achieve *nearly* optimal/predictable performance for several different architectures.

In this work, we introduce a family of applications that have optimal and inherent data locality. We also present techniques to reorganize this family of applications to exploit—for every input—both data locality and system resources fully. D&C algorithms exploit locality naturally. The division of the main computation in sub-computations exposes an independent set of data and computations, which can be divided further. The division process stops when the computation can be performed—efficiently. If sufficient resources are available, we may ply low and high levels of parallelism and we may reduce inter-processors communication. If a single processor is the host of the computation and the memory hierarchy has multiple levels of caches, the division of the problem in smaller problems is tremendously beneficial as well. In fact, we divide large problems, for which data must reside in slow storage devices (e.g., disk and tape), in more manageable problems that we solve as soon as we bring the data in main memory; if we divide the problem a level further, we can solve smaller problems as soon as the data is in cache.

Algorithms applying the D&C approach are ubiquitous for problems on volumes of data.

We present and investigate D&C algorithms for linear algebra for dense matrices [1, 2], and algorithms characterization for hierarchical memories [3, 4]. We work with the following examples of linear-algebra applications:

• **LU-Matrix Factorization** is used in non-iterative algorithms for the solution of systems of equations, such as  $\mathbf{A}\mathbf{x} = \mathbf{b}$  where  $\mathbf{A}$  (matrix of coefficients) and  $\mathbf{b}$  are known and  $\mathbf{x}$  is unknown. The solution follows these steps: first, we determine two matrices  $\mathbf{L}$  and  $\mathbf{U}$  so that  $\mathbf{L}\mathbf{U} = \mathbf{A}$ , where  $\mathbf{L}$  is a lower triangular matrix and  $\mathbf{U}$  is an upper triangular matrix [5]. Thus, we have reduced the system to two simpler triangular systems. Second, we solve the system  $\mathbf{L}\mathbf{y} = \mathbf{b}$  and and then  $\mathbf{U}\mathbf{x} = \mathbf{y}$  so to compute the final solution  $\mathbf{x}$ .

Notice that the solution of triangular systems (upper and lower), as well as the matrix factorization, have matrix multiplication as kernel computation, and, they also inherit the data locality properties of matrix multiply, <sup>2</sup> see the following point.

• Matrix Multiplication (MM), C = AB, where A, C, B are square matrices of size  $n \times n$ , is kernel for basic matrix factorization algorithms and linear algebra applications [6, 7, 8]. There is a countless number of implementations for MM and we can distinguish them by their computational complexity. For example, if we start from the fastest to the slowest, we have: Coppersmith-Winograd's [9] with complexity  $O(n^{2.31})$ , Strassen's [10] with complexity  $O(n^{\log 7})$ , and the definition, ijk-matrix multiply with complexity  $O(n^3)$ .

The latter, ijk-matrix multiply has been proved to achieve optimal cache locality [11], and, in fact, MM is one of the **cache oblivious algorithms**; that is, there is an implementation that, unchanged, is optimal (asymptotically) in the number of cache misses for an ideal cache  $^3$  of any cache size.

<sup>&</sup>lt;sup>2</sup>We use interchangeably matrix multiplication and matrix multiply

<sup>&</sup>lt;sup>3</sup>I.e., fully associative cache with ideal optimal cache line replacement policy

• Matrix by vector multiplication is basic computation in BLAS 2 and, it is especially used for the change of representation of a vector using different space bases. In particular, the spectral analysis of digital signals, such as the application of Discrete Fourier Transform (DFT) on discrete digital signals, is commonly used for the design and implementation of discrete digital filters. When the discrete signal is considered periodic for a certain number of points (i.e., after a certain number of samples or points the signal has the same repetitive form) the DFT algorithm is amenable to be optimized: the algorithm is known as the Fast Fourier Transform (FFT). The most famous implementation of FFT it may be the FFTW[12]. Notice that FFT is another cache oblivious algorithm.

The inherent cache locality of linear-algebra applications make them an excellent test set where we are able to investigate optimizations aimed to exploit fully the potentials of these applications. To exploit locality and performance even further, matrix algorithms may require *ad-hoc* organization of the data matrices; in fact, the layout of matrices may speed up the transfer of data to/from different levels of the memory hierarchy (i.e., allowing fast data-block transfers), and it may reduce cache interference (i.e., especially self interference).

Aggarwal et al. [13] present the first clear performance model for memory hierarchy with block transfer. Their model aims to represent the communication cost in real systems, where in practice, all transfers among different level of the memory hierarchy are among blocks of data. In fact, all data transfers between disk-memory and memory-caches break down eventually to a transfer sequence of large blocks of continuous data. For a hard disk, the seek time –i.e., the time to move the hard-disk head on the wanted data– dominates the transfer time, because it is of the order of milliseconds; however, when the hard disk head is moved successfully on top of the first sector, the data transfer involves large data blocks (of up to 512KB each) and is extremely fast (GB/s). The transfer of data among caches and memory has similar spatial locality characteristics, but instead of large sectors,

the data transfer involves smaller data blocks, called lines, usually having sizes between 32B and 128B.

To return to the subject of how data layout may affect performance, the reorganization of matrix layouts changes how the computation accesses the data as well as how the data are mapped in cache during the computation. For example, a careful organization of the data into the hard disk can minimize data transfer latency and maximize the use of the data block at every memory level: for example, exploiting page locality in main memory, exploiting cache-line locality in direct-mapped and associative caches, and, finally, continuous loads/stores in registers.

Data layouts have been adopted in conjunction with blocked algorithms early in their design and application, but they have received particular attention for recursive algorithms. Indeed, these layouts are known as recursive layouts [14, 15, 16]. Recursive layouts have been applied first for surface-rendering problems with massive data sets, then proposed for standard linear-algebra applications. In the following, we introduce the most compelling reasons why recursive algorithms are attractive, and especially for code portability across architectures and for code analysis by compilers.

In this work also, we propose a new processor-cache system that allows a partial adaptation of the data-cache organization to the application requirements at run-time. Our processor-cache system does not need to change dramatically during the computation; the system morphs from one configuration to another by small steps and, in general, adapting the functionality without changing the hardware configuration. That is, we propose a direct-mapped cache (e.g., 32KB) that may change its cache line size (e.g., 8, 16, 32, 64 or 128B) or its mapping function (e.g., the memory address x is mapped to the cache line  $f(x) = \ell_i$ ), but it will remain a direct-mapped cache of the same size (e.g., 32KB). We show that we can achieve optimal performance across different architectures, different cache sizes and cache organizations, because we make the application and the system work together for a common

goal. We do this by using compile-time techniques to reorganize the code application and annotating the application itself; the annotations are read and interpreted at run-time and the application-architecture adapts.

In our search for optimal performance, even when highly tuned or hand-coded applications show better performance on a specific architecture than our codes, we find a system configuration (i.e., software and hardware combination) that presents predictable performance for all input sizes. In a modern view of a system, the interaction between architecture and application is one component in a more complex equation. We believe that the predictable performance of an application is a crucial feature —especially for power management— because it allows the operating system, or the user, to plan in advance the further utilization of the architecture. For example, the operating system may plan to set to idle part of the system when the application has reached completion, thus, saving energy.

## 1.3 Thesis Contribution: The X-Legion Compiler

In the following, we introduce our novel compiler techniques for the analysis and optimizations of D&C algorithms. In fact, we discuss the implementation of these techniques in an investigative compiler that we call **X-Legion compiler** – the tenth-legion compiler. The main goal of this compiler is the analysis and model of D&C algorithms in such a way to exploit locality and software portability by addressing code optimizations and compiler-driven memory-hierarchy adaptations such as cache-line size and cache mapping for data caches.

The organization of the following section mirrors the organization of the thesis. In fact, we present each component of the experimental compiler X-Legion, in Figure 1.1. In short, we describe the dynamic of X-Legion as follows. A D&C input application, written in C, is transformed into an **intermediate representation** IR, which represents the entire program in a single hierarchical structure. Then, **JuliusC** (briefly introduced in Section 2.1 and fully described in Chapter 3) takes the hierarchical structure of the application and determines the

Figure 1.1: X-Legion Compiler

call graph of the program. In practice, Julius C determines whether a function is recursive or a function is a computation leaf. The main two goals of Julius C are: first, the analysis of the problem division and, especially, the division of a recursive D&C implemented in the input application; and, second, the concise representation of such a process by a **recursion-DAG**. A recursion-DAG is a direct acyclic graph that describes the unfolding a recursive function.

If this is possible at compile-time, the recursion-DAG can be used for the analysis of the **leaf computations** and their interaction. In fact using the recursion-DAG, we are able to

synthesize information about the hot spots of the application by computing the frequency of a function call. Also, the recursion-DAG can be used to collect statistics about the problem size of each function call and, thus, it can be used to reduce the complexity of specific analysis performed by **STAMINA**. So the recursion-DAG has two purposes: to expedite the application and the compilation execution time.

Otherwise, that is, if the recursion-DAG cannot be built at compile-time, we can reorganize the application so that we can generate the recursion-DAG at runtime and use it to speed up the execution of the recursive section/part of the application. We introduce this topic in Section 2.2 and we explain the approach in Chapter 4.

Independently, whether or not the recursion-DAG can be determined at compile time, STAMINA extracts the loop nests of the application and analyzes only the perfect loop nests, which are the most computation demanding (leaf computation). We give an introduction to STAMINA in Section 2.3 and we discuss the approach in Chapter 5. The goal of STAMINA is to analyze and quantify the cache interference per memory reference in the inner loop of a loop nest. Such an analysis drives the activation of three possible optimizations/adaptations: cache-line size, dynamic mapping and spatial scheduling. In fact, if major cache interference afflicts the leaf computations, then the leaf computation performance and the overall application performance will slowdown.

The result of the interference analysis, generated by STAMINA, is used to drive the data cache-line size —on a per loop nest basis—by introducing a special instruction (or annotation). In fact, a large cache-line size reduces the number of data fetches but it may increase cache interference; otherwise a short cache-line size may reduce cache interference, because it also changes the data cache mapping, but it increases the number of data fetches. We give an introduction in Section 2.3 and present the approach in Chapter 5.

An adaptation, which is orthogonal to adaptive cache-line size, is dynamic mapping. In fact, we may tailor the data cache mapping to the application and make the cache believe that the memory addresses used to store and retrieve data in cache is different from what it is actually used in memory. We call this alternative memory space **shadow space** and the computation in the new space, **shadow computation**. This approach introduces extra computations, such as the ones introduced while padding matrices to reduce cache interferences [17]. The main differences are that no extra space is required, the extra computations are introduced only when interference is estimated heavy, and the speed-ups achievable overcome the overhead introduced by the extra computations.

At last, we may circumvent the effects of cache interference by a careful memory access scheduling and register allocation only. In practice, we propose **spatial scheduling**: this is a source-to-source transformation that, using scalar replacement, compacts consecutive in-memory accesses into a sequence of loads into scalar variables, thus into registers; this new load scheduling exploits fully spatial cache locality and it reduces the effect of cache interference. We give an introduction in Section 2.4 and present the approach in Chapter 6.

# CHAPTER 2

# Introduction and Related Work

The goal of this chapter is to introduce the thesis contribution and the related work in a fashion that is context sensitive. Indeed, here we introduce the components of the X-Legion compiler, Figure 2.1, and the related work, which is interdisciplinary in nature and comprises ideas ranging from algorithm engineering to data allocation to registers.

This chapter is organized as follows. In Section 2.1, we introduce Julius and our approach to extract information about D&C algorithms by using a data structure that we define as a recursion-DAG. In Section 2.2, we present four applications for which we used the recursion-DAG directly so to achieve an efficient implementation. In Section 2.3, we present the software package STAMINA for the analysis and determination of the best cache-line size. We present in the following sections how STAMINA's analysis is used. In practice, in Section 2.4, we present two techniques exploiting such an analysis: first, we propose a data allocation to registers to circumvent the effects of cache interference, secondly, we present a technique to tailor the cache mapping to the application's needs.

## 2.1 JuliusC and Recursive-DAG

With the introduction of D&C algorithms for the solution of matrix computations, for example, BLAS 3 [18], the performance of scientific applications has improved markedly. In fact, D&C computations expose spatial and temporal data locality; in turn, this data locality

Figure 2.1: X-Legion Compiler

results in efficient utilization of resources on modern uniprocessor/multiprocessor systems; therefore, it results in extremely good performance. In practice, D&C algorithms can be a priori implemented using either of two language constructs: loop nests or recursion. From hereafter, we refer to the algorithms implemented using loop nests as **blocked**, and to those using recursion as **recursive** algorithms.

Though, most implementations are blocked algorithms [1, 8] and only a few implementations are recursive algorithms [6, 19]; however, recursive algorithms are appealing because of

their intuitive formulation and implementation. In fact, recursive algorithms are top-down solutions; they exploit data locality naturally at every cache level in architectures with deep memory hierarchies; they expose data dependency intuitively and, in turn, parallelize naturally along the recursive calls [20]. Indeed, most recursive matrix algorithms, such as matrix multiply and LU-factorization [5], are *cache oblivious* [21]. That is, they have optimal cache reuse at any cache level with no need for tuning –except for the register file [22] where some code tuning may further increase performance. Ultimately, recursive algorithms represent an efficient solution in a more abstract and intuitive format because the developer does not need to know the details of the architecture on which these applications will run.

Despite the above advantages, recursive algorithms have been considered impractical (for high-performance applications) for two reasons. First, a compiler has a difficult time optimizing at which point the recursion should stop (leaf computation). Thus, if only recursion is applied, the leaf computation may have too few instructions leaving little room for optimizations, exploiting little register reuse, and, especially, incurring a high overhead due to the (otherwise avoidable) proliferation of small recursive procedure calls. Second, any recursive algorithm *inherits* an overhead due to the division process, or partitioning, which is intrinsic in D&C algorithms, into small subproblems. This overhead is proportional to the number of function-recursion calls and to the work involved in computing the actual parameters of a function call.

Due to the importance of such computations, practical and efficient solutions of basic matrix computations have been the center of substantial efforts in terms of time and money in the last decades. As a result, ready-to-use and highly-tuned libraries for several systems have been proposed and used [7] and, more recently, self-installing and self-tuning libraries arose as new standards [8, 23] delivering astonishingly good performance. Briefly, self-installing and self-tuning libraries extract the parameters of an architecture and tailor the source codes to the architectures using exhaustive or tailored search techniques. These libraries are based on

blocked algorithms rather than recursive ones because of the mentioned recursive algorithm problems and for a number of other reasons: the first that comes to mind is code legacy, for example, FORTRAN has no-recursion; a second is the compactness of the code, thus the amenability to traditional aggressive compiler optimizations; and, finally, the most famous reasons are the negligible overhead introduced by loops instead of recursive calls, and ability to tile a loop nest so as to exploit temporal locality of references [24].

However, with the explosive increase in the complexity of systems due to the rapid advances in semiconductor technology, the number of parameters describing a system also increases. This undermines the portability and efficiency of current self-tuning high-performance applications. The complexity of probing the parameters as well as the complexity of tailoring the source code to an architecture will become impractical—if not quixotic. As a result, recursive algorithms for matrix computations should become increasingly appealing, if only they can be made more efficient by addressing their inherent problems as mentioned previously.

Several authors, among them us, target the solution of the recursive algorithm problems proposing applications based on both loop nests and recursion [25, 22, 12]. A recursive algorithm implements the division process, exploiting the *oblivious* data-cache locality. A blocked algorithm implements the leaf computation, exploiting aggressive compiler optimizations. These authors propose to stop the recursion at a certain level and then call high-performance non-recursive routines. This is also known as **pruning**. Pruning reduces the number of function calls, and therefore it reduces the overhead; however, it does not reduce the work per function call; that is, the computation of the actual parameters for every function call.

We propose a novel technique for greatly improving efficiency of D&C algorithms. We introduce the concept of a DAG data structure, **recursion-DAG**, to model recursive algorithms; for example, using a hand-coded implementation of the recursion-DAG, we were able to reduce the integer computation –index computation to access matrix elements– by 30% in

matrix multiplication, see Section 4.2, on page 77, [22]. In practice, we propose an automatic approach for the determination of the recursion-DAG of general recursive algorithms and we have four main contributions:

- 1. In Chapter 3, we present **JuliusC** [26], a (lite) C compiler. We present techniques for the determination of a recursion-DAG, and provide algorithms to fully automate it. We also show that the approach has practical time and space complexity.

- 2. We present techniques to model the run-time unfolding of recursive algorithms concisely and to abstractly represent function calls with the same division work as a single node in a recursion-DAG.

- The model is a concise and precise representation of the computation and we envision its application as support to drive further compiler techniques/optimizations such as dynamic cache mapping [27] and automatic parallelization, for example, using sophisticated abstract data description [28] and in combination with parallelizing techniques/compilers [29].

- We show how the system embodying the above techniques can be useful as an analysis

tool for performance evaluation purposes, for software design purposes and also for

debugging purposes.

- 4. To illustrate our techniques and provide a feel for the improvements achievable, we show that we can reduce the division work by 14 or more times for the computation of the binomial coefficients –actually, the original exponential execution time becomes polynomial– and by 20 million times for all-pair shortest path of an adjacency matrix (of size 7500 × 7500). We show that the division-work reduction is a function of: the problem size, the algorithm and the pruning technique.

Notice that in parallel applications on large data sets, the division process constitutes

the main overhead and it may be driven by a single processor in a multiprocessor system. A recursion-DAG may be used to reduce the division work, therefore speeding up the sequential execution of the problem division. Also a recursion-DAG may assist the parallelization process helping the efficient processor allocation to parallel function calls at run-time; for example, it may help reduce the number of process spawns, thus, initialization time and initialization communications.

### 2.1.1 Recursive-DAG, Related Work

Our approach has several similarities with approaches in two very active research areas: one is *self-applicable partial evaluation* and the other is *dynamic programming*.

Self-applicable partial evaluation is the problem of optimizing an algorithm when a partial number of arguments is known at compile time and, therefore, specializing a function, or the entire program, to partially precompute the result to the extent feasible at compile time. For references, see [30, 31] or a survey by Jones et al. [32]. Object-oriented class templates, and in particular function specialization in C++, are familiar examples of partial evaluations. Some general purpose compilers also apply partial evaluation for optimizations such as dead code elimination [33]. All authors propose an approach composed of two phases: a static phase and a dynamic phase. The static phase determines what can be computed at compile time, and what cannot be computed, the **residual**.

Our approach is also a combination of static and dynamic phases (or analyses). The static analysis takes the input program and annotates the formals parameters of function definitions so as to clearly mark the formals involved in the recursive division process only.

<sup>&</sup>lt;sup>1</sup> The dynamic analysis partially executes the program, and using the annotations, binds

<sup>&</sup>lt;sup>1</sup>Notice that other algorithms may deploy a few global variables to keep record of the decomposition process and they may use no auxiliary data structures such as a stack. First, this is not an example of *good* programming because the behavior of a function is not dictated by the values assigned to its interface. Second, and more importantly, all the problems presented in this work have a division work that cannot be executed correctly using only a fixed number of a few global variables.

function calls to nodes in the recursion DAG. When no argument values are known at compile time previous techniques are not applicable; however, our technique is applicable and enables us to precompute (at run time) data that will be used during the recursive algorithm execution; in practice, we *specialize* the computation of the recursive algorithm at run time.

In **dynamic programming**, there are basically two *philosophies*: function caching and incrementalization. Function caching is a top-down approach to solve a problem remembering the result of a function invocation and reusing this result when the function is invoked again with the same arguments. For example, Fibonacci number  $^2$  F(4) involves the computation of F(2) + F(1) + F(2). With function caching, the first invocation of F(2) is computed once, and the result is reused for the second invocation [34, 35, 36, 37]. While function caching may require an interpretive overhead to manage and store partial results, incrementalization is a bottom-up approach proposed to reduce or annihilate the overhead typical in function caching [38] reducing the working set of cached function results to a minimum –at any time– and having a fast access to them.

In general, dynamic-programming approaches are not applicable for matrix algorithms, because the final result of matrix algorithms is highly dependent on the contents of the input matrices (making reuse impossible). However, matrix algorithms have such regularity in their computation that some of the dynamic-programming techniques may be applied, at least in principle. In fact, our technique borrows the same basic ideas of function caching, especially in generating the recursion-DAG. Actually, we may see the recursion-DAG as the collection of all cached function-call results organized in a DAG. (However, we do not necessarily store any function return value). In this scenario, incrementalization is no better than function caching at the expense of a more complex design and implementation.

In addition, our approach is not meant for the conversion of loop nests to recursion

$<sup>^{2}</sup>F(n) = F(n-1) + F(n-2).$

[39] or vice versa [40], but it offers a means to speed up the conversion process and a quantitative measure of the overhead due to recursion. A compiler may then be able to make an informed choice between recursion or blocked instantiation. Our approach is not meant to optimize the function call mechanism (e.g., register minimization, solving allocation of the actuals-formals, inlining or recursion elimination, state elimination) because modern compiler technology already exists for these tasks and it is orthogonal to (and it could be use in combination with) our approach.

# 2.2 Recursive D&C Algorithms: Examples

We applied the concept of the recursion-DAG to four recursive algorithms. In practice, we analyzed the original recursive algorithm, we then determined the best division process, and we reorganized the algorithm in a such a way to use the recursion-DAG as guide-line for the division process and reduction of the division work. In these following sections, we introduce the applications investigated and the related work; in Chapter 4, we present our complete investigation.

We investigate a representative set of recursive algorithms to achieve the following goals: we show that recursion-DAG has practical uses for the developer and, especially, for design and implementation of linear algebra applications as recursive algorithms. As another result of our codes implementation, we show the positive effects of a balanced division process on performance for recursive algorithms: Indeed, a balanced division process produces an algorithm with a *more* predictable performance, a smaller overhead and a significative reduction of the division work.

In this thesis, we have turned our attention to the implementation features of LU-factorization and matrix multiply. In practice, we shall present an introduction here in Section 2.2.1 and 2.2.2, however we shall present a more detailed investigation in Section 4.1 and 4.2. We have also found that matrix multiply is also a basic computation in an

important application in graphs theory, **all-pair shortest paths** (APSP). We shall present an introduction in Section 2.2.3 and, in detail, our approach and results in Section 4.4.

### 2.2.1 LU-factorization

The first example of linear algebra application, where we used the recursion-DAG to model and to drive the computation, is LU-factorization with partial pivoting of non-singular matrices. The beauty of the LU-factorization with partial pivoting lies into its elegant blocked description [2, 5, 41]. In practice, matrix factorization is used to solve linear, dense and large systems as well as for the determination of the rank of a matrix; that is the number of independent rows/columns of a matrix. For example, in a system AX = B, where A and B are constant matrices and X is a matrix of free variables, we factorize matrix A as the product of one lower triangular matrix A by one upper triangular matrix A and A are system is reduced to two easier-to-solve triangular systems: A and A are A are A and A are A and A are A are A are A are A and A are A and A are A are A are A are A and A are A and A are A are A are A and A are A are A are A are A are A are A and A are A are A are A are A and A are A are

In practice, **partial pivoting** is a simple and efficient technique adopted to achieve numerical stability for most practical cases. Basically, one column of the matrix at a time, we seek for the matrix element with maximum absolute value in the leading column. We permute the matrix rows in order to set this matrix element as top element in the leading column. Finally, we execute the **Gaussian elimination** in such a way to reduce the element below the top element in the leading column to zero. We repeat the process until all elements below the major diagonal are reduced to zero. Partial pivoting assures a bounded value to the components of the lower triangular matrix **L** and, thus, a bounded error. Unfortunately, there are ill conditioned matrices, for which partial pivoting is not numerically stable, and the components of the factor **U** can become arbitrary large. To assure numerical stability for both matrix factors **L** and **U**, we may deploy a **complete pivoting**: it is a technique to

seek the element with the maximum in absolute value of the leading sub-matrix and perform both rows and columns permutation in order to have this element as a new pivot for the Gaussian elimination.