## Topics in Secure Embedded System Design

### Nachiketh Potlapally

A Dissertation

Presented to the Faculty

of Princeton University

in Candidacy for the Degree

of Doctor of Philosophy

Recommended for Acceptance by the Department of Electrical Engineering

January, 2008

$\odot$  Copyright 2008 by Nachiketh Potlapally. All rights reserved.

## Abstract

Pervasive networks have led to widespread use of embedded systems, like cell phones, PDAs, RFIDs etc., in increasingly diverse applications. Many of these embedded system applications handle sensitive data (e.g., credit card information on a mobile phone/PDA) or perform critical functions (e.g., medical devices or automotive electronics), and the use of security protocols is imperative to maintain confidentiality, integrity and authentication of these applications. Typically embedded systems have low computing power and finite energy supply based on a battery, and these factors are at odds with the computationally intensive nature of the cryptographic algorithms underlying many security protocols. In addition, secure embedded systems are vulnerable to attacks, like physical tampering, malware and side-channel attacks. Thus, design of secure embedded systems is guided by the following factors: small form factor, good performance, low energy consumption (and, thus, longer battery life), and robustness to attacks.

This thesis presents our work on tackling three issues in the design of secure embedded systems: energy consumption, performance and robustness to side-channel attacks. First, we present our work on optimizing the energy consumption of the widely employed secure sockets layer (SSL) protocol running on an embedded system. We discuss results of energy analysis of various cryptographic algorithms, and the manner in which this information can be used to adapt the operation of SSL protocol to save energy. Next, we present results of our experiments on optimizing the performance of Internet protocol security (IPSec) protocol on an embedded processor. Depending on the mode of operation, the IPSec computation is dominated by cryptographic or non-cryptographic processing. We

demonstrate how both these components of the IPSec protocol can be optimized by leveraging the extensible and configurable features of an embedded processor. Next, we introduce a satisfiability-based framework for enabling side-channel attacks on cryptographic software running on an embedded processor. This framework enables us to identify variables in the software implementations which result in the disclosure of the secret key used. Thus, security of software implementations can be improved by better protection of these identified variables. Finally, we conclude by introducing a novel memory integrity checking protocol that has much lower communication complexity than existing Merkle tree-based protocols while incurring a modest price in computation on the processor. This scheme is based on Toeplitz matrices, and can be very efficiently realized on embedded systems with hardware extensions for bit matrix operations.

# Acknowledgments

First and foremost, I would like to thank my advisors, Prof. Niraj Jha and Prof. Ruby Lee, for generously supporting me during my stay at Princeton. This thesis would not have been possible in its present form without their guidance, and the freedom they gave me in pursuing various ideas. The thesis bears marks of their meticulous attention to consistency and clarity of content. Any shortcomings in the thesis are entirely due to my oversight.

I have benefitted immensely with my association with Dr. Anand Raghunathan, Senior Research Staff Member, NEC Labs America who generously gave his time and suggestions which significantly influenced this thesis. I offer my sincere gratitude for everything he has done for me from the time I went to NEC labs as a novice researcher in 1999. My other collaborator at NEC Labs, Dr. Srivaths Ravi, helped me at various stages of my research with valuable advice, and his diligent attention to making me present various aspects of my research lucidly. I wholeheartedly thank him.

Taking courses in the Math and Computer Science departments was an intellectually rewarding experience, and a great pleasure. The credit for this largely goes to Prof. Avi Wigderson, Prof. Nicholas Pippenger, and Prof. Peter Sarnak. My stay at Princeton would have been much poorer without the company of some good friends I made along the way. Loganathan Lingappan acted as a sounding board for many of my ideas, and I enjoyed the discussions I had with him. Patrick Murphy was a wonderful roommate, and introduced me to the music of Bob Dylan with his "Dylan for Dummies" compilations. Sathyakama Sandilya helped me with my generals, and I have seen few as generous and modest as him. My first year at Princeton was made agreeable by my association with Subbu

Rajagopalan. Alex Kattamis kept days interesting with either politics or food or beverages or some combination of the three. Vassos Soteriou's quest for salvation made sure there were not many dull moments in the office. I would like to acknowledge Yogesh Mahajan, Pallav Gupta, and Gregory Nieberg. I thank all these people for the rich experience they afforded me.

She gently propped me up when I was down. She planted my feet firmly on the ground when I had my head in the clouds. She enriched my vocabulary with words like *riparian*, *eutrophication*, and *methanogenesis*. I cannot thank you enough for all the things you have done for me, Junu Shrestha. Finally, I humbly and respectfully thank my parents and grandmother for their selfless love and constant encouragement. They set aside personal desires so that I could achieve this. I remain indebted to them.

# Contents

| A            | bstra | uct                                                                 | iii  |

|--------------|-------|---------------------------------------------------------------------|------|

| $\mathbf{A}$ | ckno  | wledgments                                                          | v    |

| $\mathbf{C}$ | ontei | nts                                                                 | viii |

| Li           | st of | Figures                                                             | xii  |

| Li           | st of | Tables                                                              | xv   |

| 1            | Inti  | roduction                                                           | 1    |

|              | 1.1   | Threats and security protocols                                      | 2    |

|              | 1.2   | Secure embedded systems                                             | 6    |

|              | 1.3   | Challenges of secure embedded systems                               | 8    |

|              | 1.4   | Dissertation contributions                                          | 10   |

| 2            | Rel   | ated Work                                                           | 12   |

|              | 2.1   | Energy consumption of security protocols in embedded systems        | 12   |

|              | 2.2   | Performance of security protocols in embedded systems               | 14   |

|              | 2.3   | Side-channel attacks on embedded systems                            | 18   |

| 3            | Ene   | ergy Analysis of Security Protocols and Cryptographic Algorithms or | n    |

|              | an I  | Embedded System                                                     | 28   |

|              | 3.1   | Introduction                                                        | 29   |

|   | 3.2 | Motiva   | ation                                                           | 31        |

|---|-----|----------|-----------------------------------------------------------------|-----------|

|   |     | 3.2.1    | The impact of security on battery life: An illustration         | 31        |

|   |     | 3.2.2    | Energy-efficient security protocols                             | 33        |

|   | 3.3 | Prelin   | ninaries                                                        | 35        |

|   |     | 3.3.1    | Basic security terminology                                      | 35        |

|   |     | 3.3.2    | An example security protocol: SSL                               | 36        |

|   | 3.4 | Exper    | imental setup                                                   | 38        |

|   | 3.5 | Exper    | imental results                                                 | 39        |

|   |     | 3.5.1    | Energy analysis of cryptographic algorithms                     | 39        |

|   |     | 3.5.2    | Energy analysis of the SSL protocol                             | 51        |

|   | 3.6 | Chapt    | er summary                                                      | 67        |

| 4 | Opt | timizin  | g IPSec Protocol Execution by Extending and Configuring a       | ın        |

|   | Em  | bedded   | d Processor                                                     | 69        |

|   | 4.1 | Introd   | uction                                                          | 70        |

|   |     | 4.1.1    | Contribution of this work                                       | 72        |

|   | 4.2 | IPSec    | protocol                                                        | 74        |

|   | 4.3 | Motiva   | ation                                                           | 76        |

|   | 4.4 | Archit   | sectural exploration and performance analysis                   | 78        |

|   |     | 4.4.1    | Architectural design space                                      | 79        |

|   |     | 4.4.2    | IPSec performance analysis and optimization methodology         | 79        |

|   |     | 4.4.3    | Tuning IPSec using extensible options                           | 83        |

|   |     | 4.4.4    | Impact of configurable options and interplay with extensibility | 93        |

|   |     | 4.4.5    | Summary                                                         | 99        |

|   | 4.5 | Chapt    | er summary                                                      | 100       |

| 5 | Sat | isfiabil | ity-based Side-channel Attack Framework for Embedded Cryp       | <b>)-</b> |

|   |     |          | Software                                                        | 101       |

|   | 5 1 | Introd   | uetion                                                          | 102       |

|   |              | 5.1.1                                                                | Work contributions                                                                                                                                                                                                            | 104                                                  |

|---|--------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

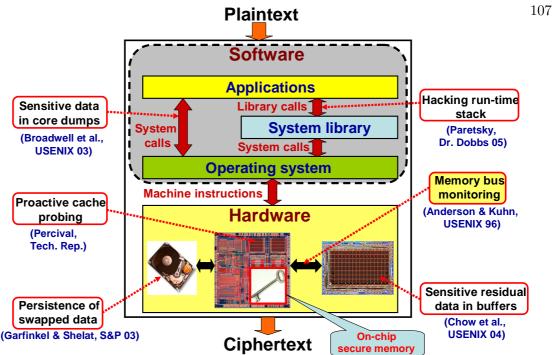

|   | 5.2          | Motiva                                                               | ation                                                                                                                                                                                                                         | 105                                                  |

|   |              | 5.2.1                                                                | Leakage of software variable values                                                                                                                                                                                           | 106                                                  |

|   |              | 5.2.2                                                                | Proactive memory bus monitoring-based leakage                                                                                                                                                                                 | 108                                                  |

|   | 5.3          | SAT f                                                                | ramework for enabling side-channel attacks                                                                                                                                                                                    | 112                                                  |

|   |              | 5.3.1                                                                | Overview of the proposed framework                                                                                                                                                                                            | 112                                                  |

|   |              | 5.3.2                                                                | SAT solver algorithm                                                                                                                                                                                                          | 115                                                  |

|   |              | 5.3.3                                                                | Boolean formulation of a cryptographic algorithm                                                                                                                                                                              | 116                                                  |

|   | 5.4          | Exper                                                                | imental results                                                                                                                                                                                                               | 122                                                  |

|   |              | 5.4.1                                                                | Experimental setup                                                                                                                                                                                                            | 122                                                  |

|   |              | 5.4.2                                                                | Cryptanalysis of DES                                                                                                                                                                                                          | 124                                                  |

|   |              | 5.4.3                                                                | Cryptanalysis of 3DES                                                                                                                                                                                                         | 128                                                  |

|   |              | 5.4.4                                                                | Cryptanalysis of AES                                                                                                                                                                                                          | 130                                                  |

|   |              | 5.4.5                                                                | Observations                                                                                                                                                                                                                  | 130                                                  |

|   |              |                                                                      |                                                                                                                                                                                                                               |                                                      |

|   | 5.5          | Chapt                                                                | er summary                                                                                                                                                                                                                    | 131                                                  |

| 6 |              | -                                                                    | er summary                                                                                                                                                                                                                    |                                                      |

| 6 | Ver          | -                                                                    |                                                                                                                                                                                                                               |                                                      |

| 6 | Ver          | ifying<br>eries                                                      |                                                                                                                                                                                                                               | r                                                    |

| 6 | Ver:         | ifying<br>eries                                                      | Integrity of Data Stored in Untrusted Memory with Fewer                                                                                                                                                                       | r<br>132                                             |

| 6 | Ver:         | ifying<br>eries<br>Introd                                            | Integrity of Data Stored in Untrusted Memory with Fewer                                                                                                                                                                       | r<br>1 <b>32</b><br>133                              |

| 6 | Ver<br>Que   | ifying eries Introd 6.1.1 6.1.2                                      | Integrity of Data Stored in Untrusted Memory with Fewer duction                                                                                                                                                               | r<br>1 <b>32</b><br>133                              |

| 6 | Ver<br>Que   | ifying eries Introd 6.1.1 6.1.2                                      | Integrity of Data Stored in Untrusted Memory with Fewer fuction                                                                                                                                                               | r<br>132<br>133<br>138<br>140                        |

| 6 | Ver<br>Que   | ifying eries Introd 6.1.1 6.1.2 Definit 6.2.1                        | Integrity of Data Stored in Untrusted Memory with Fewer function                                                                                                                                                              | 132<br>133<br>138<br>140<br>142                      |

| 6 | Ver: Que 6.1 | ifying eries Introd 6.1.1 6.1.2 Definit 6.2.1                        | Integrity of Data Stored in Untrusted Memory with Fewer fuction                                                                                                                                                               | 132<br>133<br>138<br>140<br>142<br>142               |

| 6 | Ver: Que 6.1 | ifying eries Introd 6.1.1 6.1.2 Defini 6.2.1 Propo                   | Integrity of Data Stored in Untrusted Memory with Fewer function                                                                                                                                                              | 132<br>133<br>138<br>140<br>142<br>142               |

| 6 | Ver: Que 6.1 | ifying eries Introd 6.1.1 6.1.2 Defini 6.2.1 Propo 6.3.1             | Integrity of Data Stored in Untrusted Memory with Fewer fuction                                                                                                                                                               | 132<br>133<br>138<br>140<br>142<br>145<br>145        |

| 6 | Ver: Que 6.1 | ifying eries Introd 6.1.1 6.1.2 Defini 6.2.1 Propo 6.3.1 6.3.2 6.3.3 | Integrity of Data Stored in Untrusted Memory with Fewer fuction.  Contribution of the work  Related work  tions.  Basic model and definitions  sed memory integrity verification technique  UPDATE() routine  CHECK() routine | 132<br>133<br>138<br>140<br>142<br>145<br>145<br>149 |

| 7  | Conclusions and Future Work | 156 |

|----|-----------------------------|-----|

| D. | eferences                   | 150 |

| Re | eierences                   | 158 |

# List of Figures

| 2.1  | DPA attack                                                                          | 22 |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | Last round of DES                                                                   | 23 |

| 2.3  | Last round of DES                                                                   | 25 |

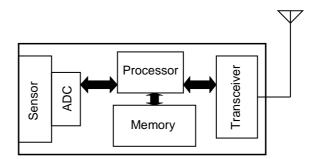

| 3.1  | Architecture of a sensor node                                                       | 32 |

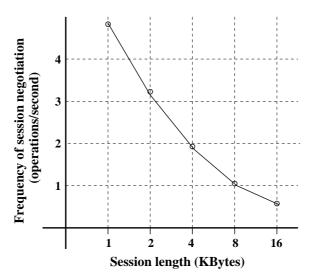

| 3.2  | Frequency of session set-up as a function of session length $\dots \dots \dots$ .   | 33 |

| 3.3  | Effect of encryption on battery life                                                | 34 |

| 3.4  | The SSL protocol, with an expanded view of the SSL record protocol                  | 37 |

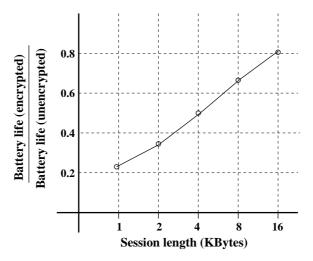

| 3.5  | Secure client-server configuration and the energy measurement testbed               | 39 |

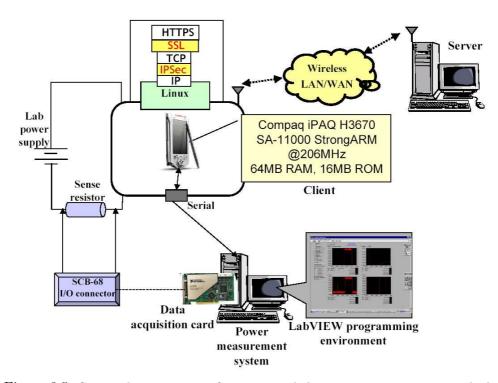

| 3.6  | Energy consumption data for various symmetric ciphers                               | 44 |

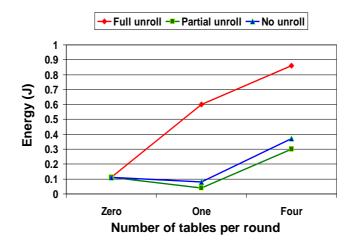

| 3.7  | Energy consumption of AES as a function of table look-ups                           | 48 |

| 3.8  | Comparison of processor and memory energy consumption in (a) full unrolling and     |    |

|      | (b) partial unrolling                                                               | 49 |

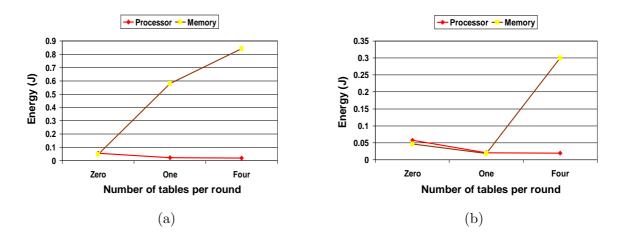

| 3.9  | Energy consumption versus security trade-off for RC5 encryption                     | 50 |

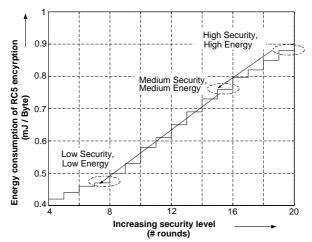

| 3.10 | Sequence of client-side operations for an SSL session                               | 52 |

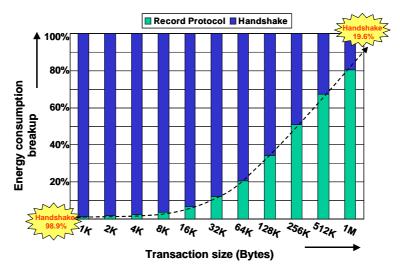

| 3.11 | Variation of energy consumption contributions from the SSL handshake and record     |    |

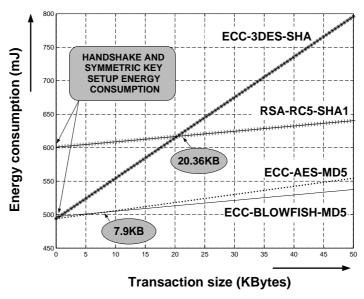

|      | stages with increasing transaction sizes                                            | 53 |

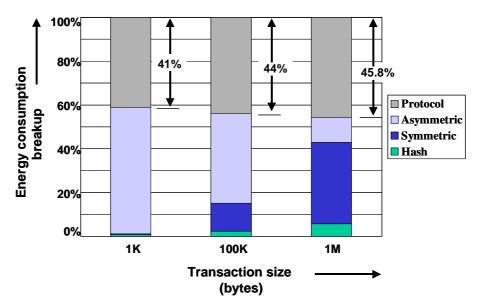

| 3.12 | Break-up of SSL energy consumption into cryptographic and non-cryptographic         |    |

|      | components                                                                          | 54 |

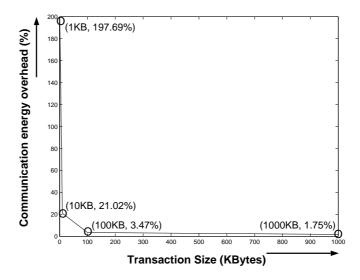

| 3.13 | Percentage communication energy overhead of SSL usage for varying transaction sizes | 59 |

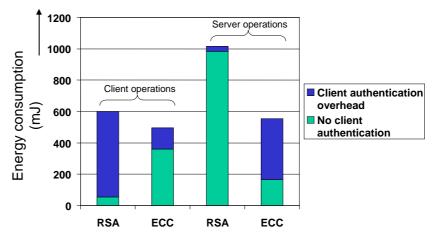

| 3.14 | Energy consumption for client and server operations in SSL handshake under the        |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | presence or absence of client authentication                                          | 60  |

| 3.15 | The impact of cipher suite selection on energy consumption during the SSL hand-       |     |

|      | shake and record stages                                                               | 62  |

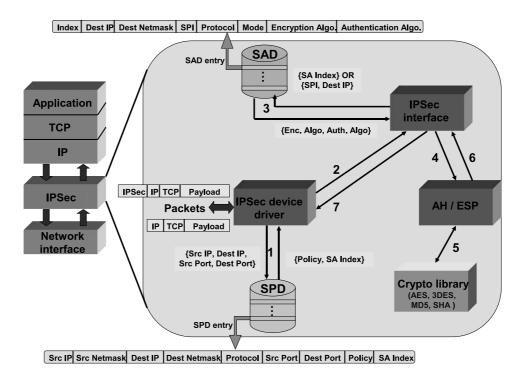

| 4.1  | Steps in IPsec processing                                                             | 75  |

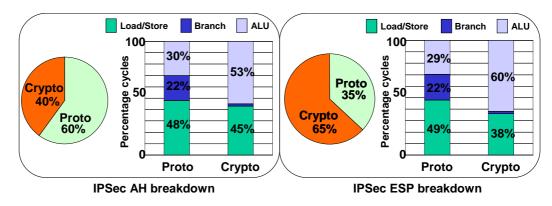

| 4.2  | Breakdown of IPSec processing into cryptographic and protocol components, and         |     |

|      | into various instruction categories                                                   | 76  |

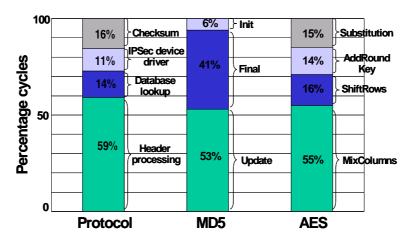

| 4.3  | Contributions of core functions in cryptographic and protocol components of IPSec     |     |

|      | processing                                                                            | 78  |

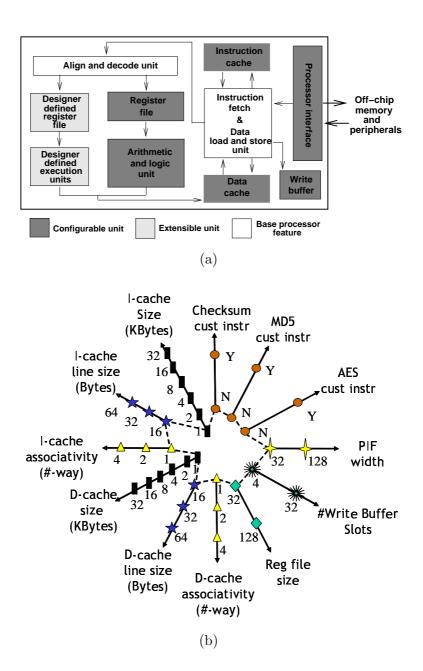

| 4.4  | (a) Xtensa's architectural features, and (b) design space of configurable and exten-  |     |

|      | sible options explored in this work                                                   | 80  |

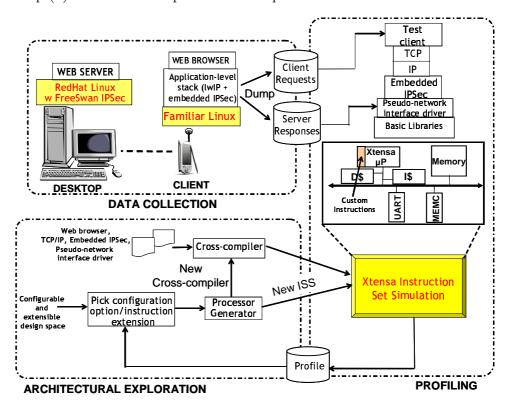

| 4.5  | The three phases of our design methodology: data collection, performance profiling    |     |

|      | and architectural exploration                                                         | 81  |

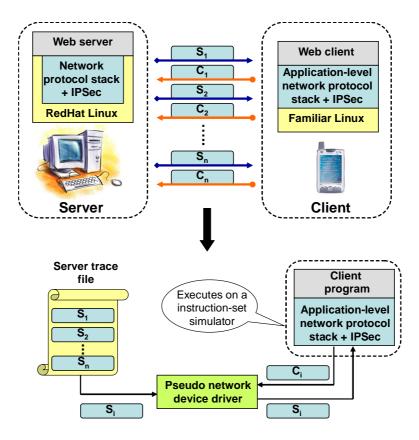

| 4.6  | Profiling using the pseudo device driver                                              | 84  |

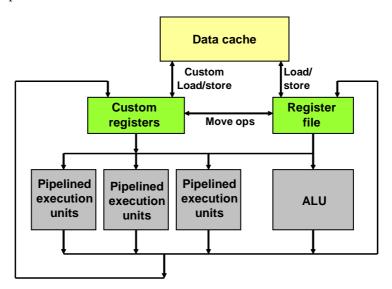

| 4.7  | Datapath of an extensible processor                                                   | 85  |

| 4.8  | Software implementation of the checksum operation (a) without, and (b) with cus-      |     |

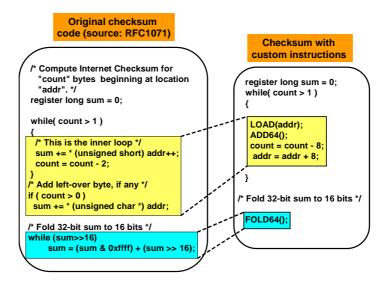

|      | tom instructions                                                                      | 86  |

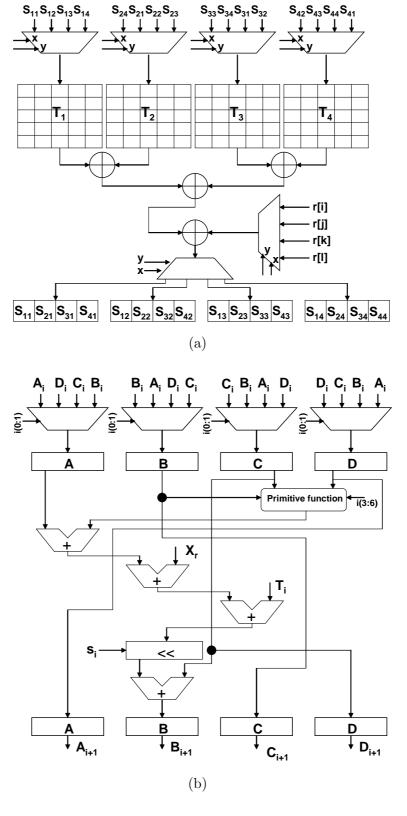

| 4.9  | Functional view of custom instructions (a) ENC_ROUND, and (b) MD5_ITERATIO            | N   |

|      | in AES and MD5, respectively                                                          | 90  |

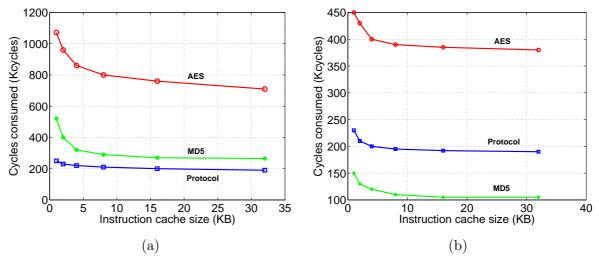

| 4.10 | Effect of instruction cache size on IPSec performance in (a) the absence and (b)      |     |

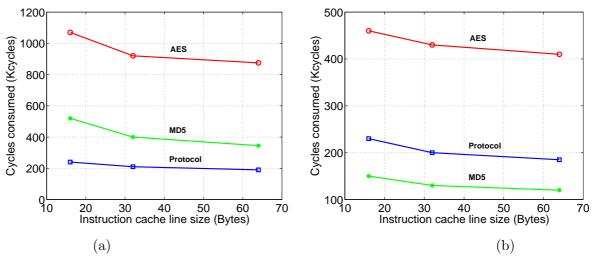

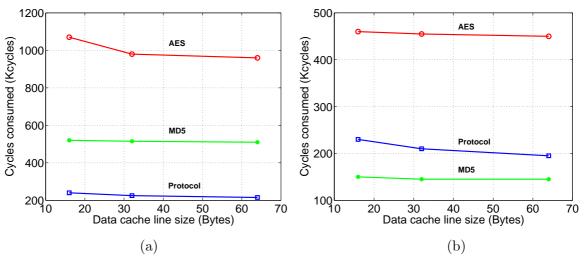

|      | presence of extensible options                                                        | 94  |

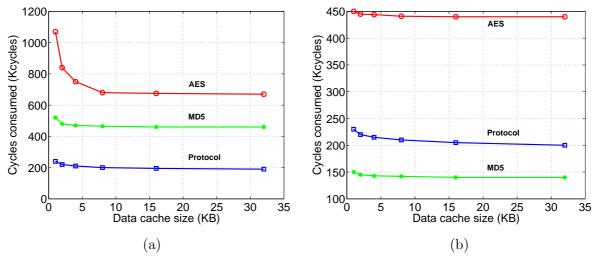

| 4.11 | Effect of data cache size on IPSec performance in (a) the absence and (b) presence    |     |

|      | of extensible options                                                                 | 95  |

| 4.12 | Effect of instruction cache line size on IPSec performance in (a) the absence and (b) |     |

|      | presence of extensible options                                                        | 96  |

| 4.13 | Effect of data cache line size on IPSec performance in (a) the absence and (b)        |     |

|      | presence of extensible options                                                        | 97  |

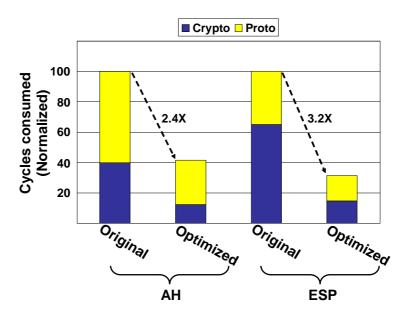

| 111  | Speed up of IDSee AH and ESD modes                                                    | 100 |

| 5.1  | Leakage of software variable values in hardware-software systems                                      | 107 |

|------|-------------------------------------------------------------------------------------------------------|-----|

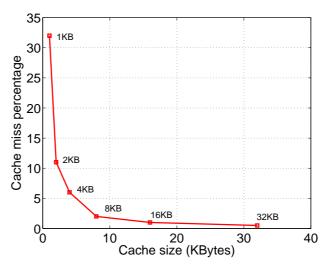

| 5.2  | Probability of DES intermediate value exposure as a function of cache size                            | 109 |

| 5.3  | Algorithm for collecting intermediate values of cryptographic computation .                           | 110 |

| 5.4  | Algorithm for flushing intermediate values from data cache $\dots \dots$ .                            | 111 |

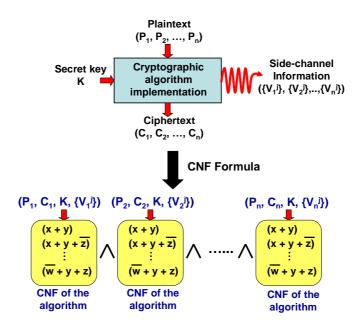

| 5.5  | SAT formulation for side-channel cryptanalysis                                                        | 113 |

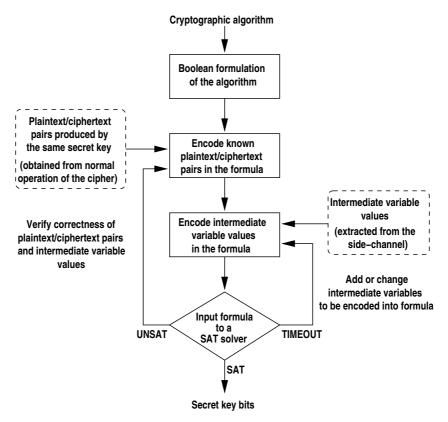

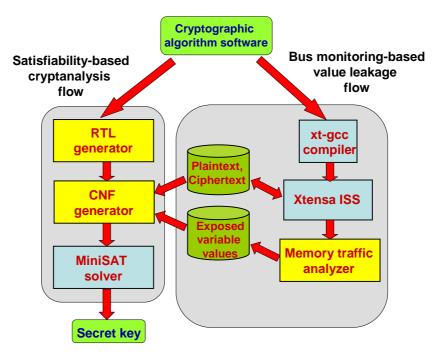

| 5.6  | High-level view of the proposed SAT-based framework                                                   | 114 |

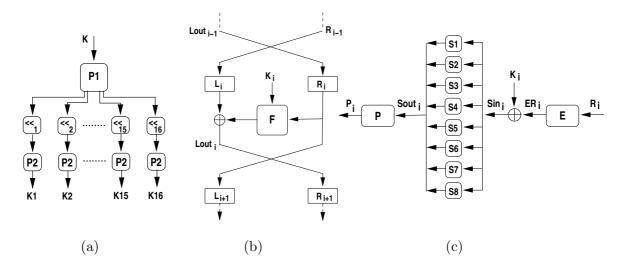

| 5.7  | Functional view of DES encryption: (a) round key generation, (b) round transfor-                      |     |

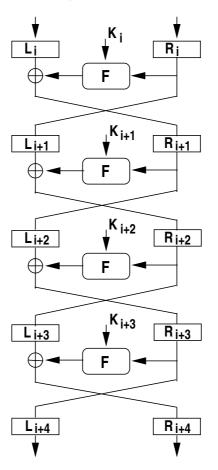

|      | mation, and (c) $F$ function used in the round transformation                                         | 117 |

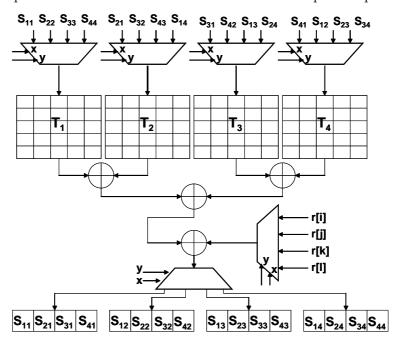

| 5.8  | AES round transformation                                                                              | 121 |

| 5.9  | Experimental setup                                                                                    | 123 |

| 5.10 | DES structure illustrating invariant rules                                                            | 125 |

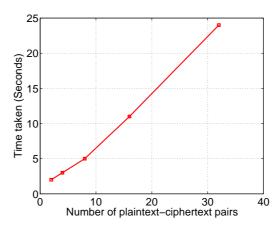

| 5.11 | Time to compute the secret key with the value of variable $L_{16}$                                    | 127 |

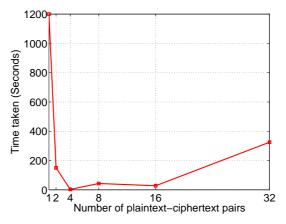

| 5.12 | Time taken to compute the secret key with the values of variables $\mathcal{L}_5$ and $\mathcal{L}_6$ | 128 |

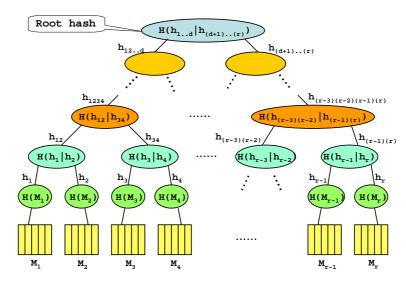

| 6.1  | Integrity verification using Merkle tree                                                              | 135 |

|      |                                                                                                       |     |

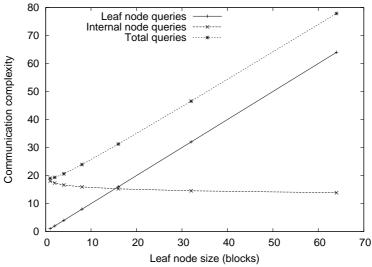

| 6.2  | Merkle tree communication complexity                                                                  | 137 |

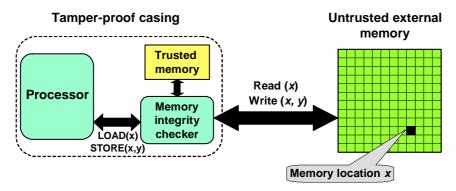

| 6.3  | Memory integrity checker                                                                              | 143 |

# List of Tables

| 2.1 | Comparision of features of some popular secure embedded processors                    | 16  |

|-----|---------------------------------------------------------------------------------------|-----|

| 3.1 | Energy cost of digital signature algorithms                                           | 41  |

| 3.2 | Energy cost of key exchange algorithms                                                | 42  |

| 3.3 | Energy consumption characteristics of hash functions                                  | 43  |

| 3.4 | Energy costs of AES variants                                                          | 50  |

| 3.5 | Multiple levels of cryptanalytic difficulty in RC5 [1] $\dots \dots \dots$ .          | 51  |

| 3.6 | Energy consumption of RC5 key setup                                                   | 51  |

| 3.7 | Profile of the data exchanged between the client and server in an SSL connection $$ . | 56  |

| 3.8 | Communication energy overhead in the client due to SSL security processing $$         | 58  |

| 3.9 | Key sizes for the two security levels                                                 | 63  |

| 4.1 | Parameters examined in profiling                                                      | 83  |

| 4.2 | Effect on I-cache size on performance                                                 | 94  |

| 4.3 | Effect on D-cache size on performance                                                 | 95  |

| 4.4 | Effect on I-cache line size on performance                                            | 97  |

| 4.5 | Effect on D-cache line size on performance                                            | 98  |

| 4.6 | Performance speedup of IPSec due to extensibility and configurability                 | 99  |

| 5.1 | Results of the Boolean formulation                                                    | 122 |

| 5.2 | 3-CNF DES formula                                                                     | 131 |

| 6.1 | Comparison of space and communication complexity                                      | 151 |

### Chapter 1

### Introduction

Security is an important concern in networked applications due to increasingly sensitive data being exchanged on the computer networks. This concern necessitates the use of security protocols to protect the sensitive data from unauthorized snooping or manipulation by adversaries. A significant fraction of the devices making up present-day networks are embedded systems which are marked by low processing power and finite energy supply derived from a battery. However, existing security protocols are computationally intensive, and executing them on resource-constrained embedded systems leads to the problem of reduced performance and battery life. In addition, many embedded systems are especially susceptible to a type of non-invasive attacks called side-channel attacks. This thesis proposes techniques for improving the performance, battery life and robustness to side-channel attacks of secure embedded systems.

This chapter begins with an introduction to various security threats present in computer networks, and the security protocols which are formulated to counter these threats in Section 1.1. Section 1.2 motivates the need for secure embedded systems. Section 1.3 discusses the challenges involved in designing secure embedded systems, and provides the motivation for the thesis. Finally, the chapter concludes with Section 1.4 which gives the outline of chapters of this thesis.

### 1.1 Threats and security protocols

Data being exchanged on computer networks are open to a variety of threats from unauthorized parties, collectively known as adversaries. The presence of high-speed and large-throughput networks has enabled the migration of many important applications, like voting, filing taxes, banking, heath monitoring, etc., online. The high value of the data being exchanged by these applications has made it an attractive target for attacks by adversaries motivated by commercial gain, fame for notoriety and other factors. According to a CERT report on electronic crime [2], 150 million dollars were lost due to electronic attacks on the organizations in spite of 62% of the surveyed organizations refusing to disclose their losses due these attacks. Thus, it is important to employ security mechanisms in order to protect electronic transactions. Security refers to techniques employed to prevent adversaries from carrying out any unpermitted action which affects the data being exchanged between legitimate parties in an unauthorized manner. Usually, in the security literature, any two legitimate entities interacting with each other are referred to as Alice and Bob, and an adversary is called Eve. We adopt the same convention in rest of this chapter. Data exchanged on the computer networks are susceptible to the following adversarial threats:

- 1. Eve observes data being exchanged between Alice and Bob with the intention of finding out the content.

- 2. Eve modifies communication between Alice and Bob.

- 3. Eve impersonates as Alice to Bob, or as Bob to Alice.

- 4. Eve disrupts the network so that Alice and Bob cannot communicate with each other.

We employ security protocols in order to counter the above-mentioned threats. A security protocol is a sequence of steps, followed by two or more parties, such that certain security objectives are satisfied [3]. A security objective is formulated to either counter one of the threats listed above, or to ensure that interactions between legitimate parties satisfy some requirements. Following are the common security objectives which need to be satisfied by

#### security protocols:

- 1. Confidentiality (or secrecy): Information is not disclosed to unauthorized entities.

- 2. Integrity: Any unauthorized manipulation of data can be detected.

- 3. Authentication: An unauthorized entity should not be able to pose as a legitimate entity.

- 4. Non-repudiation: An authorized entity should not be able to disown its legitimate communication with other authorized entities.

- 5. Availability: A system should be usable on demand by an authorized entity.

In the list given above, non-repudiation (4) is the only property which does not involve an adversary, and is essential for upholding the validity of legitimate online transactions. Typically, security protocols are built using cryptographic algorithms to satisfy confidentiality (1), integrity (2), authentication (3) and non-repudiation (4), while availability (5) is made possible through the use of access control security mechanisms. In general, it is expensive to design security protocols which can counter all the possible threats. Moreover, higher the complexity of a security protocol, greater are the chances of introducing design flaws into the protocol implementation, and thereby creating inadvertent security vulnerabilities. Therefore, in practice we adopt a application-specific threat model approach. In this approach, we begin by defining a reasonable threat model comprising a set of threats which are relevant to the target application. Next, we identity the appropriate security objectives needed to counter the threats listed in the threat model, and then proceed to define a security protocol that achieves all the chosen objectives. Most security protocols are aimed at protecting data while being transmitted over communication channels. However, that alone is not sufficient, and we need to protect the end points too. By end points, we refer to computing devices that Alice uses to generate her data before she sends it over to Bob, and likewise for Bob. Attacks on these devices have the goal of retrieving sensitive material, like cryptographic keys, stored in the device, and these attacks are either invasive or non-invasive. Invasive attacks consist of physically probing the internal circuitry of a device in order to extract the sensitive material, while non-invasive techniques consist of software attacks (using viruses, worms, etc) and attacks based on the statistical analysis of operational characteristics of the device to extract secret information. Non-invasive attacks of the latter kind which are based on analyzing the device operational characteristics to extract the secret key are called side-channel attacks. Examples of operational characteristics which formed the basis of successful side-channel attacks include timing information, power dissipation, electromagnetic radiation, and device operation in the presence of faults. Side-channel attacks are quite dangerous because of two reasons. First, they do not cause any damage to the device, and thus the probability of escaping detection is very high, and second, they provide a tractable way of breaking algorithms with very high theoretical cryptanalytic strength. The nature of embedded systems makes them a target of effective side-channel attacks. The portable nature of embedded devices makes it easier for an adversary to take possession of the device temporarily in order to record operational characteristics for various inputs, and perform the statistical analysis off-line. Also, most embedded systems are designed for specific applications, and the resulting simpler circuitry facilitates effective side-channel attacks on these devices. Thus, securing electronic data against adversaries constitutes two parts: first, improve the robustness of end systems against attacks aimed at securing the sensitive information, and formulate security protocols to protect data while in transmission between end points.

The steps of a security protocol are implemented using cryptographic algorithms. A cryptographic algorithm is a mathematical function that implements encryption and decryption parameterized on a key. One of the basic assumptions of modern cryptography is that security of a cryptographic algorithm must be based only on the secrecy of the key used, and not in keeping the algorithm secret. This principle is called Kerchoff's principle [4]. For any algorithm, the total number of key values possible is referred to as the keyspace. Thus, Kerchoff's principle dictates that the key should be so chosen that given any input and the corresponding output of a cryptographic algorithm, it should be computationally

infeasible for an adversary to search the entire keyspace in order to find the correct key. Let M be the plaintext message, C be the corresponding ciphertext, and K be the key used to map M to C using encryption function E(). Then, encryption is formally denoted as,  $C = E_K(M)$  where  $E_K()$  represents encryption function E() parameterized on key K. Similarly, if  $D_K()$  represents the decryption function D() parameterized on key K, then, we have  $M = D_K(C)$ . For any key K and plaintext M, the encryption function E() and decryption function D() satisfy the property that  $D_K(E_K(M)) = M$ . If the constructions of functions E() and D() satisfy Kerchoff's principle, then, it will be computationally infeasible for an adversary to find the value of key K used to map M to C using  $C = E_K(M)$  given that E(), D(), M, and C are known. Cryptographic algorithms can be divided into the following three types:

- Symmetric algorithms: In these algorithms, encryption and decryption processes use the same key which has to be kept secret. Therefore, these algorithms are also known as secret-key algorithms. They are primarily used for realizing confidentiality. If Alice and Bob wish to encrypt their communication using a symmetric algorithm, then they have to agree upon a key before they start communicating. The process of securely agreeing upon a secret key in the presence of adversaries can be quite challenging.

- Asymmetric algorithms: In these algorithms, encryption and decryption functions use different keys such that the key used for encryption is made public and the key used for decryption is kept secret. The encryption and decryption keys are called public and private keys, respectively. These algorithms are also known as public-key algorithms, and they are primarily used for implementing authentication and non-repudiation. Let  $K_A^{public}$  and  $K_A^{private}$  be the public and private keys of Alice, respectively. For any plaintext M, the public and private keys satisfy the property that  $M = D_{K_A^{private}}(E_{K_A^{public}}(M))$ . Alice publishes key  $K_A^{public}$  and keeps key  $K_A^{private}$  secret. If Bob wishes to send an encrypted form of message M to Alice, he computes ciphertext  $C = E_{K_A^{public}}(M)$  and sends it to Alice. Since Alice alone knows her private key, she obtains message M by computing  $M = D_{K_A^{private}}(C)$ . When Alice wishes

to authenticate herself, she derives a signature S by encrypting a short message M with her private key,  $K_A^{private}$ , i.e.,  $S = E_{K_A^{private}}(M)$ . Anyone can verify Alice's signature S by decrypting it with her public key,  $K_A^{public}$ , and comparing the result with M. Since only Alice knows her private key, successful decryption implies that Alice generated the signature S.

• Hash algorithms: Hash algorithms take an arbitrary-sized input and map it to a fixed-length hash value using a efficiently computable compression function. The hash functions are primarily used to check for data integrity, and sometimes employed for authentication when the hash function is parameterized on a key (known as hash message authentication code). It is absolutely necessary that a cryptographic hash function satisfy three properties, namely:  $pre-image\ resistance$  (meaning it is computationally infeasible to invert a hash function),  $second\ pre-image\ resistance$  (which implies that given message M and its corresponding hash value h, it is infeasible to find another message  $M' \neq M$  that maps to the same hash value h), and  $collision\ resistance$  (which says that it is intractable to find two messages M and M' that map to the same hash value).

### 1.2 Secure embedded systems

An embedded system is defined as a computing platform which performs a limited set of functions using a combination of hardware and software under real-time constraints. Development of embedded systems has transformed the computing paradigm from a desktop and server-dominated scenario to a distributed computing model comprising lots of embedded systems distributed within the environment, taking information as input and performing some processing on the data before transmitting them to the centralized servers. Examples of these embedded systems include sensor nodes gathering sense data about their environment and transmitting it to a central data aggregation node in a distributed sensor network, Internet connectivity enabled handhelds used by users to access their online bank accounts,

etc. The versatility of this computing model coupled with the widespread deployment of high-bandwidth wireless networks has led to many important applications executing on desktops to be ported to embedded systems. According to a recent survey, the amount of retail commercial transactions using smartcard-based embedded systems is projected to reach \$2 billion by 2008 [5]. Embedded systems have a diverse array of system characteristics and are being increasingly deployed in applications which handle sensitive data. Examples of some of these applications are given below:

- Machine-readable travel document: An Epassport has a radio frequency identification (RFID) tag, containing important personal information of the holder of the passport, embedded into it. The RFID tag interacts with Epassport readers installed in the airports to automatically verify the holder of the passport. Typical system features of a RFID tag are:

- 1.28-1.92MHz processor.

- 128-512 bit ROM.

- 32-128 bit RAM.

- Around 60000 transistors.

- Battery energy supply (for an active tag).

- Epayment: Europay, Visa and Mastercard (EMV) compliant smartcard is an embedded device that enables users to perform highly secure retail transactions. In order to authorize payment for a sale, the smartcard information is verified by a point of sale reader installed in the commercial establishment. Typical system features of a smartcard are:

- 66-100MHz processor.

- 240KB ROM.

- 16KB RAM.

- -500000-1000000 transistors.

- Battery energy supply (for an active card).

- Mobile brokerage: Embedded devices, like PDAs and cell-phones, are used being used

to manage portfolios with help of software, like Microsoft Money. In these applications,

the embedded devices carry transactions with a central server through the Internet.

Typical characteristics of the PDA-like devices are:

- 133-300MHz processor.

- 16MB ROM.

- 64MB Flash RAM.

- > 5-10 million transistors.

- Battery energy supply.

In all the above applications, embedded systems process sensitive information. Therefore, we need to deploy security protocols on these systems to protect the information from unauthorized disclosure and tampering. As mentioned in the previous section, we need security mechanisms to not only protect data which are being transmitted by the embedded device, but, also protect the sensitive information stored on the device. Also, from the list of typical system characteristics of embedded systems listed above, we can see that the embedded systems have the following constraints: low processing capability, limited memory, and finite battery-derived energy supply. However, security protocols are computationally intensive, and deploying them on resource-constrained embedded systems without appreciably degrading their performance is a challenging task. In the next section, we will elaborate more on the challenges involved in the design of secure embedded systems.

### 1.3 Challenges of secure embedded systems

In the last section, we saw that embedded devices have inherent operating constraints of low processing power, small memory storage, and limited energy supply. In addition, embedded systems are marked by portability and a small form factor. These unique traits of embedded systems make it especially challenging to realize security functionality in embedded systems, as explained below:

- Reduced performance: Cryptographic algorithms, which are one of the building blocks of security protocols, are computationally intensive. Executing security protocols on low-end processors present in embedded systems drastically degrades their performance. For example, the Intel SA-1100 embedded processor offers 150 million instructions per second (MIPS) of computational power at 133MHz. Cryptographic algorithms, when 3DES and SHA are used to provide confidentiality and data integrity, respectively, at a data rate of 2Mbps, require 130 MIPS, leaving only 20 MIPS for non-cryptographic processing. Thus, security protocols degrade performance of embedded systems [6].

- Short battery life: The computationally intensive nature of cryptographic algorithms results in an appreciable reduction in the battery life of embedded systems when security protocols are used. Consider a Sensoria wireless sensor node equipped with a Motorola DragonBall MC68328 processor used in an application where it senses data and transmits them to a centralized node. In sensor nodes, communication is the most expensive operation with respect to energy consumption and the Sensoria node requires 21.5 mJ to transmit a bit at a data rate of 10 kbps. If the RSA algorithm is used for authenticating the node, it requires an additional 42 mJ/bit. This results in the node battery with a capacity of 26kJ running out more than twice as fast as when there is no security [7].

- Vulnerability to attacks: The small form factor and portable nature of embedded systems makes them especially susceptible to side-channel attacks. In order to launch a side-channel attack, an adversary first needs to record information, like power, timing, electromagnetic emission, etc., while the device is performing computations parameterized on the secret information, and later, analyze the recorded information using statistics to extract the secret information. The portable quality of the embedded

device together with the non-invasive nature of side-channel attack make it easier to compromise the secret information and escape detection.

Thus, designing secure embedded systems has three objectives, namely, maintaining good performance, ensuring a sufficiently long battery life, and making them robust to known side-channel attacks.

#### 1.4 Dissertation contributions

This dissertation takes steps in the direction of building secure embedded systems that have good performance, whose battery life is sufficiently long, and those that are robust to non-invasive attacks, like side-channel attacks. The contribution made by this dissertation are as follows:

- Provide a comprehensive analysis of energy consumption characteristics of cryptographic algorithms on a handheld. Based on this analysis, protocol-level energy optimizations are suggested for the secure sockets layer (SSL) protocol.

- Give an in-depth analysis of the performance of Internet security (IPSec) protocol execution on an embedded processor, in terms of cryptographic and protocol components. And, optimize both the cryptographic and protocol components of IPSec execution through the use of extensibility and configurability features of an embedded processor.

- Introduce a new side-channel attack framework on cryptographic software running on an embedded processor using a Satisfiability solver. Using this framework, intermediate variables in computation of popular cryptographic algorithms are identified which would result in the secret key being leaked.

The dissertation is organized as follows. Related work is described in Chapter 2. Chapter 3 describes the results on energy analysis of cryptographic algorithms, and ways of

optimizing the energy consumption of the SSL protocol through protocol-level optimizations. Chapter 4 describes the performance optimization of IPSec protocol execution on an embedded processor by using its configurable and extensible features to target non-cryptographic and cryptographic computations, respectively. Chapter 5 presents details of the novel SAT-based side-channel attack framework, and demonstrates it in the context of popular cryptographic algorithms DES, 3DES and AES. Chapter 6 gives the details of a novel memory integrity checking protocol that makes much fewer additional queries to the external memory than existing methods based on Merkle trees. Finally, we conclude with a summary of the dissertation and ideas for future work in Chapter 7.

### Chapter 2

# Related Work

In this chapter, we survey existing literature related to issues involved in implementing security functionality in embedded systems. We restrict ourselves to three aspects of embedded system security, namely: impact of security on the battery life, the performance of secure embedded systems, and their susceptibility to side-channel attacks. We begin by discussing works which analyze the energy cost of embedded security processing in Section 2.1. Section 2.2 surveys the works dealing with improving the performance of security processing on embedded systems. Section 2.3 gives a discussion of the literature on side-channel attacks on embedded systems.

# 2.1 Energy consumption of security protocols in embedded systems

Most embedded systems derive their energy supply from a battery. Research has shown that the battery capacity is growing at a much slower rate than the energy requirement of the newer applications, resulting in a battery gap [8]. Security protocols and the underlying cryptographic algorithms impose significant computational requirements, and introducing security functionality into embedded systems further exacerbates the existing battery gap. The shortened battery life of secure embedded systems has undesirable consequences for the

usability of embedded systems. This observation has motivated researchers to investigate energy-efficient ways of implementing security functionality in embedded systems.

The work by Carmen et al. [7] was one of the first to study the energy consumption of cryptographic algorithm execution on embedded systems. Based on analytical estimation of the number of operations involved in different cryptographic algorithms, they computed energy consumption values of some asymmetric, symmetric, and hash algorithms on various popular embedded processors. This information was used to evaluate the energy efficiency of different asymmetric-key and symmetric-key key management protocols for distributed sensor networks. A similar study on the energy cost of establishing keys in sensor nodes was done by Hodjat et al. [9]. They restricted their study to Elliptic-curve Diffie-Hellman Key exchange protocol, and AES algorithm, and obtained energy values by measuring energy consumption of software implementations of these algorithms running on a strongARMbased wireless integrated network sensor (WINS) node [10]. An important step toward energy-efficient security protocols for resource-constrained sensor nodes was proposed by Perriget al. in SPINS [11]. They proposed a set of protocols based on block ciphers and message authentication codes for providing data confidentiality, two-party data authentication, data freshness, and authenticated broadcast with low overhead in sensor networks. A comprehensive study of energy costs associated with implementing security features at the data link layer and network layer in sensor nodes was done in [12]. Jakobsson et al. [13] and Wong et al. [14] proposed energy-efficient mutual authentication and key exchange protocols targeted at client-server interactions where a handheld embedded system and a much more powerful desktop act as client and server, respectively. Karri et al. studied the energy consumed in various operations of a wireless transport layer security (WTLS) protocol running on a pocket PC containing a StrongARM embedded processor [15]. They identified two main sources of energy consumption in the WTLS protocol execution, namely: cryptographic computations and messages exchanged during secure session establishment and during secure data transactions. Based on these observations, they suggest techniques to optimize the energy dissipation of the WTLS protocol based on compression of messages,

modifying the public-key algorithm-based operations in the handshake stage, and making cryptographic computations efficient through the introduction of custom hardware. The changes to the handshake stage include the server obtaining the client certificate from a trusted source rather than requiring the client to transmit it, embedding the client master secret in its certificate and refreshing it by combining it with random numbers exchanged between the client and server, and having a pre-determined master secret which is safely stored in the client and server devices. However, these proposals introduce additional security vulnerabilities, and they have not been examined in the paper. In chapter 3, we present the first comprehensive analysis of the energy consumption of a wide array of common asymmetric, symmetric and hash algorithms on an embedded system [16,17]. Based on this information, suggestions for protocol-level energy optimizations for the SSL protocol are given.

### 2.2 Performance of security protocols in embedded systems

Security protocols and cryptographic algorithms impose significant computational overhead, and studies have indicated that they affect the performance of embedded systems in a significant manner [6,18–22]. For example, Ravi et al. showed that a software implementation of SSL, using 3DES for encryption and SHA for message authentication, running on an iPAQ, requires 650 MIPS to achieve a link speed of 10 Mbps while the StrongARM embedded processor (in iPAQ) can deliver only 235 MIPS. Thus, we see that there is a significant difference between requirements of security processing and the capability of an embedded processor. This difference is termed security processing gap [23].

Evolution of embedded processing architectures to handle security processing can be divided into three stages [24]. In the first stage, we have optimized software implementations of cryptographic algorithms running on embedded processors. Though this approach has fast design times and good application-level flexibility, it has the drawback of low performance. In order to satisfy the high performance requirements of cryptographic algorithms, the second stage in the design evolution of secure embedded processors proposed the use

of application-specific integrated circuits (ASICs). In this approach, a custom-designed circuit, which can accelerate execution of a particular cryptographic algorithm (or a limited set of algorithms), is introduced into the embedded processor. This allows the processor to offload expensive cryptographic computation onto the ASIC which is usually orders of magnitude faster. However, ASICs have very limited flexibility, and are not desirable when the target system has to support multiple cryptographic algorithms and emerging security standards. Thus, in order to combine the flexibility of the software approach with the high performance of ASICs, hybrid hardware-software approaches were proposed. This is the third stage in the evolution of embedded processors targeted toward efficient handling of cryptographic processing. An example of this new approach is an application-specific instruction-set processor (ASIP) where custom hardware is tightly coupled into the datapath of the processor, and is invoked through custom instructions. Usually, common operations in cryptographic algorithms, like permute, rotate, 1024-bit addition and multiplication, etc., are the target for introduction as custom hardware [23]. The preliminary work in this hybrid approach was done by Shi and Lee [25] and Burke et al. [26] in the general-purpose processor domain. Shi and Lee [25] proposed the introduction of instructions to efficiently perform bit-level manipulations, like permute and rotate. While current microprocessors only support rotate, the ability to realize any arbitrary permutation of nbits is a very powerful diffusion operation. Diffusion is a fundamental class of operations in a wide array of block ciphers, and an instruction which implements permute efficiently can speed up the execution of all these block ciphers. While Lee et al. [27] targeted both new and existing ciphers, Burke et al. introduced instructions which implemented a set of operations common to many existing symmetric ciphers. These include substitutions, rotates and modular addition. Ravi et al. [23] designed an embedded processor with custom instructions aimed at accelerating modular exponentiation-based asymmetric algorithms, in addition to some symmetric and hash algorithms. Hodjat et al. [28] designed an embedded processor enhanced with a co-processor which implements the entire round of the AES algorithm. Using this design, they were able to demonstrate Gbit throughput rates for

encrypting datastreams. This hybrid approach has found widespread acceptability in the commercial embedded processors used in wireless handsets, handhelds, etc. For example, the SmartMIPS MIPS32 4KSd [29] processor extends the basic MIPS instruction-set architecture to speed up cryptographic computations. Similar extensions can be found in ARM's SecurCore SC200 [30], TI's OMAP 1610 [31] and NEC's MP211 [32]. Table 2.1 presents a comparision of the features present in the above mentioned secure embedded processors. In Table 2.1, secure mode execution refers to isolation of a secure process through hardware support, secure memory denotes memory whose contents are erased in the presence of tampering, and secure booting is accomplished using the trusted platform technology.

Table 2.1: Comparision of features of some popular secure embedded processors

| Features                | SC200 | MIPS32 4KSd | OMAP 1610 | MP211 |

|-------------------------|-------|-------------|-----------|-------|

|                         | (ARM) | (MIPS)      | (TI)      | (NEC) |

| Custom functionality    | Y     | Y           | Y         | Y     |

| support                 |       |             |           |       |

| Secure execution        | Y     | Y           | Y         | Y     |

| mode                    |       |             |           |       |

| Secure memory           | Y     | Y           | Y         | Y     |

| Secure booting          | N     | N           | N         | Y     |

| Random number           | N     | N           | Y         | N     |

| generation support      |       |             |           |       |

| Tamper resistance       | Y     | Y           | N         | Y     |

| Side-channel resistance | Y     | N           | N         | N     |

ASIPs enhanced with cryptographic hardware extensions are extremely effective in improving the performance of cryptographic computations while maintaining flexibility to accommodate different algorithms and standards. However, an analysis of execution of network security protocols, like SSL and IPSec, reveals that protocol processing imposes as much computational burden as cryptographic computations [24]. By protocol processing, we refer to activities like building and stripping security protocol headers on packets, looking up security databases based on values in the headers, etc. Thus, cryptographic hardware accelerators alone will not suffice in such applications, and we need security protocol engines which accelerate both the protocol and cryptographic functionality. For application-level protocols, such as SSL, tuning the operating system to the working of the application [33]

is one possible way to address some of the non-cryptographic processing bottlenecks. In the case of IPSec running on a general-purpose computing system, it has been shown that processing overheads, such as network processing, data copying and transfer times, severely limit the utility of cryptographic hardware in certain scenarios (e.g., TCP bulk transfers) [34]. Commercial hardware solutions for speeding up both cryptographic and packet processing in high-performance processors can be found in the enterprise server and backbone router markets [35–37]. These products integrate multiple specialized cores on a single chip to provide high-performance secure packet processing. These specialized cores perform activities like, searching the packet stream to identify those which require IPSec processing, building special packet headers, mainting the database of security policies associated with packet streams and so on. All the above mentioned commercial solutions have hardware support for optimizing execution of multiple cryptographic algorithms. For example, Hifn processors [35] have support for DES, AES, SHA, MD5, RSA and DSA, while Nitrox processors [36] support the same set of processors, in addition, to having a fast hardware random number generator. In order to speedup non-cryptographic processing in protocols like IPSec, these processors [35–37] incorporate dedicated memories with fast interfaces for efficient lookup into security policy databases. These designs fall under the category of secure network processors which are ASIPs designed to perform ordinary networking functions and network security processing efficiently [38]. A comparison of various techniques adopted for speeding up IPSec processing on high-performance processors can be found in [39]. However, the hardware costs of these solutions preclude them from being directly applicable in many embedded systems.

In chapter 4, we investigated the design of security protocol processing engines for lowend embedded devices [40,41]. These works developed a high-performance processor for performing efficient IPSec processing on resource-constrained embedded devices. Towards this end, they first analyze the performance of a lightweight IPSec software implementation [42] on a state-of-the-art embedded processor (Xtensa from Tensilica, Inc.). They exploit the processor's configurability (microarchitectural parameters) and extensibility (custom instructions) to provide a speedup of the protocol and cryptographic processing components of the IPSec protocol, respectively.

### 2.3 Side-channel attacks on embedded systems

Cryptography provides techniques for securing systems and the basic services of confidentiality, authentication and integrity. However, there exist different ways of circumventing the security provided by cryptographic algorithms to compromise the security of the system [43]. Techniques for doing this include

- Logical attacks: These attacks exploit flaws in the design or implementation of security protocols. These include software attacks, like buffer overflow attacks, cryptographic key management flaws, random number generator defects, use of debug modes to bypass security, improper algorithm implementation, use of weak passwords, etc.

- Invasive physical attacks: These are physical attacks which consist of cutting open the chip packaging and examining its internals with micro-probing techniques to eavesdrop on communication between components to read secret information.

- Non-invasive physical attacks: These attacks monitor information leaked by the circuit

during cryptographic computation in order to figure out the secret key. The information leaked includes timing information, power dissipation, and electromagnetic

radiation. These attacks are commonly referred to as physical side-channel attacks.

In addition, behavior of a cryptographic algorithm in the presence of faults can also

act as side-channel information.

Among the physical attacks listed above, the most dangerous ones are the non-invasive attacks. In these attacks, the attacker only needs to collect information during the normal operation of the target embedded device, and analyze this information in order to extract the secret key information. In this section, we will restrict our attention to a survey of these non-invasive attacks.

Differential and linear cryptanalysis are two powerful mathematical cryptanalytic techniques developed to break symmetric ciphers [44,45]. However, these attacks require huge amounts of input data, thereby making a practical attack infeasible. For example, to break the 16-round DES, differential and linear cryptanalysis require 2<sup>47</sup> chosen and known plaintexts, respectively (encrypted with the key to be computed). Development of side-channel attacks enabled practically feasible attacks on a number of popular cryptographic algorithms, e.g., DES, RSA, DSS, etc. [46-49]. Kocher demonstrated how an RSA secret key could be determined by recording the time taken by the modular exponentiation computation, and analyzing small variations in time (depending on the presence of 0 or 1 in the secret key). In this attack, predictions are made about individual key bits, and these guesses are verified by using statistical techniques to determine whether there is a correlation between target system's timing behavior and the behavior expected by the prediction. Another popular source of side-channel information is power dissipation [47,48]. In these attacks, power dissipated by the physical implementation of a cryptographic algorithm while processing various plaintexts, is used to extract the bits of the secret key. The principle underlying a power analysis attack is the observation that power dissipated by a circuit is dependent on the values of the internal state bits being manipulated. The state bits, in turn, are parameterized on the value of the secret key. Thus, knowledge of the state bits would give us information about the value of the bits of the unknown secret key. In these attacks, guesses are made for the value of few appropriate state bits, and the guess which results in maximum statistical correlation with the power dissipated is considered to be the actual value of the chosen state bits. Based on the value of the state bits, the value of the key bits is inferred. There are two types of power-based side-channel attacks, simple power analysis (SPA) and differential power analysis (DPA). In SPA, values of the bits of cryptographic keys is inferred directly from the power profile of the cryptographic computation by exploiting any obvious correlations between the two. For example, in modular exponentiation computation, presence of one in the private key exponent leads to an additional modular multiplication operation compared to when there is a zero bit. This extra modular multiplication operation leads to additional power consumption, and this information can be used to infer the value of the private key bits. On the other hand, a DPA attack is much more sophisticated than a SPA attack, and can infer secret key information even when there is no direct correlation between the power profile and the secret key bits. It is based on computing the value of some internal state bits by exploiting their correlation with the power dissipation values which are known. To realize this attack in practice, we need to implement the following steps:

- Select a set of internal state bits which are parameterized on a small subset of secret key bits, and plaintext (or ciphertext).

- Formulate a function which takes as its inputs, the values of plaintext (or ciphertext) and a subset of secret key bits, and calculates the value of the state bits selected above. This function is known as the *objective function*.

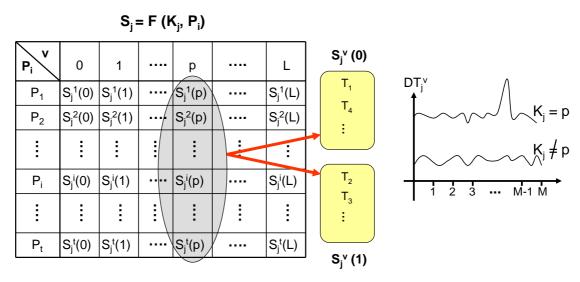

It is necessary that the size of the subset of secret key bits, given as input to the objective function, is small. This enables us to exhaustively enumerate all values of the subset, and for each value we evaluate the objective function in order to compute the value of chosen state bits. This process is repeated for several plaintext (or ciphertext) values. The value of secret key bits subset for which output of the objective function has greatest statistical correlation with the power dissipated by the circuit, over all the plaintext (or ciphertext) values, is chosen as the actual value of the subset. A DPA attack is a divide-and-conquer attack where the secret key is partitioned into subsets, and the above described procedure is repeated for each subset until the value of all secret key bits are found. For example, the 56-bit DES key is partitioned into seven subsets of eight bits each. Since DPA is one of the most successful side-channel attacks used in practice to get secret keys used in cryptographic algorithms, we will present more details of this attack. Figure 2.1 illustrates the steps of this attack. The basic methodology of a DPA attack is as follows:

1. In order to enable the statistical correlation analysis, we need to collect multiple traces of power dissipated by the circuit while it is performing the cryptographic computa-

- tion. So simulate the circuit with t plaintexts  $\{P_1, P_2, \ldots, P_t\}$ , record the corresponding ciphertexts  $\{C_1, C_2, \ldots, C_t\}$ , and the power traces  $\{T_1, T_2, \ldots, T_t\}$ . Each trace  $T_i$  is a collection of M discrete signals sampled over the entire period of computation of the cryptographic algorithm, i.e.,  $T_i = \{T_i^1, T_i^2, \ldots, T_i^M\}$ ,  $1 \le i \le t$ .

- 2. Since DPA is a divide-and-conquer approach, partition the N-bit secret key into m equal-sized subsets,  $\{K_1, K_2, \ldots, K_m\}$ , where  $|K_j| = l = N/m$ ,  $1 \le j \le m$ .  $|K_j|$  indicates the number of bits in subset  $K_j$ .

- 3. Choose a secret key subset  $K_j$  from the set of secret key partitions. Select a state bit,  $S_j$ , whose value can be computed from two input parameters: plaintext  $P_i$  (or ciphertext  $C_i$ ) and  $K_j$  using the objective function F(), i.e.,  $S_j = F(K_j, X)$ ,  $1 \le j \le m$ , where X is either  $P_i$  or  $C_i$ ,  $1 \le i \le t$ . In Figure 2.1, we assume the objective function takes the plaintexts as inputs.

- 4. The *l*-bit value  $K_j$ ,  $1 \le j \le m$ , takes values from zero to *L* where  $L = 2^l 1$ . Let *v* be a value of  $K_j$  where  $0 \le v \le L$ . For each value *v* of  $K_j$ , do the following,

- For each value v, compute value of the state bit  $S_j$  for all the t plaintexts (or ciphertexts). The t values of the state bit are represented by the set  $\{S_j^1(v), S_j^2(v), \ldots, S_j^t(v)\}$  where  $S_j^i(v) = F(v, X)$  and X is either  $P_i$  or  $C_i$ ,  $1 \le i \le t$  (columns of the table in Figure 2.1).

- Based on the values of the state bit in the set  $\{S_j^1(v), S_j^2(v), \dots, S_j^t(v)\}$ , we generate two partitions,  $S_j^v(0)$  and  $S_j^v(1)$  where  $S_j^v(0) = \{T_i, 1 \le i \le t | S_j^i(v) = 0\}$  and  $S_j^v(1) = \{T_i, 1 \le i \le t | S_j^i(v) = 1\}$  such that  $|\{S_j^v(0)\}| + |\{S_j^v(1)\}| = t$ .

- The power traces in sets  $S_j^v(0)$  and  $S_j^v(1)$  are averaged, (at each of the M sample points), and the difference of the two average traces is taken to produce a differential trace,  $DT_j^v$ . Note that the differential trace has M samples.

- 5. By iterating through all possible values for the *l*-bit secret key subset  $K_j$ , we get L differential traces  $DT_j^v$ ,  $0 \le v \le L$ . Only the differential trace corresponding to the

correct value of  $K_j$  exhibits an appreciable spike, while the remaining traces show small noisy spikes of roughly the same amplitude. This is illustrated in Figure 2.1 where the actual value of key subset  $K_j$  is equal to p.

6. We compute the N-bit secret key by repeating the steps 3, 4 and 5 for all the m secret key subsets. Thus, the complexity of key search is reduced from  $2^N - 1$  to  $m \cdot (2^l - 1)$ .

Figure 2.1: DPA attack

Now, we provide some rationale for the behavior of step 5. The set of power traces are partitioned into two sets based on the value of a state bit s (computed by the objective function). During the computation of the cryptographic algorithm, suppose the state bit s flips from 1 to 0 (or 0 to 1) at time (or sample) T in the power trace. Therefore, one set has power traces with a spike at time T due to s being set to 1, while traces in the other set have a smaller spike at time T as a result of s being set to 0 (power consumed by the 0-to-1 transition is more than for the 1-to-0 transition). Given a sufficiently large number of traces in each set, the differential trace will exhibit a spike at time T that represents the difference in power consumption when state bit s is set to 1 and 0. Also, this substantial peak at time T is observed only when the objective function correctly calculates the value of s, which in turn happens when the correct guess is made for the key bits. At any time  $T' \neq T$ , a state bit s' other than s toggles between 0 and 1. Since partitioning of the traces was conditioned

on the value of s, both the sets contain some traces with s' set to 1 and others traces with s' set to 0. In the differential trace, peaks at any time  $T' \neq T$  appear as noise. Similar reasoning applies for appearance of noisy peaks in differential traces computed for incorrect values of the key subset. Thus, the spike at time T will be much longer than the spikes at all other times.

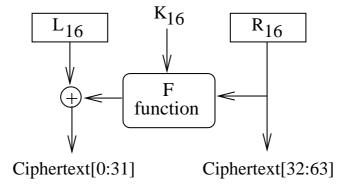

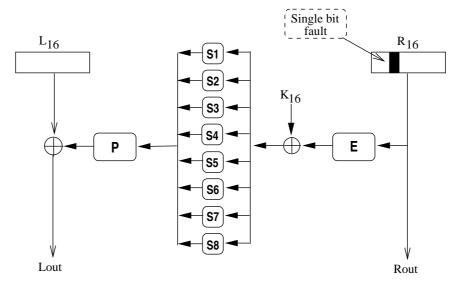

Since one of the inputs to the objective function is the plaintext (or ciphertext), only the state bits in the first or last round can be used for partitioning the power traces. Consider the last round of DES shown in Figure 2.2. We assume that we know the ciphertext values Ciphertext[0:31] and Ciphertext[32:63]. The objective function calculates the value of a bit in register L16 based on the values of the known ciphertext and guesses for a 6-bit subset of the round key K16. The transition of the chosen state bit in register L16 contributes to the power dissipated by the circuit. So the attack on DES in based on the observation that only for the correct guess of the secret key subset, the differential trace has peak which represents power dissipated by the chosen state bit. In Figure 2.2, by using the known value Ciphertext[32:63], and guess for a subset of key K16, we can compute a subset of the output of F function. By XORing the F function output with Ciphertext[0:31], we obtain the value of the target state bit in L16. Similarly, an objective function can be formulated to calculate a state bit in the first round of DES using the known plaintext values. Most of the DPA research has focussed on improving the statistical analysis methods used to extract the key bits from the power traces.

Figure 2.2: Last round of DES