# **Aalborg Universitet**

# A Synchronization Scheme for Single-Phase Grid-Tied Inverters under Harmonic **Distortion and Grid Disturbances**

Hadjidemetriou, Lenos; Yang, Yongheng; Kyriakides, Elias; Blaabjerg, Frede

Published in:

**IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2016.2581019

Publication date:

Document Version Accepted manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Hadjidemetriou, L., Yang, Y., Kyriakides, E., & Blaabjerg, F. (2017). A Synchronization Scheme for Single-Phase Grid-Tied Inverters under Harmonic Distortion and Grid Disturbances. IEEE Transactions on Power Electronics, PP(99), 1-10. DOI: 10.1109/TPEL.2016.2581019

## **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# A Synchronization Scheme for Single-Phase Grid-Tied Inverters under Harmonic Distortion and Grid Disturbances

Lenos Hadjidemetriou, *Graduate Student Member*, *IEEE*, Yongheng Yang, *Member*, *IEEE*, Elias Kyriakides, *Senior Member*, *IEEE*, and Frede Blaabjerg, *Fellow*, *IEEE*

Abstract—Synchronization is a crucial aspect in grid-tied systems, including single-phase photovoltaic inverters, and it can affect the overall performance of the system. Among prior-art synchronization schemes, the Multi Harmonic Decoupling Cell Phase-Locked Loop (MHDC-PLL) presents a fast response under grid disturbances and high accuracy under harmonic distortions. However, major drawbacks of the MHDC-PLL include increased complexity and inaccurate response under non-nominal frequencies, which may occur in practical applications. Thus, this paper proposes strategies to address these issues. At first, a novel re-formulation of an equivalent decoupling cell is proposed for reducing the implementation complexity, and then a frequency adaptive quadrature signal generator for the MHDC-PLL is proposed to enable an accurate response even under non-nominal frequencies. Simulation and experimental results are provided, which show that the proposed synchronization (i.e., the frequency adaptive MHDC-PLL) can achieve a fast and accurate response under any grid disturbance and/or severe harmonic conditions.

Index Terms—Harmonic distortion, grid disturbance, inverters, phase-locked loops, photovoltaics, power quality.

## I. INTRODUCTION

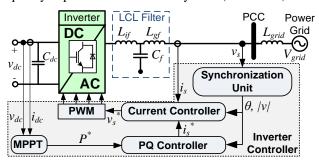

The integration of roof-top photovoltaic (PV) systems has rapidly increased in recent years, where a single-phase configuration is preferable. Such single-phase PV systems employ grid-side power electronic inverters to properly inject the produced energy into the power grid [1], as it is exemplified in Fig. 1. The inverter controller ensures a proper operation of the grid-tied PV systems [1]-[5]. The inverter controller is based on a synchronization unit, an active (P) and reactive (Q) power controller, a current controller and a Maximum Power Point Tracking (MPPT) algorithm. As shown in Fig. 1, the synchronization unit is a crucial part of the inverter controller, since it can affect the inverter controllers and as a result the entire system operation.

The synchronization unit is usually performed by a Phase-Locked Loop (PLL) algorithm and it is responsible for a fast

Manuscript received January 22, 2016; revised April 30, 2016; accepted May 31, 2016. Date of current version June 13, 2016. This work was supported by the Research Promotion Foundation (RPF, Cyprus, Project KOINA/SOLAR-ERA.NET/0114/02), by Energinet.dk (ForskEL, Denmark) and the SOLAR-ERA.NET (European Union's Seventh Framework Programme).

L. Hadjidemetriou and E. Kyriakides are with the KIOS Research Center for Intelligent Systems and Networks and the Department of Electrical and Computer Engineering, University of Cyprus, 1678 Nicosia, Cyprus (e-mail: hadjidemetriou.lenos@ucy.ac.cy; kyriakides@ieee.org).

Y. Yang and F. Blaabjerg is with the Department of Energy Technology, Aalborg University, DK-9220 Aalborg, Denmark (e-mail: yoy@et.aau.dk; fbl@et.aau.dk).

and accurate estimation of the grid voltage and phase angle at the Point of Common Coupling (PCC) under any grid condition (e.g., voltage sags). A fast synchronization enables a proper dynamic performance of the inverter, which is essential for providing Fault Ride Through (FRT) support under low-voltage grid faults and is required by the grid regulations [6], [7]. It should be noted that Japan [8] and Italy [9] have already issued FRT regulations even for low power applications. Moreover, the accuracy of the synchronization against voltage harmonic distortions can benefit the power quality of the PV system as it is discussed in [10]. Thus, it is vital to propose an advanced PLL scheme in terms of fast and good dynamic response under grid faults as well as high robustness against harmonics in these applications.

In the prior-art work, several advanced synchronization methods can be found. An Inverse Park Transformation (IPT) based PLL has been presented in [11] and [12]; a Second Order Generalized Integrator (SOGI) based PLL scheme (SOGI-PLL) has been proposed in [12], [13]; and a SOGI based Frequency-Locked Loop (SOGI-FLL) was suggested in [14], [15]. These three synchronization methods present fast dynamics under grid disturbances and great immunity against high-order harmonics due to the second-order band- or lowpass filtering characteristics. Unfortunately, the second-order filtering characteristics are not adequate to completely eliminate the effect of low-order harmonics as proven in the benchmarking of [13] and in the studies of [14], [16]. A synchronization scheme, named Enhanced PLL (EPLL) is proposed in [2], [12] based on adaptive filtering. In this case, the dynamic response of the synchronization is affected compared to the SOGI-PLL [12], [13] and the immunity against low- and high-order harmonics is poor according to the benchmarking of [13]. Additionally, two very interesting PLL schemes have been proposed in [17] - specifically, the Nonfrequency dependent Transfer Delay PLL (NTD-PLL) and the

Fig. 1. Structure of a single-phase grid-tied inverter and its controller with a synchronization unit.

Enhanced Transfer Delay PLL (ETD-PLL). These synchronization schemes use small signal analysis to modify the transfer delay units required for the synchronization and to insert compensator gains in order to improve the overall PLL performance. As a result, a significant improvement is achieved on the synchronization response, especially in case of ETD-PLL however, it is not possible to completely eliminate the inaccuracies caused by harmonics as it is shown in [17]. The inaccuracies of the prior mentioned synchronization schemes against low-order harmonics can affect the power quality of the grid-tied inverter, since the synchronization information is typically employed throughout the entire control system (e.g., reference frame transform).

Consequently, in order to improve the robustness against low-order harmonic distortions, synchronization techniques based on adaptive or notch filtering techniques [18], [19], solutions using repetitive and multi-resonant controllers [20], and schemes based on Moving Average Filters (MAF) [21], [22] have been proposed in literature. It is to be noted that the use of filtering techniques for improving the harmonic robustness is usually achieved at the cost of the dynamic response of the corresponding synchronization, as it is demonstrated in [10] for the case of the MAF-based PLL. Furthermore, a method for adjusting the PLL bandwidth-tuning is suggested in [23] in order to improve the harmonic immunity, but the tuning of the PLL can directly slow the response of the synchronization, being the major drawback of this solution.

An interesting PLL scheme is proposed in [24], [25], based on a novel Multi Harmonic Decoupling Cell (MHDC) techniques, which can achieve an accurate performance under harmonic distortions without affecting its dynamic responses. Major disadvantages of the MHDC-PLL are, however, the increased complexity in terms of heavy computation burden and the inaccurate response under non-nominal frequencies (e.g., a frequency jump).

In light of the above issues, this paper aims to address the major issues for the MHDC-PLL system and thus to improve the performance by proposing a frequency adaptive MHDC-PLL. In Section II.A, a frequency adaptive Quadrature Signal Generator (QSG) is developed to enable an accurate response under non-nominal frequencies. In Section II.B, the MHDC is reformulated in such way to achieve an equivalent fast and accurate performance under harmonic distortion and grid disturbances, but with a decrease in complexity and required processing time. Finally, in Section II.C, the development of the frequency adaptive MHDC-PLL is presented. A performance analysis and a complexity assessment of the proposed synchronization scheme is performed in Section III, while Section IV demonstrates simulation and experimental results of the proposed frequency adaptive MHDC-PLL. Finally, conclusions are drawn in Section V.

# II. FREQUENCY ADAPTIVE MHDC-PLL

The MHDC-PLL proposed in [24], [25] employs a QSG unit to generate the in-quadrature voltage vector ( $\mathbf{v}_{\alpha\beta}$ ) that is free of high-order harmonics, the MHDC to dynamically decouple the effect of low-order harmonics, and the dq-PLL algorithm to estimate the phase angle of the fundamental

voltage component ( $v^{+1}$ ). The MHDC-PLL of [24], [25] suffers from the increased implementation complexity of the MHDC and the non-ideal or unsatisfactory responses of the QSG under frequency changes as it has been observed in [13]. Hence, the following propose schemes to address these issues.

# A. Frequency Adaptive Quadrature Signal Generator (QSG)

The QSG of the MHDC-PLL in [24], [25] is based on a combination of an IPT structure to cancel out the high-order harmonics and a T/4 delay unit, where T is the nominal period of the grid voltage, to generate the in-quadrature voltage vector (i.e.,  $\mathbf{v}_{\alpha\beta}$ ). The IPT method is based on a forward Park's transformation, on a low-pass filter  $\omega_{fI}/(s+\omega_{fI})$ , and on a backward Park's transformation as described in [24]. It should be noted that the IPT method is not used for the in-quadrature vector  $\mathbf{v}_{\alpha\beta}$  generation, since the filtering effect of IPT on  $v_{\alpha}$  and  $v_{\beta}$  is different. Thus, a more complicated design of the MHDC is required for cancelling out the low-order harmonics. Here, the IPT is only used for filtering the high-order harmonics of the grid voltage  $v_s$ . Therefore, the voltage  $v_{\alpha}$  is free of high-order harmonics and then a T/4 delay unit is used for generating the in-quadrature voltage vector  $\mathbf{v}_{\alpha\beta}$ .

The T/4 delay unit of [24], [25] can accurately be performed in a digital controller, only when the ratio between the sampling frequency (denoted as  $f_s$ ) and the grid frequency ( $f_{grid}$ ) is an integer. Therefore, in the case where the ratio (i.e.,  $f_s/(4f_{grid})$ ) is an integer, the in-quadrature voltage vector  $\mathbf{v}_{\alpha\beta}$  can equivalently be expressed in the continuous- and in the discrete-time domains as,

Continuous-time

$$\rightarrow \mathbf{v}_{\alpha\beta}(t) = \begin{bmatrix} v_{a}(t) \\ v_{\beta}(t) \end{bmatrix} = \begin{bmatrix} v_{a}(t) \\ v_{\alpha}(t - T/4) \end{bmatrix}$$

Discrete-time  $\rightarrow \mathbf{v}_{\alpha\beta}(k) = \begin{bmatrix} v_{a}(k) \\ v_{\beta}(k) \end{bmatrix} = \begin{bmatrix} v_{a}(k) \\ v_{\alpha}(k - f/4) \end{bmatrix}$

(1)

where k is the sampling instant. Unfortunately, in the case where the ratio  $(f_s/4f_{grid})$  is not an integer, the T/4 delay unit of [24], [25] can only approach the closest sample (denoted as  $k_{T/4}$ ) to the T/4 delayed signal, where  $k_{T/4}$  is the rounding value of  $f_s/(4f_{grid})$ . Hence, when the grid frequency varies, the generated discrete-time voltage  $v_\beta(k)$  can present a phase shift error  $\Delta \varphi$  from its desired continuous-time signal  $v_\beta(t)$  as explained by.

$$v_{\beta}(k) = v_{\alpha}(k - k_{T/4}) \Leftrightarrow v_{\beta}(t) = v_{\alpha}(t - T/4 \pm \Delta \varphi).$$

(2)

In the worst case scenario, the phase error  $\Delta \varphi$  is equal to  $180 f_{grid}/f_s$ . For example, when  $f_s = 10$  kHz and  $f_{grid} = 49.505$  Hz, the phase error can reach 0.89 degrees, since the sample  $v_\alpha(k-f_s/(4f_{grid})) = v_\alpha(k-50.5)$  can only be approximated by the closest integer-order delayed sample in the digital controller, which is corresponding to  $v_\alpha(k-51)$ . Such a phase shift error on the in-quadrature voltage vector  $\mathbf{v}_{\alpha\beta}$  will cause significant oscillations (errors) on the voltage signals expressed in the synchronous reference frame. As a result, undesired inaccuracies on the synchronization signals will be raised. A straightforward way to overcome this issue is to use a variable sampling rate as discussed in [26] to ensure that the delay  $f_s/(4f_{grid})$  is always an integer under any grid frequency. However, in such grid-tied inverter applications, the variable

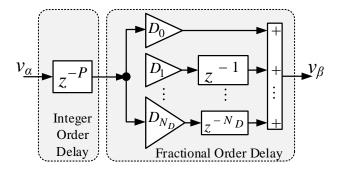

Fig. 2. Structure of the T/4 delay unit for the proposed frequency adaptive MHDC-PLL.

sampling rate is usually not a feasible option, due to several restrictions on the controller design.

Hence, a novel frequency adaptive implementation of the T/4 delay unit is introduced in the following to enable an accurate operation of the MHDC-PLL under any grid frequency. The proposed frequency adaptive T/4 delay unit is developed in a digital controller by splitting the T/4 delay unit (i.e.,  $z^{-(fs/fgrid)/4}$ ) into an integer order delay ( $z^{-P}$ ) and a fractional order delay ( $z^{-F}$ ) as given in (3) and shown in Fig. 2.

$$z^{-(f_s/f_{grid})/4} = z^{-(P+F)}$$

(3)

For the example of the previous paragraph, the value of  $v_{\alpha}(k-f_{s}/(4f_{grid})) = v_{\alpha}(k-50.5)$  will be approximated by splitting the real delay into an integer order delay  $(z^{-P} = z^{-50})$  and a fractional order delay  $(z^{-F} = z^{-0.5})$ . Then, the integer order delay is directly available by the digital controller as an integer order delayed sample  $(z^{-P})$ , while the fractional order delay  $(z^{-F})$  is approximated using the *Lagrange* interpolation polynomial finite-impulse-response filter [27] as,

$$z^{-F} \approx \sum_{l=0}^{N_D} D_l \cdot z^{-l} = D_0 \cdot z^{-0} + D_1 \cdot z^{-1} + \dots + D_{N_D} \cdot z^{-N_D} ;$$

where:

$$D_l = \prod_{\substack{i=0\\i \neq l}}^{N_D} \frac{F - i}{l - i} \text{ and } l = 0, 1, 2 \dots, N_D.$$

(4)

Now, according to [27], a very accurate approximation can be achieved by setting the *Lagrange* interpolation polynomial order  $(N_D)$  as  $N_D = 3$ . Thus, the coefficients  $D_l$  used in this approximation are given by,

$$D_{0} = -\left(\frac{1}{6}\right)(F-1)(F-2)(F-3),$$

$$D_{1} = +\left(\frac{1}{2}\right)F(F-2)(F-3),$$

$$D_{2} = -\left(\frac{1}{2}\right)(F-1)F(F-3),$$

$$D_{3} = +\left(\frac{1}{6}\right)(F-1)(F-2)F.$$

(5)

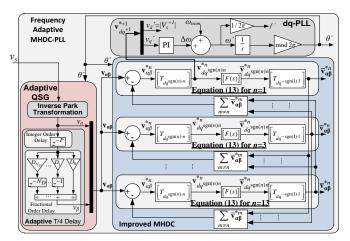

Hence, the frequency adaptive T/4 delay unit is developed in the digital controller according to (3)-(5) and is presented in Fig. 2 in order to generate the in-quadrature voltage vector  $\mathbf{v}_{\alpha\beta}$ , which is as a consequence also frequency adaptive. The discrete-time voltage  $v_{\beta}(k)$  can accurately estimate the continuous-time voltage  $v_{\beta}(t)$ = $v_{\alpha}(t-T/4)$  due to the *Lagrange* interpolation and thus, the use of the adaptive T/4 delay on the structure of the proposed frequency adaptive MHDC-PLL (as shown in Fig. 3) can enable an accurate synchronization under a varying grid frequency.

## B. Reformulation of the MHDC for Complexity Reduction

The decoupling network (i.e., MHDC) of [24], [25] can achieve a dynamic cancellation of the low-order voltage harmonics and hence a fast and accurate synchronization can be ensured under any grid condition (e.g., grid faults and high harmonic distortion). Another major disadvantage of the MHDC of [24], [25] is the increased complexity (processing burden) of the decoupling network, which may be sufficiently high in such real-time applications. Hence, a re-formulation of the decoupling network is proposed in the following in order to minimize the required processing time of the algorithm and still to achieve an exact equivalent response with the conventional MHDC [24], [25]. The complexity minimization is achieved by re-designing the decoupling network in the stationary reference frame ( $\alpha\beta$ -frame) instead of performing this in each synchronous reference frame  $(dq^n$ -frame) as it has initially been proposed in [24], [25].

The re-design of the decoupling network for dynamically cancelling out the low-order harmonics requires the analysis of the grid voltage under high harmonic distortion. As already proved in [24], the QSG is filtering out only the high-order harmonics (due to the IPT) and then it generates the voltage  $v_{\beta}$  component by delaying the voltage  $v_{\alpha}$  for a period of T/4. Thus, under harmonic distorted conditions, the vector  $\mathbf{v}_{\alpha\beta}$  can be expressed as a summation of the fundamental component (n = 1) and of the low-order harmonics (n = 3, 5, 7, 9, 11, 13, ...), as given by,

$$\mathbf{v}_{\alpha\beta} = \mathbf{v}_{\alpha\beta}^{1} + \mathbf{v}_{\alpha\beta}^{3} + \mathbf{v}_{\alpha\beta}^{5} + \dots = V^{1} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \cos(\omega (t - \frac{T}{4}) + \theta_{1}) \end{bmatrix} + \\ \sum_{n=3,5,7,\dots} V^{n} \begin{bmatrix} \cos(n\omega t + \theta_{n}) \\ \cos\left(n\omega (t - \frac{T}{4}) + \theta_{n}\right) \end{bmatrix}, \tag{6}$$

where  $V^n$  and  $\theta_n$  represent the amplitude and the initial phase angle of each voltage component respectively and  $\omega$  is the angular grid frequency. Based on the QSG of the MHDC-PLL [24], [25] and by using basic trigonometric identities, (6) can be analyzed into,

$$\mathbf{v}_{\alpha\beta} = \sum_{n=1,3,5,7,\dots} \mathbf{v}_{\alpha\beta}^{n} \Leftrightarrow \mathbf{v}_{\alpha\beta} = \sum_{n=1,3,5,7,\dots} V^{n} \begin{bmatrix} \cos(\operatorname{sgn}(n) \cdot n\omega t + \theta_{n}) \\ \sin(\operatorname{sgn}(n) \cdot n\omega t + \theta_{n}) \end{bmatrix},$$

where  $\operatorname{sgn}(n) = \sin\left(\frac{n\pi}{2}\right) = \begin{cases} +1 & \text{for } n = 1,5,9,13,\dots \\ -1 & \text{for } n = 3,7,11,\dots \end{cases}$

where sgn(n) defines the speed direction of each component. It is worth noticing that sgn(n) is inserted in this analysis due to the QSG-based  $\mathbf{v}_{a\beta}$ .

According to (7), the direct calculation of each voltage component  $\mathbf{v}_{\alpha\beta}^n$  is not possible due to the coupling effect among the existing components. However, an accurate estimation especially of the fundamental voltage component  $\mathbf{v}_{\alpha\beta}^1$  is necessary for the grid synchronization of a grid-tied inverter system and thus, a novel decoupling network is proposed hereafter. The development of the decoupling network requires to express (7) in terms of any voltage

Fig. 3. Detailed structure of the proposed frequency adaptive MHDC-PLL.

component  $\mathbf{v}_{\alpha\beta}^n$  as,

$$\mathbf{v}_{\alpha\beta}^{n} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} \mathbf{v}_{\alpha\beta}^{m} \Leftrightarrow \begin{bmatrix} v_{\alpha}^{n} \\ v_{\beta}^{n} \end{bmatrix} = \begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} - \sum_{m \neq n} \begin{bmatrix} v_{\alpha}^{m} \\ v_{\beta}^{m} \end{bmatrix}$$

(8)

Now, since the vectors  $\mathbf{v}_{\alpha\beta}^m$  are unknown, the estimation of the voltage component  $\mathbf{v}_{\alpha\beta}^n$  by  $\mathbf{v}_{\alpha\beta}^{*n}$  is enabled in (9) by replacing the unknown vectors  $\mathbf{v}_{\alpha\beta}^m$  of (8) with the corresponding filtered estimation vectors  $\bar{\mathbf{v}}_{\alpha\beta}^{*m}$ .

$$\mathbf{v}_{\alpha\beta}^{*n} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} \bar{\mathbf{v}}_{\alpha\beta}^{*m} \tag{9}$$

The filtered estimation vectors  $\overline{\mathbf{v}}_{\alpha\beta}^{*m}$  are produced by filtering out the corresponding estimation vector  $\mathbf{v}_{\alpha\beta}^{*m}$  in order to eliminate any remaining oscillations after subtracting the coupling effect caused by the existence of other harmonic components. Since each estimation vector  $\mathbf{v}_{\alpha\beta}^{*m}$  is rotated with a different  $\mathrm{sgn}(m)m\omega$ , an equivalent filtering cannot be directly achieved for each component. Therefore, for an equivalent filtering of all the voltage components, it is necessary to express each estimated vector  $\mathbf{v}_{\alpha\beta}^{*m}$  into a corresponding synchronous reference frame rotating with a  $\mathrm{sgn}(m)m\omega$  speed  $(dq^{\mathrm{sgn}(m)m}$ -frame) by using Park's transformation theory. Thus, the m component of the estimation voltage vector expressed in the corresponding  $dq^{\mathrm{sgn}(m)m}$ -frame  $(\mathbf{v}_{dq}^{*\mathrm{sgn}(m)m})$  is given by,

$$\mathbf{v}_{dq}^{*m} = \begin{bmatrix} v_{d \operatorname{sgn}(m) \cdot m} \\ v_{q \operatorname{sgn}(m) \cdot m} \end{bmatrix} = \begin{bmatrix} T_{dq}^{\operatorname{sgn}(m) \cdot m} \end{bmatrix} \mathbf{v}_{\alpha\beta}^{*m}, \text{ where:}$$

$$\begin{bmatrix} T_{dq}^{\operatorname{sgn}(m) \cdot m} \end{bmatrix} = \begin{bmatrix} \cos(\operatorname{sgn}(m) m \omega t) & \sin(\operatorname{sgn}(m) m \omega t) \\ -\sin(\operatorname{sgn}(m) m \omega t) & \cos(\operatorname{sgn}(m) m \omega t) \end{bmatrix}$$

(10)

It should be noted that each vector  $\mathbf{v}_{dq}^{*m}$  is actually described as a DC/non-rotating vector, since both the  $dq^{\mathrm{sgn}(m)m}$  frame and the m voltage component are rotated with the same  $\mathrm{sgn}(m)m$  speed. Therefore, an equivalent filtering can now be achieved since all the voltage components can be expressed as non-rotating vectors according to (10). Therefore, the filtered estimation vector  $\mathbf{\bar{v}}_{dq}^{*sgn}(m)m$  expressed in a corresponding  $dq^{\mathrm{sgn}(m)m}$ -frame is generated by filtering the corresponding estimation vector component  $\mathbf{v}_{da}^{*sgn}(m)m$

according to,

$$\overline{\mathbf{v}}_{dq}^{*m} = \begin{bmatrix} \overline{v}_{d}^{*m} & \\ \overline{v}_{d}^{*gn(m)m} & \overline{v}_{q}^{*m} \\ \overline{v}_{q}^{*gn(m)m} & \end{bmatrix} = [F(s)] \mathbf{v}_{dq}^{*m}, \qquad (11)$$

where  $[F(s)] = \frac{\omega_{f2}}{s + \omega_{f2}} \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$ ,

and  $\omega_{f2}$  is the cut-off frequency of the low-pass filter [F(s)] and should be set to  $2\pi \cdot 50/3$  rad/s according to the theoretical analysis in [24]. Finally, the filtered estimation vector  $\mathbf{\bar{v}}_{\alpha\beta}^{*m}$ , required by (9) to develop the decoupling network, can be calculated based on Park's transformations and is given by,

$$\overline{\mathbf{v}}_{\alpha\beta}^{*m} = \begin{vmatrix} \overline{v}_{\alpha}^{*m} \\ \overline{v}_{\beta}^{*m} \end{vmatrix} = \begin{bmatrix} T_{dq}^{-\operatorname{sgn}(m) \cdot m} \end{bmatrix} \overline{\mathbf{v}}_{dq}^{*m}$$

(12)

When submitting (10) to (11) and then (11) to (12), (9) can be re-written as,

$$\mathbf{v}_{\alpha\beta}^{*n} = \mathbf{v}_{\alpha\beta} - \sum_{m \neq n} \left[ T_{dq}^{-\operatorname{sgn}(m)m} \right] [F(s)] \left[ T_{dq}^{\operatorname{sgn}(m)m} \right] \mathbf{v}_{\alpha\beta}^{*m}$$

(13)

Finally, (13) is the cornerstone of the proposed decoupling network (improved MHDC) as shown in Fig. 3. Hence, the multiple use of (13) for n = 1, 3, 5, 7, ... in a cross feed-back decoupling network enables a dynamic estimation of each voltage component  $\mathbf{v}_{\alpha\beta}^{*n}$ . It should be pointed out that the cross feed-back network is required to dynamically eliminate the coupling effect between the fundamental voltage component and all the significant low-order harmonic components. It is important to mention that the improved MHDC can achieve an exact equivalent performance with the MHDC in [24], [25], but the complexity of the improved MHDC is significantly decreased, as it will be proved in Section III.

#### C. Development of the Frequency Adaptive MHDC-PLL

The proposed frequency adaptive MHDC-PLL can now be developed based on the adaptive QSG (as described in Section II.A), the improved MHDC (as described in Section II.B) and on the dq-PLL algorithm [28] for estimating the phase angle of the grid voltage as shown in Fig. 3. All the design parameters for developing the proposed frequency adaptive MHDC-PLL are summarized in Table I. The new frequency adaptive MHDC-PLL can achieve a fast and accurate synchronization under any grid disturbance and under highly harmonic distortion. The complexity of the synchronization has been significantly decreased compared to the MHDC-PLL of [24], [25], as it will be proved in Section III.

The adaptive QSG is based on the IPT method in order to filter out the high-order harmonics and then the proposed frequency adaptive T/4 delay unit is used to generate the voltage vector  $\mathbf{v}_{\alpha\beta}$ . The proposed frequency adaptive method

TABLE I.

DESIGN PARAMETERS OF FREQUENCY ADAPTIVE MHDC-PLL.

| IPT unit           | Filtering parameter $\rightarrow \omega_{fl} = 2\pi 50\sqrt{2} \text{ rad/s}$ |

|--------------------|-------------------------------------------------------------------------------|

| Adaptive T/4 delay | Langrange interpolation order $\rightarrow N_D=3$                             |

| Improved MHDC      | Multiple use of (13) for <i>n</i> =1, 3, 5, 7, 9, 11, 13                      |

|                    | Filtering parameter $\rightarrow \omega_{f2}=2\pi 50/3 \text{ rad/s}$         |

| dq-PLL             | Tuning parameters $\rightarrow k_P=92$ , $T_I=0.000235$                       |

overcomes the inaccuracies under non-nominal frequency caused by the initial QSG used in [24], [25] and thus, an accurate operation can be achieved under any grid frequency.

Then, the in-quadrature voltage  $\mathbf{v}_{\alpha\beta}$  is fed on the proposed improved MHDC as shown in Fig. 3, in order to dynamically cancel out the effect of the low-order harmonics with minimized computation burden. For a proper design of the improved MHDC, it is first necessary to define the number of harmonic-orders that are considered and eliminated by the decoupling network. An investigation is performed on the accuracy of the frequency adaptive MHDC-PLL under the worst-case voltage harmonic distortion according to EN50160 standards (see HC3 in Table II). The investigation shows that a very accurate synchronization (error in phase angle estimation  $\theta_{error} = \theta_{grid} - \theta'$  less than 0.00035 rad) can be achieved, when the improved MHDC is designed for N = 7, considering the fundamental (n = 1) and the effect of the six most significant harmonic components (n = 3, 5, 7, 9, 11, 13) in single-phase systems. The effect of the higher order harmonics is minimized due to the second-order band-pass filtering characteristics of IPT as mentioned in [24]. Therefore, the decoupling network of the frequency adaptive MHDC-PLL is designed for N = 7 as shown in Fig. 3 in order to achieve an accurate synchronization under any harmonic distorted grid conditions. Thus, the fast and accurate estimation of the fundamental voltage component  $\mathbf{v}_{dq^{+1}}^{*1}$ expressed in the  $dq^{+1}$ -frame is enabled by the improved MHDC. This estimation voltage vector is free of any low- and high-order harmonics and therefore, the conventional dq-PLL algorithm can be used to accurately estimate the phase angle and the amplitude of the grid voltage, as demonstrated in Fig.

The conventional dq-PLL system [28] is a closed-loop synchronization system, which aims to force the per unit  $v_q' = v_{q+1}^{*1}$  to track zero. The synchronization algorithm is based on a Proportional-Integral (PI) controller, whose transfer function is given by  $k_p+1/(T_is)$ , with  $k_p$  and  $T_i$  being the controller parameters. Therefore, based on a linearized small signal analysis, the transfer function of the PLL is given by the second order transfer function of (14), where it is obvious that the tuning parameters ( $k_p$  and  $T_i$ ) can affect the response of the synchronization unit.

$$\frac{\theta'}{\theta} = \frac{k_p \cdot s + \frac{1}{T_i}}{s^2 + k_p \cdot s + \frac{1}{T_i}},$$

(14)

where:

$$k_p = \frac{9.2}{ST}$$

and  $T_i = 0.047 \cdot \zeta^2 \cdot ST^2$

For an optimally damped response of the PLL, the damping coefficient  $\zeta$  should be set to  $1/\sqrt{2}$ ; the Settling Time (ST) has been set to 100 ms for the purposes of this work. Hence, the tuning parameters  $k_p$  and  $T_i$  of the frequency adaptive MHDC-PLL have been set to 92 and  $2.35\cdot10^{-4}$ , respectively.

The proposed frequency adaptive MHDC-PLL can achieve a fast and accurate response under any harmonic distortion and under any grid faults and the required processing time of the proposed synchronization algorithm is significantly less compared to the original MHDC of [24], [25], as it will be

TABLE II.

DEFINITION OF SEVERAL HARMONIC CONDITIONS (HC).

| Normal<br>Operation | Pure sinusoidal grid voltage                                                                                                                                                                                        |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HC1                 | $ V_3 =5\%$ and $ V_5 =6\%$                                                                                                                                                                                         |  |  |  |

| HC2                 | $ V_3 =5\%$ , $ V_5 =6\%$ , $ V_7 =5\%$ , $ V_9 =1.5\%$ , $ V_{II} =3.5\%$                                                                                                                                          |  |  |  |

| НС3                 | Worst case harmonic distortion according to EN50160: $ V_3 $ =5%, $ V_5 $ =6%, $ V_7 $ =5%, $ V_9 $ =1.5%, $ V_{II} $ =3.5%, $ V_{I3} $ =3%, $ V_{I5} $ =0.5%, $ V_{I7} $ =2%, $ V_{I9} $ =1.5%, $ V_{h>20} $ =0.3% |  |  |  |

| HC4                 | An inter-harmonic with 10% amplitude at 375 Hz                                                                                                                                                                      |  |  |  |

| HC5                 | Two sub-harmonics with 7% amplitude each at 5.3 Hz and 7.96 Hz                                                                                                                                                      |  |  |  |

demonstrated in Section III and IV.

## III. PERFORMANCE ANALYSIS - COMPLEXITY EVALUATION

This section aims to prove that the proposed frequency adaptive MHDC-PLL (based on the improved MHDC) and the MHDC-PLL of [24], [25] can achieve an equivalent performance under any harmonic distorted grid voltage and that the proposed improved MHDC (Section II.B) requires significantly less processing time in each control loop.

The proposed improved MHDC, as it is shown in Fig. 3, is based on the multiple-time use of (13) for accurately estimating each voltage component. By analyzing (13), it can be proved that the improved MHDC can achieve an exact equivalent response with the original MHDC proposed in [24], [25]. Thus, by multiplying both sides of (13) with the transformation matrix  $\left[T_{dq^sgn(n)n}\right]$  and applying Park's transformation theory, (13) can be equivalently re-written as (15).

$$\mathbf{v}_{dq}^{*n} = \left[T_{dq}^{\operatorname{sgn}(n)n}\right] \mathbf{v}_{\alpha\beta} - \sum_{\mathbf{v} \in \mathcal{V}} \left[T_{dq}^{\operatorname{sgn}(n)n}\right] \left[T_{dq}^{-\operatorname{sgn}(m)m}\right] \left[F(s)\right] \mathbf{v}_{dq}^{*m}$$

(15)

Then, by filtering both side of (15) with the filtering matrix [F(s)], by using (11), and by merging the transformation matrices, (15) can be re-written as (16), which is the cornerstone equation of the MHDC according to [24], [25].

$$\overline{\mathbf{v}}^{*n}_{dq^{\operatorname{sgn}(n)n}} = \left[F(s)\right] \begin{cases} \mathbf{v}_{dq^{\operatorname{sgn}(n)n}} - \\ \sum_{m \neq n} \left[T_{dq^{\operatorname{sgn}(n)n - \operatorname{sgn}(m)m}}\right] \overline{\mathbf{v}}^{*m}_{dq^{\operatorname{sgn}(m)m}} \end{cases}$$

(16)

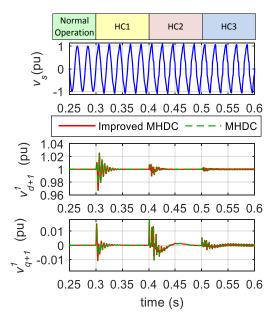

Since (13) can be re-written in the form of (16), it is proven that the MHDC of [24], [25] and the improved MHDC proposed in this paper can achieve an exact equivalent response in terms of estimating the voltage vector of the fundamental voltage component. Furthermore, simulation results of Fig. 4, verify that under several Harmonic Conditions (HC), where HC1, HC2 and HC3 are defined in Table II, both the MHDC of [24], [25] and the improved MHDC present an exact equivalent and identical response on the accurate estimation of the  $\mathbf{v}_{dq+1}^{*1}$ . Since (13) and (16) are equivalent, the theoretical analysis of both decoupling networks is exactly the same as the one that has already been presented in Section II.C of [24] and thus, it is not necessary to repeat this analysis at this point. According to the analysis, the transfer function, the Bode diagram, and the step response

Fig. 4. Comparison of the performance of the proposed improved MHDC and of the MHDC of [24], [25].

[24], both decoupling networks can achieve a very fast and accurate estimation of the fundamental voltage component by completely eliminating the oscillations caused by the harmonic distortion. It is to be noted that the fast and dynamic response of the decoupling network allows the accurate synchronization without causing a further deceleration on the PLL response. Further, the transfer function and the Bode diagram derived in [24] for the series combination of the QSG and the MHDC prove the stability of the proposed PLL and the ability to completely eliminate the harmonic oscillations. Although the two decoupling networks present an equivalent response, the improved MHDC proposed in this paper requires significantly less processing time compared to the MHDC of [24], [25], as it is further analyzed below.

For a fair complexity analysis, both decoupling networks need to be designed for N = 7, to consider the fundamental component (n = 1) and the effect of the six most significant harmonic components (n = 3, 5, 7, 9, 11, 13). Therefore, the process of the MHDC of [24], [25] for N = 7 requires the repeated processing of (16) for seven times. As a consequence, in each control step the decoupling network should process N multi-subtractions  $\left(\mathbf{v}_{dq^{\operatorname{sgn}(n)n}} - \sum_{m \neq n} \overline{\mathbf{v}}_{dq^{\operatorname{sgn}(m)m}}^{*m}\right)$ , transformation matrices  $[T_{dq} \operatorname{sgn}(n)n]$ , and N low-pass filtering matrices [F(s)]. In the case of the improved MHDC, for N = 7, (13) must be repeated for seven times as well. At each control step the improved MHDC should process N multi-subtractions  $(\mathbf{v}_{\alpha\beta} - \sum_{m\neq n} \bar{\mathbf{v}}_{\alpha\beta}^{*m})$ , 2N transformation matrices, and N lowpass filtering matrices [F(s)]. It is obvious that the proposed improved MHDC requires the processing of 2N = 14transformation matrices instead  $N^2 = 49$  matrices of the MHDC of [24], [25]. The complexity comparison is summarized in Table III. A further complexity analysis is also presented in Table III, where the two decoupling networks have been analyzed in terms of the required additions, subtractions and multiplications at each control step. It is obvious that the re-formulation of the decoupling cell

according to the proposed improved MHDC (Section II.B) can significantly decrease the required processing time of the synchronization algorithm. The decreased complexity of the new improved MHDC is particularly useful, since the real-time operation of the inverter is enabled and a higher sampling rate can be adapted by the inverter controller for an improved performance.

Further, an in-depth experimental complexity analysis has been performed, based on a widely used microcontroller, such as the Texas Instrument TMS320F28335 digital signal processor. The investigation demonstrates a significant improvement with regards to the algorithm complexity, since the process of the frequency adaptive MHDC-PLL at each control loop requires 54.6 \( \mu \) instead of 140 \( \mu \) in the case of the initial MHDC-PLL of [24], [25]. Therefore, the proposed synchronization method requires 61% less processing time compared to the initial MHDC-PLL, as summarized in Table IV. It is important to mention that an inverter controller based on the frequency adaptive MHDC-PLL can achieve a sampling rate of 8 kHz on TMS320F28335 (54.6 µs for the synchronization and 63 µs for the rest units of the inverter controller). On the other hand, if the inverter controller is based on the initial MHDC-PLL of [24], [25] the sampling rate should be decreased to 4 kHz on TMS320F28335 (140 µs for the synchronization and 63 us for the rest of the units of the inverter controller). Thus, the higher sampling rate enabled by the proposed PLL can improve the accuracy and the performance of the inverter as a result of minimizing the inaccuracies/distortion introduced by practical digital to analogue converters, such as a zero-order hold. Further, the improvement regarding the algorithm complexity allows to straightforwardly apply the proposed synchronization method in such a real-time practical application within the embedded micro-controller of the grid-tied inverter without requiring additional computational power.

TABLE III.

COMPLEXITY COMPARISON OF THE DECOUPLING NETWORKS.

| Ī | Decoupling<br>Network       | Complexity analysis in each control loop |                                          |                          |                                                     |  |  |

|---|-----------------------------|------------------------------------------|------------------------------------------|--------------------------|-----------------------------------------------------|--|--|

| _ |                             | Multi-<br>subtractions                   | $\left[T_{dq^{\mathrm{sgn}(n)n}}\right]$ | [ <i>F</i> ( <i>s</i> )] | Total mathematical operations                       |  |  |

|   | MHDC of [19] ( <i>N</i> =7) | N                                        | $N^2$                                    | N                        | Multiplications<br>63 Additions<br>133 Subtractions |  |  |

|   | Improved MHDC (N=7)         | N                                        | 2N                                       | N                        | Multiplications<br>28 Additions<br>98 Subtractions  |  |  |

TABLE IV.

PERFORMANCE COMPARISON OF TWO PLLS.

|                          | Required<br>Processing<br>Time (%) | Dynamic<br>Response<br>under<br>grid<br>faults | Accurate Resposne under       |                                         |                     |

|--------------------------|------------------------------------|------------------------------------------------|-------------------------------|-----------------------------------------|---------------------|

| PLL<br>algorithm         |                                    |                                                | Voltage<br>sag/phase<br>shift | Frequency jump $(f \neq 50 \text{ Hz})$ | Harmonic distortion |

| MHDC-PLL                 | 100%                               | Fast                                           | +                             | -                                       | +                   |

| Freq. Adapt.<br>MHDC-PLL | 39%                                | Fast                                           | +                             | +                                       | +                   |

## IV. SIMULATION AND EXPERIMENTAL RESULTS

The performance of the proposed frequency adaptive MHDC-PLL has been tested through simulation and experimental results in order to demonstrate the outstanding response of the new synchronization method. The simulation based investigation has been performed MATLAB/Simulink. The experimental setup is based on a TMS320F28335 microcontroller (where the inverter controller has been applied), a Semikron SEMITeach (B6CI) inverter, a California Instrument 2253IX AC power source for emulating the grid, and an Elektro-Automatik EA-PSI 9750-20 DC power supply for emulating the DC bus of a PV system. It is worth mentioning that in both simulation and experimental studies, an 8 kHz sampling rate has been used for the inverter controller.

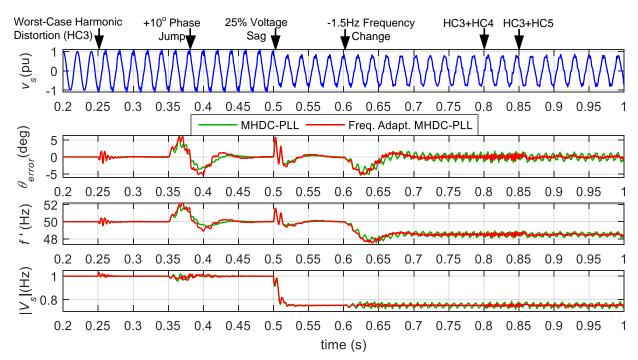

Simulations performed in MATLAB/Simulink show the synchronization response of the proposed frequency adaptive MHDC-PLL, as demonstrated in Fig. 5. The results of Fig. 5 show the synchronization response of the frequency adaptive MHDC-PLL and the MHDC-PLL of [24], [25] under the worst-case harmonic distortion (HC3 of Table II) at 0.25 s, a 10° phase jump at 0.35 s, a 25% voltage sag at 0.5 s, a -1.5 Hz frequency change at 0.6 s, an inter-harmonic distortion (HC4 of Table II) at 0.8 s, and a sub-harmonic distortion (HC5 of Table II) at 0.85 s. The performance comparison of Fig. 5 between the two PLLs, proves that the frequency adaptive implementation of the OSG (Section II.A) enables the accurate synchronization under non-nominal frequencies (0.6 < t < 0.75s). Therefore, the frequency adaptive MHDC-PLL not only requires a significantly less processing time as shown in Section III, but additionally, it can also achieve a superior performance under any grid condition, as summarized in Table IV. From Fig. 5, it is obvious that the new frequency adaptive

MHDC-PLL presents a very accurate response (even under the worst-case harmonic distortion for t > 0.25 s) and a very fast synchronization under any grid disturbance (e.g., phase jump, voltage sag, frequency change). Furthermore, the operation of the new synchronization scheme has been tested under interharmonic (0.8 s - 0.85 s) and sub-harmonic (0.85 s - 1 s) distortion, as shown in Fig. 5. It is worth mentioning that although the improved MHDC has not been designed to eliminate inter-harmonics and/or sub-harmonics. synchronization inaccuracies caused by these harmonics are significantly suppressed ( $\theta_{error}$  is less than 0.75°), but not completely eliminated. The sub-harmonics and interharmonics are suppressed with the proposed synchronization scheme, since the second-order band-pass filtering characteristics of the developed QSG (due to the use of IPT) are inherited by the proposed PLL as shown in the theoretical analysis presented in [24]. The band-pass filtering capabilities of the proposed PLL offers approximately -45 db suppression in the case of sub-harmonics (HC5) and -36 db suppression in the case of inter-harmonics (HC4), according to the theoretical analysis of [24].

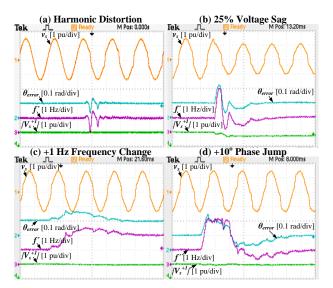

The superior synchronization performance of the proposed frequency adaptive MHDC-PLL has also been experimentally verified as shown in Fig. 6. The experimental results of Fig. 6(a) demonstrate the response of the new synchronization method when the worst-case harmonic distortion (HC3 of Table II) occurs at the grid voltage. The experiments show that the proposed PLL can decouple the effect of harmonics within 10 ms. The initial voltage in Fig. 6(b)-(d) has harmonic distortion with the worst-case harmonics (HC3) and then a grid disturbance is applied. According to Fig. 6(b), a fast and accurate synchronization is achieved under a 25% voltage sag, which can enable a proper FRT operation of the grid tied

Fig. 5. Simulation results for the response of the frequency adaptive MHDC-PLL (new) and the MHDC-PLL under harmonic distortion, phase jump, voltage sag and frequency change events.

Fig. 6. Experimental results for the synchronization response of the frequency adaptive MHDC-PLL under: (a) a harmonic distorted voltage, (b) a 25% voltage sag, (c) an 1 Hz frequency change, and (d) a 100 phase jump. The time division of the results is 10 ms/div.

inverter. Fig. 6(c) demonstrates the operation of the new PLL under a 1 Hz frequency change. It is worth mentioning that the frequency adaptive MHDC-PLL presents a very accurate response under non-nominal frequencies due to the adaptive QSG. Finally, the fast and accurate synchronization response under a 10° phase jump is demonstrated in Fig. 6(d). According to the experiments of Fig. 6, the proposed frequency adaptive MHDC-PLL can achieve a fast and accurate synchronization under any grid conditions. Such an advanced PLL based synchronization method can be an ideal solution for the synchronization of grid tied inverters.

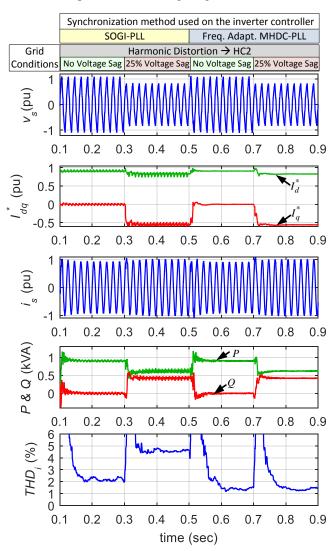

The synchronization accuracy under harmonic distortion can be very beneficial for the power quality of the grid-tied inverter as discussed in [10] and [25], while the dynamic response of the synchronization, especially under voltage sags, can enable a proper FRT operation of the inverter in order to enhance the stability of the power system under grid faults. A simulation based investigation has been performed here to demonstrate the beneficial effect of a fast and accurate synchronization on the operation of the grid-tied inverter as it is shown in Fig. 7. For this investigation, an open loop PQ controller designed in the dq-frame [29] is used to generate the reference currents  $\mathbf{I}_{dq}^* = [I_d^* I_q^*]^T$ . Then, a current controller based on a PI controller and also designed in the dq-frame [29], [30] is used to regulate the inverter current. It is to be noted that the current controller is enhanced with a harmonic compensation module [30] in order to minimize the distortion of the injected current. Furthermore, the PQ controller is enhanced with FRT capabilities [31] in order to provide a proper voltage support under voltage sags, in terms of proper reactive current injection  $I_O$ , according to  $I_O = k(v_N - v_s)$ , where k is set to 2 for the purposes of this investigation and  $v_N$  is the nominal grid voltage [31].

Therefore, the simulation results of Fig. 7 present the inverter operation when a) a SOGI-PLL (t < 0.5 s) and b) when the proposed Frequency Adaptive MHDC-PLL (t > 0.5s) are used for the grid synchronization of the inverter. It should

be noted that the SOGI-PLL does not present immunity against harmonic distortion in contrast with the new PLL which presents a great robustness against harmonics. For a fair comparison, the same tuning parameters have been used for both PLL systems according to Table I and the parameter k of SOGI-PLL has been set to  $\sqrt{2}$  for optimally damped response according to [12], [13]. The inverter operation is demonstrated under highly harmonic distorted grid voltage (HC2 of Table II) and under a 25% voltage sag. It is obvious that the accuracy of the new synchronization against harmonics enables the accurate generation of reference currents  $(\mathbf{I}_{dq}^*)$ while the inaccuracies of SOGI-PLL cause undesired oscillations on the reference currents. The oscillations on the reference currents cause an increased total harmonic distortion of the current  $(THD_i)$  in the case of the SOGI-PLL, with a  $THD_i = 2.15\%$  when there is no voltage sag and  $THD_i = 4.5\%$ when a voltage sag occurs. On the other hand, the accuracy of the proposed frequency adaptive MHDC-PLL enables an oscillation-free generation of the reference currents and thus, a high quality current injection is achieved, with a  $THD_i = 1.5\%$ under normal operation and voltage sag. It is to be noted that

Fig. 7. Simulation results for the inverter operation when (a) a SOGI-PLL and (b) a frequency adaptive MHDC-PLL is used for the synchronization of the inverter under harmonic distorted voltage and a voltage sag event.

the THD; presented in Fig. 7 is calculated according to the time-dependent current signal over a running window of one cycle. This method does not allow the accurate calculation of the *THD*<sub>i</sub> during the transient operation, and thus the resulting THD<sub>i</sub> can be ignored during the transients. Consequently, the accurate calculation of the THD<sub>i</sub> requires approximately two cycles to come to steady-state. Further, the dynamic response of the frequency adaptive MHDC-PLL enables a fast and a proper FRT operation of the inverter, where a reactive power support is properly injected into the grid within 15 ms, for enhancing the stability of the power system. During the FRT operation the injected active power is decreased to maintain the injected current within the inverter limits. Hence, the results of Fig. 7 demonstrate that the accurate and fast response of the frequency adaptive MHDC-PLL is particularly beneficial for the operation of the grid tied inverter, in terms of increasing the power quality and of enabling an appropriate dynamic and FRT operation of the inverter. Especially, the improvement on the quality of the injected current (by minimizing the *THD<sub>i</sub>*) proves that the advanced performance of the proposed PLL is necessary in practical applications and can benefit the overall quality of the power system.

#### V. CONCLUSIONS

In this paper, two new methods have been proposed: one for decreasing the complexity of the Multi Harmonic Decoupling Cell PLL system (MHDC-PLL) and one for enhancing its performance against non-nominal grid frequencies. Hence, the proposed frequency adaptive MHDC-PLL requires a significantly less processing time and presents a superior performance in contrast to the original MHDC-PLL in the case of a varying grid frequency. That is to say, the proposed frequency adaptive MHDC-PLL can achieve a fast and accurate response under any grid disturbances and under highly harmonic distorted grid voltage. As a consequence, the proposed synchronization method can be beneficial for the operation of a grid-tied inverter in terms of improved power quality, fast and accurate dynamics.

# REFERENCES

- L. Zhang, K. Sun, H. Hu and Y. Xing, "A system-level control strategy of photovoltaic grid-tied generation systems for european efficiency enhancement," *IEEE Trans. Power Electronics*, vol. 29, no. 7, pp. 3445-53, Jul. 2014.

- [2] S.A. Khajehoddin, M. Karimi-Ghartemani, A. Bakhshai and P. Jain, "A power control method with simple structure and fast dynamic response for single-phase grid-connected DG systems," *IEEE Trans. Power Electronics*, vol. 28, no. 1, pp. 221-233, Jan. 2013.

- [3] B. Bahrani, A. Rufer, S. Kenzelmann and L.A.C. Lopes, "Vector control of single-phase voltage-source converters based on fictive-axis emulation," *IEEE Trans. Industry Applications*, vol. 47, no. 2, pp. 831-840, Apr. 2011.

- [4] H. Hu, S. Harb, N. Kutkut, I. Batarseh and Z.J. Shen, "A review of power decoupling techniques for microinverters with three different decoupling capacitor locations in PV systems," *IEEE Trans. Power Electronics*, vol. 28, no. 6, pp. 2711-2726, June 2013.

- [5] R.A. Mastromauro, M. Liserre and A. Dell'Aquila, "Control issues in single-stage photovoltaic systems: MPPT, current and voltage control," *IEEE Trans. Industrial Informatics*, vol. 8, no. 2, pp. 241-254, May 2012

- [6] R. Teodorescu, M. Liserre and P. Rodriguez, Grid converters for photovoltaic and wind power systems, John Wiley & Sons, 2011.

- [7] B. Craciun, T. Kerekes, D. Sera and R. Teodorescu, "Overview of recent grid codes for PV power integration," in *Proc. OPTIM*, Brasov, Romania, 2012, pp. 959-965.

- [8] H. Kobayashi, "Fault ride through requirements and measures of distributed PV systems in Japan," in *Proc. IEEE-PES General Meeting*, San Diego (CA), USA, 2012, pp. 1-6.

- [9] CEI, "CEI 0-21: Reference technical rules for connecting users to the active and passive LV distribution companies of electricity," Comitato Elettrotecnico Italiano 2012.

- [10] L. Hadjidemetriou, E. Kyriakides and F. Blaabjerg, "A robust synchronization to enhance the power quality of renewable energy systems," *IEEE Trans. Industrial Electronics*, vol. 62, no. 8, pp. 4858-4868, Aug. 2015.

- [11] L.N. Arruda, S.M. Silva and B.J.C. Filho, "PLL structures for utility connected systems," in *Proc. IEEE IAS Annual Meeting*, 2001, vol.4, pp. 2655-2660.

- [12] Y. Yang and F. Blaabjerg, "Synchronization in single-phase grid-connected photovoltaic systems under grid faults," in *Proc. IEEE PEDG*, Aalborg, Denmark, 2012, pp. 476-482.

- [13] Y. Yang, L. Hadjidemetriou, F. Blaabjerg and E. Kyriakides, "Benchmarking of phase locked loop based synchronization techniques for grid-connected inverter systems," in *Proc. ICPE ECCE Asia*, Seoul, Korea, 2015, pp. 2517-2524.

- [14] P. Rodriguez, A. Luna, M. Ciobotaru, R. Teodorescu and F. Blaabjerg, "Advanced grid synchronization system for power converters under unbalanced and distorted operating conditions," in *proc. IEEE IECON*, Paris, 2006, pp. 5173-5178.

- [15] J. Matas, M. Castilla, J. Miret, L. García de Vicuña and R. Guzman, "An adaptive prefiltering method to improve the Speed/Accuracy tradeoff of voltage sequence detection methods under adverse grid conditions," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 5, pp. 2139-2151 2014.

- [16] P. Rodríguez, A. Luna, R.S. Muñoz-Aguilar, I. Etxeberria-Otadui, R. Teodorescu and F. Blaabjerg, "A stationary reference frame grid synchronization system for three-phase grid-connected power converters under adverse grid conditions," *IEEE Trans. Power Electronics*, vol. 27, no. 1, pp. 99-112, Jan. 2012.

- [17] S. Golestan, J.M. Guerrero, A. Vidal, A.G. Yepes, J. Doval-Gandoy and F.D. Freijedo, "Small-signal modeling, stability analysis and design optimization of single-phase delay-based PLLs," *IEEE Trans. Power Electronics*, vol. 31, no. 5, pp. 3517-3527, May 2016.

- [18] F. Gonzalez-Espin, G. Garcera, I. Patrao and E. Figueres, "An adaptive control system for three-phase photovoltaic inverters working in a polluted and variable frequency electric grid," *IEEE Trans. Power Electronics*, vol. 27, no. 10, pp. 4248-4261, Oct. 2012.

- [19] K. Lee, J. Lee, D. Shin, D. Yoo and H. Kim, "A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS," *IEEE Trans. Industrial Electronics*, vol. 61, no. 1, pp. 292-301, Jan. 2014.

- [20] B. Zhang, K. Zhou and D. Wang, "Multirate repetitive control for PWM DC/AC converters," *IEEE Trans. Industrial Electronics*, vol. 61, no. 6, pp. 2883-2890, June 2014.

- [21] Y. Han, M. Luo, X. Zhao, J. Guerrero and L. Xu, "Comparative performance evaluation of orthogonal-signal-generators based singlephase PLL algorithms-A survey," *IEEE Trans. Power Electronics*, vol. 31, no. 5, pp. 3932-3944, May 2016.

- [22] S. Golestan, M. Ramezani, J.M. Guerrero, F.D. Freijedo and M. Monfared, "Moving average filter based phase-locked loops: Performance analysis and design guidelines," *IEEE Trans. Power Electronics*, vol. 29, no. 6, pp. 2750-2763, June 2014.

- [23] A. Kulkarni and V. John, "Analysis of bandwidth-unit-vector-distortion tradeoff in PLL during abnormal grid conditions," *IEEE Trans. Industrial Electronics*, vol. 60, no. 12, pp. 5820-5829, Dec. 2013.

- [24] L. Hadjidemetriou, E. Kyriakides, Y. Yang and F. Blaabjerg, "A synchronization method for single-phase grid-tied inverters," *IEEE Trans. Power Electronics*, vol. 31, no. 3, pp. 2139-2149, Mar. 2016.

- [25] L. Hadjidemetriou, E. Kyriakides, Y. Yang and F. Blaabjerg, "Power quality improvement of single-phase photovoltaic systems through a robust synchronization method," in *Proc. IEEE ECCE*, Pittsburgh (PA), USA, 2014, pp. 2625-2632.

- [26] I. Carugati, S. Maestri, P.G. Donato, D. Carrica and M. Benedetti, "Variable sampling period filter PLL for distorted three-phase systems," *IEEE Trans. Power Electronics*, vol. 27, no. 1, pp. 321-330, Jan. 2012.

- [27] Y. Yang, K. Zhou, H. Wang, F. Blaabjerg, D. Wang and B. Zhang, "Frequency adaptive selective harmonic control for grid-connected

- inverters," *IEEE Trans. Power Electronics*, vol. 30, no. 7, pp. 3912-3924, July 2015.

- [28] V. Kaura and V. Blasko, "Operation of a phase locked loop system under distorted utility conditions," *IEEE Trans. Industry Applications*, vol. 33, no. 1, pp. 58-63, Jan./Feb. 1997.

- [29] Y. Yang, F. Blaabjerg and Z. Zou, "Benchmarking of grid fault modes in single-phase grid-connected photovoltaic systems," *IEEE Trans. Industry Applications*, vol. 49, no. 5, pp. 2167-2176, Sep. 2013.

- [30] L. Hadjidemetriou, E. Kyriakides and F. Blaabjerg, "A grid side converter current controller for accurate current injection under normal and fault ride through operation," in *Proc. IEEE IECON*, Vienna, Austria, 2013, pp. 1454-1459.

- [31] L. Hadjidemetriou, P. Demetriou and E. Kyriakides, "Investigation of different fault ride through strategies for renewable energy sources," in *Proc. IEEE POWERTECH*, Eindhoven, Netherlands, 2015, pp. 1-6.

Lenos Hadjidemetriou (S'11) received the Diploma in Electrical and Computer Engineering in 2010 from the National Technical University of Athens, Athens, Greece, and his Ph.D. degree in Electrical Engineering in 2016 from University of Cyprus. Currently, he is a Postdoctoral Research Fellow at the KIOS Research Center for Intelligent Systems and Networks, University of Cyprus. His research interests include renewable energy systems, grid synchronization methods, fault ride through control,

power electronics and micro-grids.

Dr. Hadjidemetriou is a member of the Cyprus Technical Chamber. He volunteered as a reviewer to several IEEE transactions and conferences and received the best paper award in the power quality session at IEEE IECON13.

Yongheng Yang (S'12 - M'15) received the B.Eng. degree from Northwestern Polytechnical University, Xian, China, in 2009, and the Ph.D. degree from Aalborg University, Aalborg, Denmark, in 2014. He was a Post-Graduate with Southeast University, Nanjing, China, from 2009 to 2011. In 2013, he was a Visiting Scholar with the Department of Electrical and Computer Engineering, Texas A&M University, College Station, USA. Since 2014, he has been with the Department of Energy Technology, Aalborg

University, where he is currently an Assistant Professor. His research interests are focused on grid integration of renewable energy systems, power converter design, analysis and control, harmonics identification and mitigation, and reliability in power electronics.

Dr. Yang is a Member of the IEEE Power Electronics Society Students and Young Professionals Committee, where he is responsible for the webinar series. He serves as a Guest Associate Editor of the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS special issue on Power Electronics for Energy Efficient Buildings. Dr. Yang has also been invited as a Guest Editor of Applied Sciences special issue on Advancing Grid-Connected Renewable Generation Systems. He is an active reviewer for relevant top-tier journals.

Elias Kyriakides (S'00–M'04–SM'09) received the B.Sc. degree in Electrical Engineering from the Illinois Institute of Technology, Chicago, IL, USA, in 2000 and the M.Sc. and Ph.D. degrees in Electrical Engineering from Arizona State University, Tempe, AZ, USA, in 2001 and 2003, respectively.

He is currently an Associate Professor with the Department of Electrical and Computer Engineering, University of Cyprus, Nicosia. He is also a Founding

Member of the KIOS Research Center for Intelligent Systems and Networks. His research interests include modeling of electric machines, synchronized measurements in power systems, security and reliability of the power system networks, optimization of power system operation techniques, and the integration of renewable energy sources.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he was a Ph.D. Student with Aalborg University, Aalborg, Denmark. He became an Assistant Professor in 1992, Associate Professor in 1996, and Full Professor of power electronics and drives in 1998. His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives.

He has received 17 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014 and the Villum Kann Rasmussen Research Award 2014. He was an Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He is nominated in 2014 and 2015 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.