## WE TRIP THE LICHT FAMILASTIC

### THE

## COMPUTER ENGINEERING HANDBOOK

### The Electrical Engineering Handbook Series

Series Editor

### Richard C. Dorf

University of California, Davis

### Titles Included in the Series

The Avionics Handbook, Cary R. Spitzer

The Biomedical Engineering Handbook, 2nd Edition, Joseph D. Bronzino

The Circuits and Filters Handbook, Wai-Kai Chen

The Communications Handbook, Jerry D. Gibson

The Control Handbook, William S. Levine

The Digital Signal Processing Handbook, Vijay K. Madisetti & Douglas Williams

The Electrical Engineering Handbook, 2nd Edition, Richard C. Dorf

The Electric Power Engineering Handbook, Leo L. Grigsby

The Electronics Handbook, Jerry C. Whitaker

The Engineering Handbook, Richard C. Dorf

The Handbook of Formulas and Tables for Signal Processing, Alexander D. Poularikas

The Industrial Electronics Handbook, J. David Irwin

The Measurement, Instrumentation, and Sensors Handbook, John G. Webster

The Mechanical Systems Design Handbook, Osita D.I. Nwokah and Yidirim Hurmuzlu

The RF and Microwave Handbook, Mike Golio

The Mobile Communications Handbook, 2nd Edition, Jerry D. Gibson

The Ocean Engineering Handbook, Ferial El-Hawary

The Technology Management Handbook, Richard C. Dorf

The Transforms and Applications Handbook, 2nd Edition, Alexander D. Poularikas

The VLSI Handbook, Wai-Kai Chen

The Mechatronics Handbook, Robert H. Bishop

The Computer Engineering Handbook, Vojin G. Oklobdzija

### **Forthcoming Titles**

The Circuits and Filters Handbook, 2nd Edition, Wai-Kai Chen

The Handbook of Ad hoc Wireless Networks, Mohammad Ilvas

The Handbook of Optical Communication Networks, Mohammad Ilyas

The Handbook of Nanoscience, Engineering, and Technology, William A. Goddard,

Donald W. Brenner, Sergey E. Lyshevski, and Gerald J. Iafrate

The Communications Handbook, 2nd Edition, Jerry Gibson and Daniel Blumenthal

### THE

# COMPUTER ENGINEERING

HANDBOOK

Edited by VOJIN G. OKLOBDZIJA

Boca Raton London New York Washington, D.C.

Cover photos from Molecular Expressions Website (www.microscopy.fsu.edu), National High Magnetic Field Laboratory, Optical Microscopy Division, The Florida State University, Tallahassee, FL. ©1995–2001 Michael W. Davidson and The Florida State University. With permission.

### Library of Congress Cataloging-in-Publication Data

The computer engineering handbook / Vojin G. Oklobdzija, editor-in-chief.

p. cm.--(Electrical engineering handbook series)

Includes bibliographical references and index.

ISBN 0-8493-0885-2 (alk. paper)

1. Computer engineering. 2. Electronic digital computers. I. Oklobdzija, Vojin G. II. Series.

TK7885 .C645 2001 004---dc21

2001043891

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the authors and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

Neither this book nor any part may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without prior permission in writing from the publisher.

All rights reserved. Authorization to photocopy items for internal or personal use, or the personal or internal use of specific clients, may be granted by CRC Press LLC, provided that \$1.50 per page photocopied is paid directly to Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923 USA The fee code for users of the Transactional Reporting Service is ISBN 0-8493-0885-2/02/\$0.00+\$1.50. The fee is subject to change without notice. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

The consent of CRC Press LLC does not extend to copying for general distribution, for promotion, for creating new works, or for resale. Specific permission must be obtained in writing from CRC Press LLC for such copying.

Direct all inquiries to CRC Press LLC, 2000 N.W. Corporate Blvd., Boca Raton, Florida 33431.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation, without intent to infringe.

### Visit the CRC Press Web site at www.crcpress.com

© 2002 by CRC Press LLC

No claim to original U.S. Government works

International Standard Book Number 0-8493-0885-2

Library of Congress Card Number 2001043891

Printed in the United States of America 1 2 3 4 5 6 7 8 9 0

Printed on acid-free paper

Fernanda por tu orgullo coraje y dignidad de una mujer luchadora

### Purpose and Background

Computer engineering is such a vast field that it is difficult and almost impossible to present everything in a single book. This problem is also exaggerated by the fact that the field of computers and computer design has been changing so rapidly that by the time this book is introduced some of the issues may already be obsolete. However, we have tried to capture what is fundamental and therefore will be of lasting value. Also, we tried to capture the trends, new directions, and new developments. This book could easily fill thousands of pages because there are so many issues in computer design and so many new fields that are popping out daily. We hope that in the future CRC Press will come with new editions covering some of the more specialized topics in more details. Given that, and many other limitations, we are aware that some areas were not given sufficient attention and some others were not covered at all. However, we hope that the areas covered are covered very well given that they are written by specialists that are recognized as leading experts in their fields. We are thankful for their valuable time and effort.

### Organization

This book contains a dozen sections. First, we start with the fabrication and technology that has been a driving factor for the electronic industry. No sector of the industry has experienced such tremendous growth. The progress has surpassed what we thought to be possible, and limits that were once thought of as fundamental were broken several times. When the first 256 kbit DRAM chips were introduced the "alpha particle scare" (the problem encountered with alpha particles discharging the memory cell) predicted that radiation effects would limit further scaling in dimensions of memory chips. Twenty years later, we have reached 256 Mbit DRAM chips—a thousand times improvement in density—and we see no limit to further scaling. In fact, the memory capacity has been tripling every two years while the number of transistors on the processor chip has been doubling every two years.

The next section deals with computer architecture and computer system organization, a top-level view. Several architectural concepts and organizations of computer systems are described. The section ends with description of performance evaluation measures, which are the bottom line from the user's point of view.

Important design techniques are described in two separate sections, one of which deals exclusively with power consumed by the system. Power consumption is becoming the most important issue as computers are starting to penetrate large consumer product markets, and in several cases low-power consumption is more important than the performance that the system can deliver.

Penetration of computer systems into the consumer's market is described in the sections dealing with signal processing, embedded applications, and future directions in computing.

Finally, reliability and testability of computer systems is described in the last section.

### **Locating Your Topic**

Several avenues are available to access desired information. A complete table of contents is presented at the front of the book. Each of the sections is preceded with an individual table of contents. Finally, each chapter begins with its own table of contents. Each contributed article contains comprehensive references. Some of them contain a "To Probe Further" section where a general discussion of various sources such as books, journals, magazines, and periodicals are discussed. To be in tune with the modern times, some of the authors have also included Web pointers to valuable resources and information. We hope our readers will find this to be appropriate and of much use.

A subject index has been compiled to provide a means of accessing information. It can also be used to locate definitions. The page on which the definition appears for each key defining term is given in the index

The Computer Engineering Handbook is designed to provide answers to most inquiries and to direct inquirers to further sources and references. We trust that it will meet the needs of our readership.

### Acknowledgments

The value of this book is completely based on the work of many experts and their excellent contributions. I am grateful to them. They spent hours of their valuable time without any compensation and with a sole motivation to provide learning material and help enhance the profession. I would like to thank Prof. Saburo Muroga, who provided editorial advice, reviewed the content of the book, made numerous suggestions, and encouraged me to do it. I am indebted to him as well as to other members of the advisory board. I would like to thank my colleague and friend Prof. Richard Dorf for asking me to edit this book and trusting me with this project. Kristen Maus worked tirelessly to put all of this material in a decent shape and so did Nora Konopka of CRC Press. My son, Stanisha, helped me with my English. It is their work that made this book.

### Editor-in-Chief

**Vojin G. Oklobdzija** is a Fellow of the Institute of Electrical and Electronics Engineers and Distinguished Lecturer of IEEE Solid-State Circuits and IEEE Circuits and Systems Societies. He received his Ph.D. and M.Sc. degrees from the University of California, Los Angeles in 1978 and 1982, as well as a Dipl. Ing. (MScEE) from the Electrical Engineering Department, University of Belgrade, Yugoslavia in 1971.

From 1982 to 1991 he was at the IBM T. J. Watson Research Center in New York where he made contributions to the development of RISC architecture and processors. In the course of this work he obtained a patent on Register-Renaming, which enabled an entire new generation of super-scalar processors.

From 1988–90 he was a visiting faculty at the University of California, Berkeley, while on leave from IBM. Since 1991, Prof. Oklobdzija has held various consulting positions. He was a consultant to Sun Microsystems Laboratories, AT&T Bell Laboratories,

Hitachi Research Laboratories, Silicon Systems/Texas Instruments Inc., and Siemens Corp. where he was principal architect of the Siemens/Infineon's TriCore processor. Currently he serves as an advisor to SONY and Fujitsu Laboratories.

In 1988 he started Integration, which was incorporated in 1996. Integration Corp. delivered several successful processor and encryption processor designs. (see: www.integration-corp.com)

Prof. Oklobdzija has held various academic appointments, besides the current one at the University of California. In 1991, as a Fulbright professor, he was helping to develop programs at universities in South America. From 1996–98 he taught courses in the Silicon Valley through the University of California, Berkeley Extension, and at Hewlett-Packard.

He holds seven US, four European, one Japanese, and one Taiwanese patents in the area of computer design and seven others currently pending.

Prof. Oklobdzija is a member of the American Association for Advancement of Science, and the American Association of the University Professors. He serves on the editorial boards of the IEEE Transaction of VLSI Systems and the Journal of VLSI Signal Processing. He served on the program committees of the International Conference on Computer Design, the International Symposium on VLSI Technology and Symposium on Computer Arithmetic. In 1997, he was a General Chair of the 13th Symposium on Computer Arithmetic and is serving as a program committee member of the International Solid-State Circuits Conference (ISSCC) since 1996. He has published over 120 papers in the areas of circuits and technology, computer arithmetic and computer architecture, and has given over 100 invited talks and short courses in the USA, Europe, Latin America, Australia, China, and Japan.

### Editorial Board

### Krste Asanovic

Massachusetts Institute of Technology Cambridge, Massachusetts

### William Bowhill

Compaq/DEC Shrewsbury, Massachusetts

### Anantha Chandrakasan

Massachusetts Institute of Technology Cambridge, Massachusetts

### Hiroshi Iwai

Tokyo Institute of Technology Yokohama, Japan

### Saburo Muroga

University of Illinois Urbana, Illinois

### Kevin Nowka

IBM Austin Research Laboratory Austin, Texas

### Takayasu Sakurai

Tokyo University Tokyo, Japan

### **Alan Smith**

University of California, Berkeley Berkeley, California

### Ian Young

Intel Corporation Hillsboro, Oregon

### Contributors

Cyrus (Morteza) Afghahi

Broadcom Corporation Irvine, California

Chouki Aktouf

Institute Universitaire de Technologie Valex Cedex, France

John F. Alexander

University of North Florida Jacksonville, Florida

Krste Asanovic

Massachusetts Institute of Technology Cambridge, Massachusetts

William Athas

Apple Computer Inc. Sunnyvale, California

Ming Au-Yeung

San Francisco State University San Francisco, California

Pervez M. Aziz

Agere Systems Allentown, Pennsylvania

Raymond Barrett

University of North Florida Jacksonville, Florida

Mario Blaum

IBM Alamaden Research Center San Jose, California

Shekhar Borkar

Intel Corporation Hillsboro, Oregon **Pradip Bose**

IBM T.J. Watson Research Center Yorktown Heights, New York

Don Bouldin

University of Tennessee Knoxville, Tennessee

E. Bozorgzadeh

University of California Los Angeles, California

Thomas D. Burd

University of California Berkeley, California

R. Chandramouli

Synopsys Inc. Mountain View, California

Tzi-cker Chiueh

State University of New York at Stony Brook Stony Brook, New York

K. Wayne Current

University of California Davis, California

Adam Dabrowski

Poznan University of Technology Poznan, Poland

Babak Daneshrad

University of California Los Angeles, California

Vivek De

Intel Corporation Hillsboro, Oregon Miroslav Despotović

Technical University of Novi Sad Novi Sad, Yugoslavia

Jozo J. Dujmović

San Francisco State University San Francisco, California

Manoj Franklin

University of Maryland College Park, Maryland

Matt Franklin

University of California at Davis Davis, California

**Borko Furht**

Florida Atlantic University Boca Raton, Florida

Jean-Luc Gaudiot

University of Southern California City of Commerce, California

U. Glaeser

Halstenbach ACT GmbH Paderborn, Germany

Ricardo Gonzalez

Tensilica, Inc. Santa Clara, California

Gensuke Goto

Yamagata University Yamagata, Japan

Anna Hac

University of Hawaii Honolulu, Hawaii

Siamack Haghighi

Intel Corporation Santa Clara, California Yoshiaki Hagiwara

Sony Corporation Tokyo, Japan

James O. Hamblen

Georgia Institute of Technology Atlanta, Georgia

**Mohammad Ilyas**

Florida Atlantic University Boca Raton, Florida

Hiroshi Iwai

Tokyo Institute of Technology Yokohama, Japan

**Bruce Jacob**

University of Maryland College Park, Maryland

Shahram Jamshidi

Intel Corporation Santa Clara, California

Snehal Jariwala

Intel Corporation Santa Clara, California

Wenjie Jiang

Intel Corporation Santa Clara, California

**Eugene John**

The University of Texas San Antonio, Texas

Lizy Kurian John

University of Texas at Austin Austin, Texas

Yuichi Kado

NIT Telecommunications Technology Laboratories Kanagawa, Japan

James Kao

Intel Corporation Hillsboro, Oregon

R. Kastner

University of California Los Angeles, California Ali Keshavarzi

Intel Corporation Hillsboro, Oregon

Fabian Klass

Sun Microsystems, Inc. Palo Alto, California

Tadahiro Kuroda

Keio University Keio, Japan

Ruby Lee

Princeton University Princeton, New Jersey

Worayot Lertniphonphun

Georgia Institute of Technology Atlanta, Georgia

John George Maneatis

True Circuits, Inc. Los Altos, California

Tomasz Marciniak

Poznan University of Technology Poznan, Poland

**Brian Marcus**

IBM Almaden Research Center San Jose, California

Dejan Marković

University of California Berkeley, California

Daniel Martin

Infineon Mountain View, California

Binu Matthew

University of Utah Salt Lake City, Utah

John C. McCallum

National University of Singapore Singapore, Singapore

James H. McClellan

Georgia Institute of Technology Atlanta, Georgia S.O. Memik

University of California Los Angeles, California

Masayuki Miyazaki

Hitachi, Ltd. Tokyo, Japan

John Morris

University of Western Australia Perth, Australia

Samiha Mourad

Santa Clara University Santa Clara, California

Raj Nair

Intel Corporation Hillsboro, Oregon

Siva Narendra

Intel Corporation Hillsboro, Oregon

Danny F. Newport

University of Tennessee Knoxville, Tennessee

Kevin J. Nowka

IBM Austin Research Laboratory Austin, Texas

Shun-ichiro Ohmi

Tokyo Institute of Technology Yokohama, Japan

Garrett Okamoto

Santa Clara University Santa Clara, California

Ara Patapoutian

Maxtor

Shrewsbury, Massachusetts

Rakesh Patel

Intel Corporation Santa Clara, California

Gerald G. Pechanek

BOPS, Inc.

Chapel Hill, North Carolina

**Christian Piguet**

CSEM: Centre Suisse d'Electronique et de Microtechnique SA and LAP-EPFL

Neuchatel, Switzerland

Donna Quammen

George Mason University Fairfax, Virginia

Hema Ramamurthy

Intel Corporation Santa Clara, California

Todd R. Reed

University of California at Davis Davis, California

Peter Reiher

University of California Los Angeles, California

**Eric Rotenberg**

North Carolina State University Raleigh, North Carolina

Kaushik Roy

Purdue University West Lafayette, Indiana

Abdul Sadka

University of Surrey Surrey, England

Sadiq M. Sait

King Fahd University Dhahran, Saudi Arabia

M. Sarrafzadeh

University of California Los Angeles, California

Thomas C. Savell

Creative Advanced Technology Center Santa Cruz, California

**Necip Sayiner**

Agere Systems Allentown, Pennsylvania

Giovanni Seni

Motorola Human Interface Labs Palo Alto, California Vojin Šenk

University of Novi Sad Novi Sad, Yugoslavia

Katsunori Seno

Sony Corporation Tokyo, Japan

Dezsö Sima

Budapest Polytechnic Budapest, Hungary

**Kevin Skadron**

University of Virginia Charlottesville, Virginia

**Mark Smotherman**

Clemson University Clemson, South Carolina

Hendrawan Soeleman

Purdue University West Lafayette, Indiana

Emina Šoljanin

Lucent Technologies New Vernon, New Jersey

**Dinesh Somasekhar**

Intel Corporation Hillsboro, Oregon

Z. Stamenković

University of Nis Nis, Yugoslavia

N. Stojadinović

University of Nis Nis, Yugoslavia

**Iavashree Subrahmonia**

IBM Thomas J. Watson Research Center Yorktown Heights, New York

Earl E. Swartzlander, Ir.

University of Texas at Austin Austin, Texas

Fred J. Taylor

University of Florida Gainesville, Florida Vivek Tiwari

Intel Corporation Santa Clara, California

**Daniel Tomasevich**

San Francisco State University San Francisco, California

Nestoras Tzartzanis

Fujitsu Laboratories of America Sunnyvale, California

Ionathan W. Valvano

University of Texas at Austin Austin, Texas

Hemmige Varadarajan

Intel Corporation Santa Clara, California

Peter J. Varman

Rice University Houston, Texas

Bane Vasić

University of Arizona Tucson, Arizona

Ingrid Verbauwhede

University of California Los Angeles, California

H. T. Vierhaus

Bradenburgische Technische Universitat Cottbus, Germany

**Jeffrey Scott Vitter**

Duke University Durham, North Carolina

Albert Wang

Tensilica, Inc. Santa Clara, California

Shoichi Washino

Tottori University Tottori City, Japan

Wavne Wolf

Princeton University Princeton, New Jersey Thucydides Xanthopoulos Caveo Networks, Inc.

Marlboro, Massachusetts

Shunzo Yamashita Hitachi, Ltd.

Tokyo, Japan

**Chik-Kong Ken Yang** University of California Los Angeles, California

Yibin Ye

Intel Corporation Hillsboro, Oregon

**Habib Youssef** King Fahd University Dharan, Saudi Arabia

### Contents

### **SECTION I** Fabrication and Technology

- 1 Trends and Projections for the Future of Scaling and Future Integration Trends Hiroshi Iwai and Shun-ichiro Ohmi

- 2 CMOS Circuits

- 2.1 VLSI Circuits Eugene John

- 2.2 Pass-Transistor CMOS Circuits Shunzo Yamashita

- 2.3 Synthesis of CMOS Pass-Transistor Logic Dejan Marković

- 2.4 Silicon on Insulator (SOI) Yuichi Kado

- 3 High-Speed, Low-Power Emitter Coupled Logic Circuits *Tadahiro Kuroda*

- 4 Price-Performance of Computer Technology John C. McCallum

### **SECTION II Computer Systems and Architecture**

- 5 Computer Architecture and Design

- 5.1 Server Computer Architecture Siamack Haghighi

- 5.2 Very Large Instruction Word Architectures Binu Mathew

- 5.3 Vector Processing Krste Asanovic

- 5.4 Multithreading, Multiprocessing Manoj Franklin

- 5.5 Survey of Parallel Systems Donna Quammen

- 5.6 Virtual Memory Systems and TLB Structures Bruce Jacob

- 6 System Design

- 6.1 Superscalar Processors Mark Smotherman

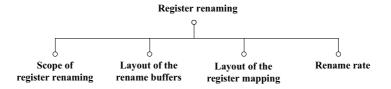

- 6.2 Register Renaming Techniques Dezsö Sima

- 6.3 Predicting Branches in Computer Programs Kevin Skadron

- 6.4 Network Processor Architecture Tzi-cker Chiueh

- 7 Architectures for Low Power Pradip Bose

- 8 Performance Evaluation

- 8.1 Measurement and Modeling of Disk Subsystem Performance Jozo J. Dujmović, Daniel Tomasevich, and Ming Au-Yeung

- 8.2 Performance Evaluation: Techniques, Tools, and Benchmarks *Lizy Kurian John*

- 8.3 Trace Caching and Trace Processors Eric Rotenberg

- 9 Computer Arithmetic

- 9.1 High-Speed Computer Arithmetic Earl E. Swartzlander, Jr.

- 9.2 Fast Adders and Multipliers Gensuke Goto

### **SECTION III Design Techniques**

- 10 Timing and Clocking

- 10.1 Design of High-Speed CMOS PLLs and DLLs John George Maneatis

- 10.2 Latches and Flip-Flops Fabian Klass

- 10.3 High-Performance Embedded SRAM Cyrus (Morteza) Afghahi

- 11 Multiple-Valued Logic Circuits K. Wayne Current

- 12 FPGAs for Rapid Prototyping James O. Hamblen

- 13 Issues in High-Frequency Processor Design Kevin J. Nowka

### **SECTION IV** Design for Low Power

- 14 Low-Power Design Issues Hemmige Varadarajan, Vivek Tiwari, Rakesh Patel, Hema Ramamurthy, Shahram Jamshidi, Snehal Jariwala, and Wenjie Jiang

- 15 Low-Power Circuit Technologies Masayuki Miyazaki

- 16 Techniques for Leakage Power Reduction Vivek De, Ali Keshavarzi, Siva Narendra, Dinesh Somasekhar, Shekhar Borkar, James Kao, Raj Nair, and Yibin Ye

- 17 Dynamic Voltage Scaling Thomas D. Burd

- 18 Low-Power Design of Systems on Chip Christian Piguet

- 19 Implementation-Level Impact on Low-Power Design *Katsunori Seno*

- 20 Accurate Power Estimation of Combinational CMOS Digital Circuits Hendrawan Soeleman and Kaushik Roy

- 21 Clock-Powered CMOS for Energy-Efficient Computing Nestoras Tzartzanis and William Athas

### **SECTION V** Embedded Applications

- 22 Embedded Systems-on-Chips Wayne Wolf

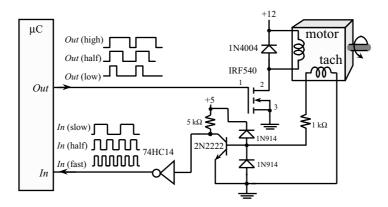

- 23 Embedded Processor Applications Jonathan W. Valvano

### **SECTION VI Signal Processing**

- 24 Digital Signal Processing Fred J. Taylor

- 25 DSP Applications Daniel Martin

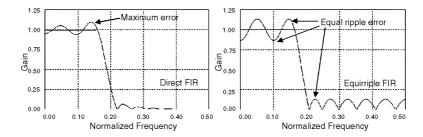

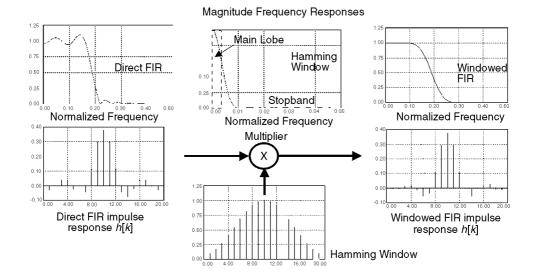

- 26 Digital Filter Design Worayot Lertniphonphun and James H. McClellan

- 27 Audio Signal Processing Adam Dabrowski and Tomasz Marciniak

- 28 Digital Video Processing Todd R. Reed

- 29 Low-Power Digital Signal Processing Thucydides Xanthopoulos

### **SECTION VII Communications and Networks**

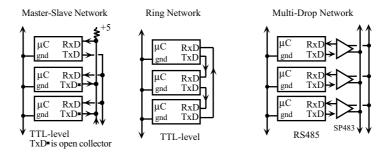

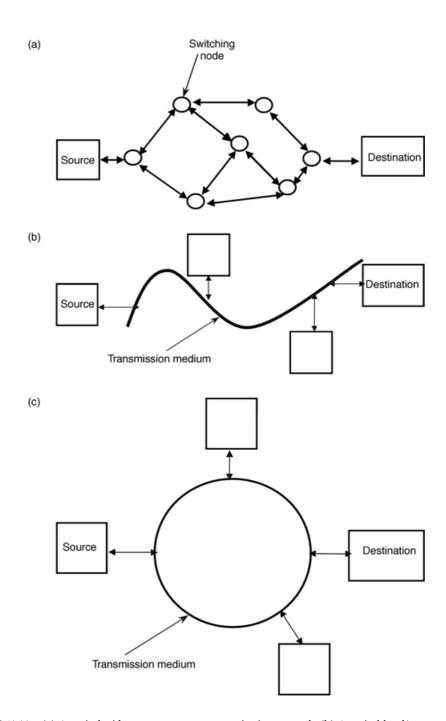

30 Communications and Computer Networks Anna Hać

### SECTION VIII Input/Output

- 31 Circuits for High-Performance I/O Chik-Kong Ken Yang

- 32 Algorithms and Data Structures in External Memory Jeffrey Scott Vitter

- 33 Parallel I/O Systems Peter J. Varman

- 34 A Read Channel for Magnetic Recording

- 34.1 Recording Physics and Organization of Data on a Disk Bane Vasić and Miroslav Despotović

- 34.2 Read Channel Architecture Bane Vasić, Pervez M. Aziz, and Necip Sayiner

- 34.3 Adaptive Equalization and Timing Recovery Pervez M. Aziz

- 34.4 Head Position Sensing in Disk Drives Ara Patapoutian

- 34.5 Modulation Codes for Storage Systems Brian Marcus and Emina Šoljanin

- 34.6 Data Detection Miroslav Despotović and Vojin Šenk

- 34.7 An Introduction to Error-Correcting Codes Mario Blaum

### **SECTION IX** Operating System

35 Distributed Operating Systems Peter Reiher

### **SECTION X** New Directions in Computing

- 36 SPS: A Strategically Programmable System M. Sarrafzadeh, E. Bozorgzadeh, R. Kastner, and S. O. Memik

- 37 Reconfigurable Processors

- 37.1 Reconfigurable Computing John Morris

- 37.2 Using Configurable Computing Systems Danny Newport and Don Bouldin

- 37.3 Xtensa: A Configurable and Extensible Processor Ricardo E. Gonzalez and Albert Wang

- 38 Roles of Software Technology in Intelligent Transportation Systems Shoichi Washino

- 39 Media Signal Processing

- 39.1 Instruction Set Architecture for Multimedia Signal Processing *Ruby Lee*

- 39.2 DSP Platform Architecture for SoC Products Gerald G. Pechanek

- 39.3 Digital Audio Processors for Personal Computer Systems *Thomas C. Savell*

- 39.4 Modern Approximation Iterative Algorithms and Their Applications in Computer Engineering Sadiq M. Sait and Habib Youssef

- 40 Internet Architectures Borko Furht

- 41 Microelectronics for Home Entertainment Yoshiaki Hagiwara

- 42 Mobile and Wireless Computing

- 42.1 Bluetooth—A Cable Replacement and More John F. Alexander and Raymond Barrett

- 42.2 Signal Processing ASIC Requirements for High-Speed Wireless Data Communications Babak Daneshrad

- 42.3 Communication System-on-a-Chip Samiha Mourad and Garret Okamoto

- 42.4 Communications and Computer Networks Mohammad Ilyas

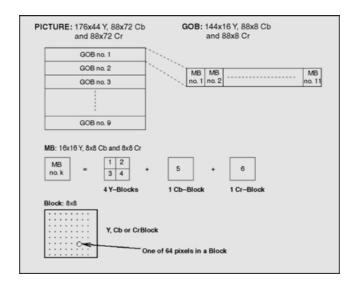

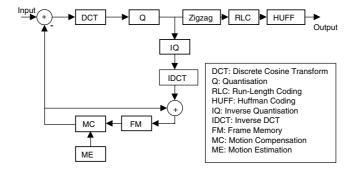

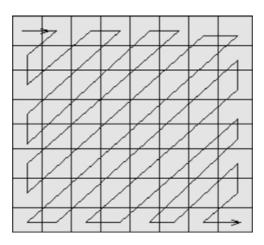

- 42.5 Video over Mobile Networks Abdul H. Sadka

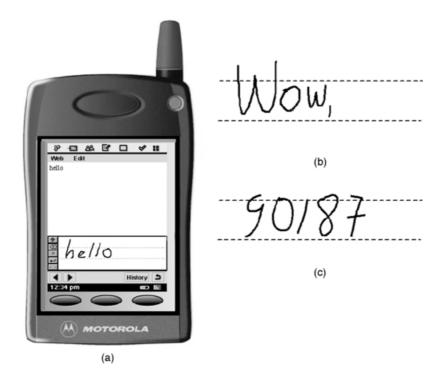

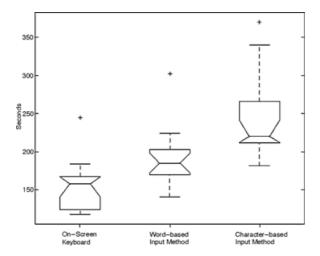

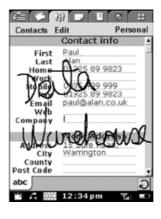

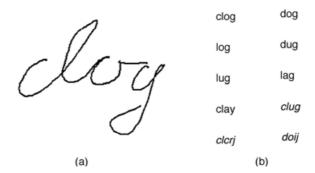

- 42.6 Pen-Based User Interfaces—An Applications Overview Giovanni Seni and Jayashree Subrahmonia

- 42.7 What Makes a Programmable DSP Processor Special? Ingrid Verbauwhede

- 43 Data Security Matt Franklin

### SECTION XI Testing and Design for Testability

44 System-on-Chip (SoC) Testing: Current Practices and Challenges for Tomorrow R. Chandramouli

- 45 Testing of Synchronous Sequential Digital Circuits U. Glaeser, Z. Stamenković, and H. T. Vierhaus

- 46 Scan Testing Chouki Aktouf

- 47 Computer-Aided Analysis and Forecast of Integrated Circuit Yield Z. Stamenković and N. Stojadinović

I

### Fabrication and Technology

- 1 Trends and Projections for the Future of Scaling and Future Integration Trends Hiroshi Iwai and Shun-ichiro Ohmi Introduction • Downsizing below 0.1 μm • Gate Insulator • Gate Electrode • Source and Drain • Channel Doping • Interconnects • Memory Technology • Future Prospects

- 2 CMOS Circuits Eugene John, Shunzo Yamashita, Dejan Marković, and Yuichi Kado VLSI Circuits • Pass-Transistor CMOS Circuits • Synthesis of CMOS Pass-Transistor Logic • Silicon on Insulator (SOI)

- 3 High-Speed, Low-Power Emitter Coupled Logic Circuits Tadahiro Kuroda

Active Pull-Down ECL Circuits Low-Voltage ECL Circuits

- 4 Price-Performance of Computer Technology John C. McCallum

Introduction Computer and Integrated Circuit Technology Processors Memory

and Storage—The Memory Hierarchy Computer Systems—Small to Large Summary

### Trends and Projections for the Future of Scaling and Future Integration **Trends**

- Hiroshi Iwai

- Shun-ichiro Ohmi

Tokyo Institute of Technology

**Channel Doping** 1.6 Tokyo Institute of Technology 1.7 Interconnects 1.8 Memory Technology

1.1

1.2 1.3

1.4 1.5

1.9 **Future Prospects**

Introduction

Gate Insulator Gate Electrode

Source and Drain

Downsizing below 0.1  $\mu$ m

### Introduction 1.1

Recently, information technology (IT)—such as Internet, i-mode, cellular phone, and car navigation has spread very rapidly all over of the world. IT is expected to dramatically raise the efficiency of our society and greatly improve the quality of our life. It should be noted that the progress of IT entirely owes to that of semiconductor technology, especially Silicon LSIs (Large Scale Integrated Circuits). Silicon LSIs provide us high speed/frequency operation of tremendously many functions with low cost, low power, small size, small weight, and high reliability. In these 30 years, the gate length of the metal oxide semiconductor field effect transistors (MOSFETs) has reduced 100 times, the density of DRAM increased 500,000 times, and clock frequency of MPU increased 2,500 times, as shown in Table 1.1. Without such a marvelous progress of LSI technologies, today's great success in information technology would not be realized at all.

The origin of the concept for solid-state circuit can be traced back to the beginning of last century, as shown in Fig. 1.1. It was more than 70 years ago, when J. Lilienfeld using Al/Al<sub>2</sub>O<sub>3</sub>/Cu<sub>2</sub>S as an MOS structure invented a concept of MOSFETs. Then, 54 years ago, first transistor (bipolar) was realized using germanium. In 1960, 2 years after the invention of integrated circuits (IC), the first MOSFET was realized by using the Si substrate and SiO<sub>2</sub> gate insulator [1]. Since then Si and SiO<sub>2</sub> became the key materials for electronic circuits. It takes, however, more than several years until the Silicon MOSFET evolved to Silicon ICs and further grew up to Silicon LSIs. The Silicon LSIs became popular in the market from the beginning of 1970s as a 1 kbit DRAM and a 4 bit MPU (microprocessor). In the early 1970s, LSIs started

TABLE 1.1

Past and Current Status of Advanced LSI Products

| Year    | Min.<br>L <sub>g</sub> (µm) | Ratio | DRAM  | Ratio   | MPU   | Ratio |

|---------|-----------------------------|-------|-------|---------|-------|-------|

| 1970/72 | 10                          | 1     | 1 k   | 1       | 750 k | 1     |

| 2001    | 0.1                         | 1/100 | 512 M | 256,000 | 1.7 G | 2,300 |

### Year 2001 New Century for Solid-State Circuit

20th C

73 years since the concept of MOSFET 1928, J. Lilienfeld, MOSFET patent

54 years since the 1st Transistor

1947, J. Bardeen, W. Bratten, bipolar Tr

43-42 years since the 1st Integrated Circuits 1958, J. Kilby, IC

1959, R. Noice, Planar Technolgy

41 years since the 1st Si-MOSFET 1960, D. Kahng, Si-MOSFET

38 years since the 1st CMOS

1963, CMOS, by F. Wanlass, C. T. Sah

31 years since the 1st 1 kbit DRAM (or LSI) 1970 Intel 1103

16 years since CMOS became the major technology 1985, Toshiba 1 Mbit CMOS DRAM

FIGURE 1.1 History of LSI in 20th century.

by using PMOS technology in which threshold voltage control was easier, but soon the PMOS was replaced by NMOS, which was suitable for high speed operation. It was the middle of 1980s when CMOS became the main stream of Silicon LSI technology because of its capability for low power consumption. Now CMOS technology has realized 512 Mbit DRAMs and 1.7 GHz clock MPUs, and the gate length of MOSFETs in such LSIs becomes as small as 100 nm.

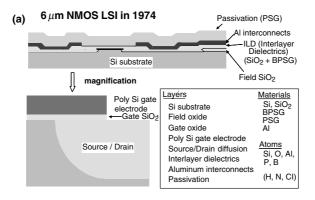

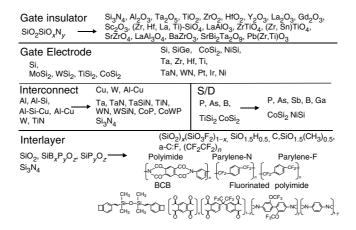

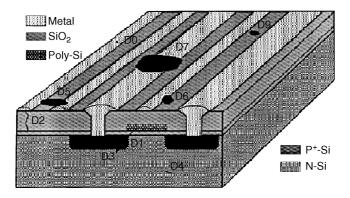

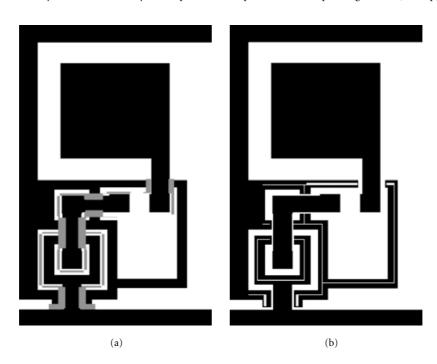

Figure 1.2 shows the cross sections of NMOS LSIs in the early 1970s and those of present CMOS LSIs. The old NMOS LSI technology contains only several film layers made of Si, SiO<sub>2</sub>, and Al, which are basically composed of only five elements: Si, O, Al, B, and P. Now, the structure becomes very complicated, and so many layers and so many elements have been involved.

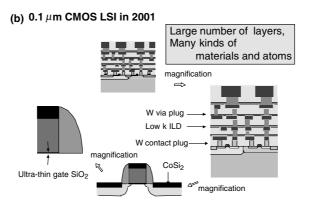

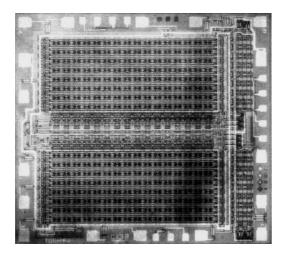

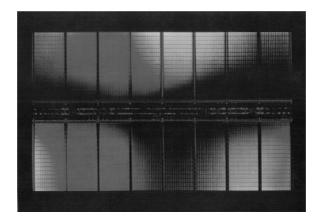

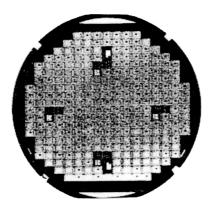

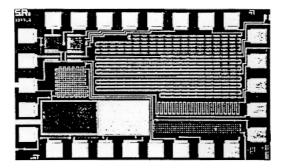

In the past 30 years, transistors have been miniaturized significantly. Thanks to the miniaturization, the number of components and performance of LSIs have increased significantly. Figures 1.3 and 1.4 show the microphotographs of 1 kbit and 256 Mbit DRAM chips, respectively. Individual tiny rectangle units barely recognized in the 16 large rectangle units of the 256 M DRAM correspond to 64 kbit DRAM. It can be said that the downsizing of the components has driven the tremendous development of LSIs.

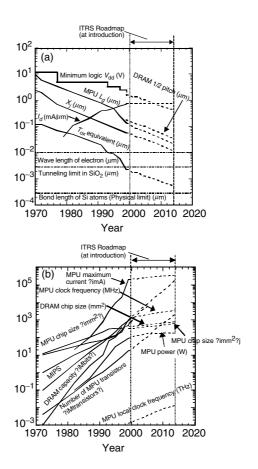

Figure 1.5 shows the past and future trends of the downsizing of MOSFET's parameters and LSI chip properties mainly used for high performance MPUs. Future trend was taken from ITRS'99 (International Technology Roadmap for Semiconductors) [2]. In order to maintain the continuous progress of LSIs for future, every parameter has to be shrunk continuously with almost the same rate as before. However, it was anticipated that shrinking the parameters beyond the  $0.1~\mu m$  generation would face severe difficulties due to various kinds of expected limitations. It was expected that huge effort would be required in research and development level in order to overcome the difficulties.

In this chapter, silicon technology from past to future is reviewed for advanced CMOS LSIs.

FIGURE 1.2 Cross-sections of (a) NMOS LSI in 1974 and (b) CMOS LSI in 2001.

FIGURE 1.3 1 kbit DRAM (TOSHIBA).

FIGURE 1.4 256 Mbit DRAM (TOSHIBA).

FIGURE 1.5 Trends of CPU and DRAM parameters.

### 1.2 Downsizing below 0.1 $\mu$ m

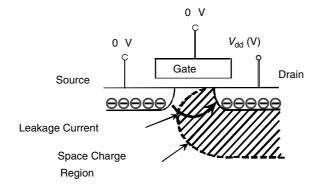

In digital circuit applications, a MOSFET functions as a switch. Thus, complete cut-off of leakage current in the "off" state, and low resistance or high current drive in the "on" state are required. In addition, small capacitances are required for the switch to rapidly turn on and off. When making the gate length small, even in the "off" state, the space charge region near the drain—the high potential region near the drain—touches the source in a deeper place where the gate bias cannot control the potential, resulting in a leakage current from source to drain via the space charge region, as shown in Fig. 1.6. This is the well-known, short-channel effect of MOSFETs. The short-channel effect is often measured as the threshold voltage reduction of MOSFETs when it is not severe. In order for a MOSFET to work as a component of an LSI, the capability of switching-off or the suppression of the short-channel effects is the first priority in the designing of the MOSFETs. In other words, the suppression of the short-channel effects limits the downsizing of MOSFETs.

In the "on" state, reduction of the gate length is desirable because it decreases the channel resistance of MOSFETs. However, when the channel resistance becomes as small as source and drain resistance, further improvement in the drain current or the MOSFET performance cannot be expected. Moreover, in the short-channel MOSFET design, the source and drain resistance often tends to even increase in order to suppress the short-channel effects. Thus, it is important to consider ways for reducing the total resistance of MOSFETs with keeping the suppression of the short-channel effects. The capacitances of MOSFETs usually decreases with the downsizing, but care should be taken when the fringing portion is dominant or when impurity concentration of the substrate is large in the short-channel transistor design.

Thus, the suppression of the short-channel effects, with the improvement of the total resistance and capacitances, are required for the MOSFET downsizing. In other words, without the improvements of the MOSFET performance, the downsizing becomes almost meaningless even if the short-channel effect is completely suppressed.

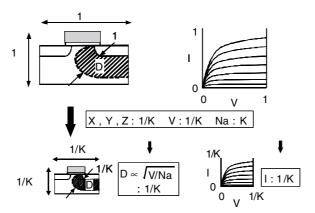

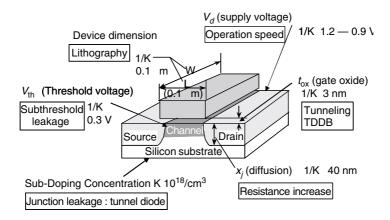

To suppress the short-channel effects and thus to secure good switching-off characteristics of MOSFETs, the scaling method was proposed by Dennard et al. [3], where the parameters of MOSFETs are shrunk or increased by the same factor K, as shown in Figs. 1.7 and 1.8, resulting in the reduction of the space charge region by the same factor K and suppression of the short-channel effects.

In the scaling method, drain current,  $I_d$  (=  $W/L \times V^2/t_{ox}$ ), is reduced to 1/K. Even the drain current is reduced to 1/K, the propagation delay time of the circuit reduces to 1/K, because the gate charge reduces to  $1/K^2$ . Thus, scaling is advantageous for high-speed operation of LSI circuits.

If the increase in the number of transistors is kept at  $K^2$ , the power consumption of the LSI—which is calculated as 1/2fnCV<sup>2</sup> as shown in Fig. 1.7—stays constant and does not increase with the scaling. Thus, in the ideal scaling, power increase will not occur.

FIGURE 1.6 Short channel effect at downsizing.

**TABLE 1.2** Real Scaling (Research Level)

|                               | 1972      | 2001      | Ratio | Limiting<br>Factor      |

|-------------------------------|-----------|-----------|-------|-------------------------|

| Gate length                   | 6 μm      | 0.1 μm    | 1/60  | _                       |

| Gate oxide                    | 100 nm    | 2 nm      | 1/50  | Gate leakage<br>TDDB    |

| Junction depth                | 700 nm    | 35 nm     | 1/20  | Resistance              |

| Supply voltage                | 5 V       | 1.3 V     | 1/3.8 | $V_{ m th}$             |

| Threshold voltage             | 0.8 V     | 0.35 V    | 1/2   | Subthreshold<br>leakage |

| Electric field $(V_d/t_{ox})$ | 0.5 MV/cm | 6.5 MV/cm | 13    | TDDB                    |

Drain Current:  $I_d \rightarrow 1/K$

Gate area:  $S_g = L_g \cdot W_g \rightarrow 1/K^2$

Gate capacitance:  $C_g = a \cdot S_g/\text{tox} \rightarrow 1/\text{K}$ Gate charge:  $Q_g = C_g \cdot V_g \rightarrow 1/\text{K}^2$

Propagation delay time:  $tpd = a \cdot Q_g/I_d \rightarrow 1/K$

Clock frequency:  $f = 1/\text{tpd} \rightarrow K$

Chip area: Sc: set const.  $\rightarrow 1$

Number of Tr. in a chip:  $n \to K^2$

Power consumption:  $P = (1/2) \cdot f \cdot n \cdot C_g \cdot V_d^2 \rightarrow 1$  $K K^{2} 1/k 1/k^{2}$

FIGURE 1.7 Parameters change by ideal scaling.

**FIGURE 1.8** Ideal scaling method.

However, the actual scaling of the parameters has been different from that originally proposed as the ideal scaling, as shown in Table 1.2 and also shown in Fig. 1.5(a). The major difference is the supply voltage reduction. The supply voltage was not reduced in the early phase of LSI generations in order to keep a compatibility with the supply voltage of conventional systems and also in order to obtain higher operation speed under higher electric field. The supply voltage started to decrease from the 0.5  $\mu$ m generation because the electric field across the gate oxide would have exceeded 4 MV/cm, which had been regarded as the limitation in terms of TDDB (time-dependent break down)—recently the maximum field is going to be raised to high values, and because hot carrier induced degradation for the shortchannel MOSFETs would have been above the allowable level; however, now, it is not easy to reduce the

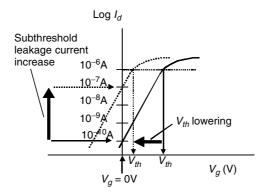

**FIGURE 1.9** Subthreshold leakage current at low  $V_{th}$ .

**FIGURE 1.10** Scaling limitation factor for Si MOSFET below 0.1  $\mu$ m.

supply voltage because of difficulties in reducing the threshold voltage of the MOSFETs. Too small threshold voltage leads to significantly large subthreshold leakage current even at the gate voltage of 0 V, as shown in Fig. 1.9. If it had been necessary to reduce the supply voltage of 0.1  $\mu$ m MOSFETs at the same ratio as the dimension reduction, the supply voltage would have been 0.08 V (=5 V/60) and the threshold voltage would have been 0.0013 V (=0.8 V/60), and thus the scaling method would have been broken down. The voltage higher than that expected from the original scaling is one of the reasons for the increase of the power. Increase of the number of transistors in a chip by more than the factor  $K^2$  is another reason for the power increase. In fact, the transistor size decreases by factor 0.7 and the transistor area decreases by factor 0.5 (=0.7 × 0.7) for every generation, and thus the number of transistors is expected to increase by a factor of 2. In reality, however, the increase cannot wait for the downsizing and the actual increase is by a factor of 4. The insufficient area for obtaining another factor 2 is earned by increasing the chip area by a factor of 1.5 and further by extending the area in the vertical direction introducing multilayer interconnects, double polysilicon, and trench/stack DRAM capacitor cells.

In order to downsizing MOSFETs down to sub-0.1  $\mu$ m, further modification of the scaling method is required because some of the parameters have already reached their scaling limit in the 0.1  $\mu$ m generation, as shown in Fig. 1.10. In the 0.1  $\mu$ m generation, the gate oxide thickness is already below the direct-tunneling leakage limit of 3 nm. The substrate impurity concentration (or the channel impurity concentration) has already reached  $10^{18}$ cm<sup>-3</sup>. If the concentration is further increased, the source-substrate and drain-substrate junctions become highly doped pn junctions and act as tunnel diodes. Thus, the isolation of source and drains with substrate cannot be maintained. The threshold voltage has already

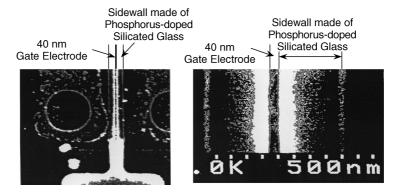

### 40 nm gate length MOSFETs Dec. 1993

### Top-view of Gate Electrode and Sidewalls

FIGURE 1.11 Top view of 40 nm gate length MOSFETs [4].

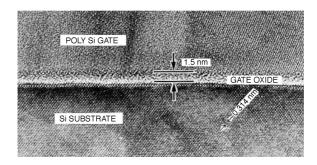

### 1.5 nm gate oxide MOSFETs Dec 1994

### TEM photograph of 1.5 nm gate oxide

FIGURE 1.12 Cross-sectional TEM image of 1.5 nm gate oxide [5].

decreased to 0.3–0.25 V and further reduction causes significant increase in subthreshold leakage current. Further reduction of the threshold voltage and thus the further reduction of the supply voltage are difficult.

In 1990s, fortunately, those difficulties were shown to be solved somehow by invention of new techniques, further modification of the scaling, and some new findings for short gate length MOSFET operation. In the following, examples of the solutions for the front end of line are described. In 1993, first successful operation of sub-50 nm n-MOSFETs was reported [4], as shown in Fig. 1.11. In the fabrication of the MOSFETs, 40 nm length gate electrodes were realized by introducing resist-thinning technique using oxygen plasma. In the scaling, substrate (or channel doping) concentration was not increased any more, and the gate oxide thickness was not decreased (because it was not believed that MOSFETs with direct-tunnelling gate leakage operates normally), but instead, decreasing the junction depth more aggressively (in this case) than ordinary scaling was found to be somehow effective to suppress the short-channel effect and thus to obtain good operation of sub-50 nm region. Thus, 10-nm depth S/D junction was realized by introduction of solid-phase diffusion by RTA from PSG gate sidewall. In 1994, it was found that MOSFETs with gate SiO<sub>2</sub> less than 3 nm thick—for example 1.5 nm as shown in Fig. 1.12 [5]—operate quite normally when

### Epi Channel MOSFETs June 1993 Epitaxial channel Channel ion implantation Under the state of t

MOSFET fabrication

FIGURE 1.13 Epitaxial channel [9].

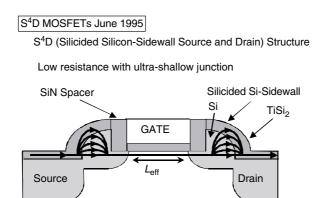

FIGURE 1.14 S<sup>4</sup>D MOSFETs [9].

the gate length is small. This is because the gate leakage current decreases in proportion with the gate length while the drain current increases in inverse proportion with the gate length. As a result, the gate leakage current can be negligibly small in the normal operation of MOSFETs. The performance of 1.5 nm was record breaking even at low supply voltage.

In 1993, it was proposed that ultrathin-epitaxial layer shown in Fig. 1.13 is very effective to realize super retrograde channel impurity profiles for suppressing the short-channel effects. It was confirmed that 25 nm gate length MOSFETs operate well by using simulation [6]. In 1993 and 1995, epitaxial channel MOSFETs with buried [7] and surface [8] channels, respectively, were fabricated and high drain current drive with excellent suppression of the short-channel effects were experimentally confirmed. In 1995, new raised (or elevated) S/D structure was proposed, as shown in Fig. 1.14 [10]. In the structure, extension portion of the S/D is elevated with self-aligned to the gate electrode by using silicided silicon sidewall. With minimizing the Si<sub>3</sub>N<sub>4</sub> spacer width, the extension S/D resistance was dramatically reduced. In 1991, NiSi salicide were presented for the first time, as shown in Fig. 1.15 [10]. NiSi has several advantages over TiSi<sub>2</sub> and CoSi<sub>2</sub> salicides, especially in use for sub-50 nm regime. Because NiSi is a monosilicide, silicon consumption during the silicidation is small. Silicidation can be accomplished at low temperature. These features are suitable for ultra-shallow junction formation. For NiSi salicide, there

## NiSi Salicide Dec 1991 Cross-section TiSi<sub>2</sub> $0.1 \, \mu m$ NiSi Poly Si

FIGURE 1.15 NiSi Salicide [10].

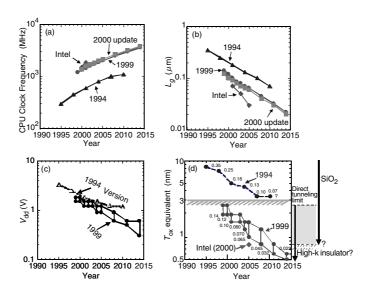

FIGURE 1.16 ITRS'99. (a) CPU clock frequency, (b) gate length, (c) supply voltage, and (d) gate insulator thickness.

was no narrow line effect—increase in the sheet resistance in narrow silicide line—and bridging failure by the formation of silicide path on the gate sidewall between the gate and S/D. NiSi-contact resistances to both  $n^+$  and  $p^+$  Si are small. These properties are suitable for reducing the source, drain, and gate resistance for sub-50 nm MOSFETs.

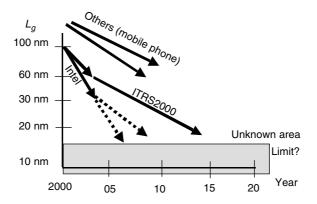

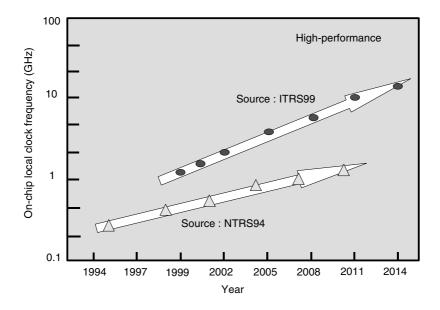

The previous discussion provides examples of possible solutions, which the authors found in the 1990s for sub-50 nm gate length generation. Also, many solutions have been found by others. In any case, with the possible solutions demonstrated for sub-50 nm generation as well as the keen competitions among semiconductor chipmakers for high performance, the downsizing trend or roadmap has been significantly accelerated since late 1990s, as shown in Fig. 1.16. The first roadmap for downsizing was published in 1994 by SIA (Semiconductor Industry Association, USA) as NTRS'94 (National Technology Roadmap for Semiconductors) [11]—at that time, the roadmap was not an international version. On NTRS'94, the clock frequency was expected to stay at 600 MHz in year 2001 and expected to exceed 1 GHz in 2007. However, it has already reached 2.1 GHz for 2001 in ITRS 2000 [12]. In order to realize high clock frequencies, the

gate length reduction was accelerated. In fact, in the NTRS'94, gate length was expected to stay at 180 nm in year 2001 and expected to reach 100 nm only in 2007, but the gate length is 90 nm in 2001 on ITRS 2000, as shown in Fig. 1.16(b).

The real world is much more aggressive. As shown in Fig. 1.16(a), the clock frequency of Intel's MPU already reached 1.7 GHz [12] in April 2001, and its roadmap for gate length reduction is unbelievably aggressive, as shown in Fig. 1.16(b) [13,14]. In the roadmap, 30-nm gate length CMOS MPU with 70-nm node technology is to be sold in the market in year 2005. It is even several years in advance compared with the ITRS 2000 prediction.

With the increase in clock frequency and the decrease in gate length, together with the increase in number of transistors in a chip, the tremendous increase in power consumption becomes the main issue. In order to suppress the power consumption, supply voltage should be reduced aggressively, as shown in Fig. 1.16(c). In order to maintain high performance under the low supply voltage, gate insulator thickness should be reduced very tremendously. On NTRS'94, the gate insulator thickness was not expected to exceed 3 nm throughout the period described in the roadmap, but it is already 1.7 nm in products in 2001 and expected to be 1.0 nm in 2005 on ITRS'99 and 0.8 nm in Intel's roadmap, as shown in Fig. 1.16(d). In terms of total gate leakage current of an entire LSI chip for use for mobile cellular phone, 2 nm is already too thin, in which standby power consumption should be minimized. Thus, high K materials, which were assumed to be introduced after year 2010 at the earliest on NTRS'94, are now very seriously investigated in order to replace the SiO<sub>2</sub> and to extend the limitation of gate insulator thinning.

Introduction of new materials is considered not only for the gate insulator, but also almost for every portion of the CMOS structures. More detailed explanations of new technology for future CMOS will be given in the following sections.

### 1.3 Gate Insulator

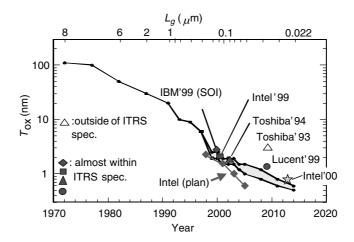

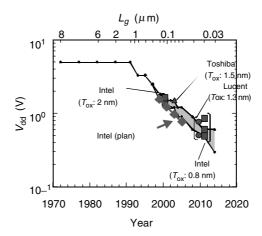

Figure 1.17 shows gate length  $(L_g)$  versus gate oxide thickness  $(t_{ox})$  published in recent conferences [4,5,14–19]. The x-axis in the bottom represents corresponding year of the production to the gate length according to ITRS 2000. The solid curve in the figure is  $L_g$  versus  $t_{ox}$  relation according to the ITRS 2000 [12]. It should be noted that most of the published MOSFETs maintain the scaling relationship between  $L_g$  and  $t_{ox}$  predicted by ITRS 2000. Figures 1.18 and 1.19 are  $V_d$  versus  $L_g$ , and  $I_d$  (or  $I_{on}$ ) versus  $L_g$  curves, respectively obtained from the published data at the conferences. From the data, it can be estimated that MOSFETs will operate quite well with satisfaction of  $I_{on}$  value specified by the roadmap until the generation

**FIGURE 1.17** Trend of  $T_{ox}$ .

**FIGURE 1.18** Trend of  $V_{\rm dd}$ .

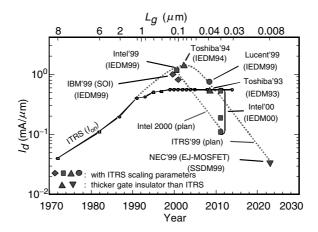

FIGURE 1.19 Trend of drain current.

around  $L_g = 30$  nm. One small concern is that the  $I_{\rm on}$  starts to reduce from  $L_g = 100$  nm and could be smaller than the value specified by the roadmap from  $L_g = 30$  nm. This is due to the increase in the S/D extension resistance in the small gate length MOSFETs. In order to suppress the short-channel effects, the junction depth of S/D extension needs to be reduced aggressively, resulting in high sheet resistance. This should be solved by the raised (or elevated) S/D structures. This effect is more significantly observed in the operation of an 8-nm gate length EJ-MOSFET [20], as shown in Fig. 1.19. In the structure, S/D extension consists of inversion layer created by high positive bias applied on a 2nd gate electrode, which is placed to cover the 8-nm, 1st gate electrode and S/D extension area. Thus, reduction of S/D extension resistance will be another limiting factor of CMOS downsizing, which will come next to the limit in thinning the gate SiO<sub>2</sub>.

In any case, it seems at this moment that  $SiO_2$  gate insulator could be used until the sub-1 nm thickness with sufficient MOSFET performance. There was a concern proposed in 1998 that TDDB (Time Dependent Dielectric Breakdown) will limit the  $SiO_2$  gate insulator reduction at  $t_{ox} = 2.2$  nm [21]; however, recent results suggest that TDDB would be OK until  $t_{ox} = 1.5 - 1.0$  nm [22–25]. Thus,  $SiO_2$  gate insulator would be used until the 30 nm gate length generation for high-speed MPUs. This is a big change

of the prediction. Until only several years ago, most of the people did not believe the possibility of gate SiO<sub>2</sub> thinning below 3 nm because of the direct-tunnelling leakage current, and until only 2 years ago, many people are sceptical about the use of sub-2 nm gate SiO<sub>2</sub> because of the TDDB concern.

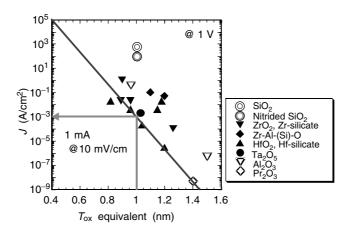

However, even excellent characteristics of MOSFETs with high reliability was confirmed, total gate leakage current in the entire LSI chip would become the limiting factor. It should be noted that  $10 \text{ A/cm}^2$  gate leakage current flows across the gate  $SiO_2$  at  $t_{ox} = 1.2 \text{ nm}$  and  $100 \text{ A/cm}^2$  leakage current flows at  $t_{ox} = 1.0 \text{ nm}$ . However, AMD has claimed that 1.2 nm gate  $SiO_2$  (actually oxynitrided) can be used for high end MPUs [26]. Furthermore, Intel has announced that total-chip gate leakage current of even  $100 \text{ A/cm}^2$  is allowable for their MPUs [14], and that even 0.8 nm gate  $SiO_2$  (actually oxynitrided) can be used for product in 2005 [15].

Total gate leakage current could be minimized by providing plural gate oxide thicknesses in a chip, and by limiting the number of the ultra-thin transistors; however, in any case, such high gate leakage current density is a big burden for mobile devices, in which reduction of standby power consumption is critically important. In the cellular phone application, even the leakage current at  $t_{ox} = 2.5$  nm would be a concern. Thus, development of high dielectric constant (or high-k) gate insulator with small gate leakage current is strongly demanded; however, intensive study and development of the high-k gate dielectrics have started only a few years ago, and it is expected that we have to wait at least another few years until the high-k insulator becomes mature for use of the production.

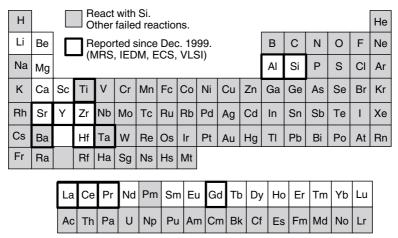

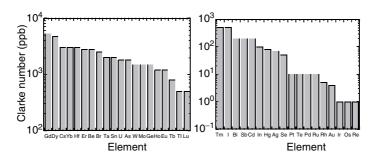

The necessary conditions for the dielectrics are as follows [27]: (i) the dielectrics remain in the solid-phase at the process temperature of up to about 1000 K, (ii) the dielectrics are not radio-active, (iii) the dielectrics are chemically stable at the Si interface at high process temperature. This means that no barrier film is necessary between the Si and the dielectrics. Considering the conditions, white columns in the periodic law of the elements shown in Fig. 1.20 remained as metals whose oxide could be used as the high-k gate insulators [27]. It should be noted that  $Ta_2O_5$  is now regarded as not very much suitable for use as the gate insulator of MOSFET from this point of view.

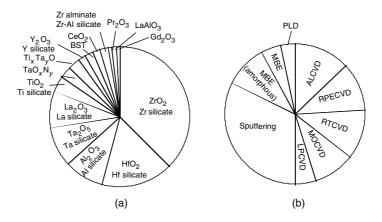

Figure 1.21 shows the statistics of high-k dielectrics—excluding  $Si_3N_4$ —and its formation method published recently [28–43]. In most of the cases, 0.8–2.0 nm capacitance equivalent thicknesses to  $SiO_2$  (CET) were tested for the gate insulator of MOS diodes and MOSFETs and leakage current of several orders of magnitude lower value than that of  $SiO_2$  film was confirmed. Also, high TDDB reliability than that of the  $SiO_2$  case was reported.

Plotted on the material given by J. R. Hauser at IEDM Short Course on Sub-100 nm CMOS (1999)

FIGURE 1.20 Metal oxide gate insulators reported since Dec. 1998 [27].

FIGURE 1.21 Recently reported (a) high-k materials and (b) deposition methods.

Among the candidates,  $ZrO_2$  [29–31,34–37] and  $HfO_2$  [28,32,34,36,38–40] become popular because their dielectric constant is relatively high and because  $ZrO_2$  and  $HfO_2$  were believed to be stable at the Si interface. However, in reality, formation and growth of interfacial layer made of silicate ( $ZrSi_xO_y$ ,  $HfSi_xO_y$ ) or  $SiO_2$  at the Si interface during the MOSFET fabrication process has been a serious problem. This interfacial layer acts to reduce the total capacitance and is thought to be undesirable for obtaining high performance of MOSFETs. Ultrathin nitride barrier layer seems to be effective to suppress the interfacial layer formation [37]. There is a report that mobility of MOSFETs with  $ZrO_2$  even with these interfacial layers were significantly degraded by several tens of percent, while with entire Zr silicate gate dielectrics is the same as that of  $SiO_2$  gate film [31]. Thus, there is an argument that the thicker interfacial silicate layer would help the mobility improvement as well as the gate leakage current suppression; however, in other experiment, there is a report that  $HfO_2$  gate oxide MOSFETs mobility was not degraded [38]. For another problem, it was reported that  $ZrO_2$  and  $HfO_2$ , easily form micro-crystals during the heat process [31,33].

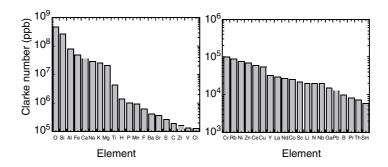

Comparing with the cases of ZrO<sub>2</sub> and HfO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub> film was reported to have better characteristics at this moment [33]. There was no interfacial silicate layer formed, and mobility was not degraded at all. The dielectric constant was 20–30. Another merit of the La<sub>2</sub>O<sub>3</sub> insulator is that no micro-crystal formation was found in high temperature process of MOSFET fabrication [33]. There is a strong concern for its hygroscopic property, although it was reported that the property was not observed in the paper [33]. However, there is a different paper published [34], in which La<sub>2</sub>O<sub>3</sub> film is reported to very easily form a silicate during the thermal process. Thus, we have to watch the next report of the La<sub>2</sub>O<sub>3</sub> experiments. Crystal Pr<sub>2</sub>O<sub>3</sub> film grown on silicon substrate with epitaxy is reported to have small leakage current [42]. However, it was shown that significant film volume expansion by absorbing the moisture of the air was observed. La and Pr are just two of the 15 elements in lanthanoids series. There might be a possibility that any other lanthanoid oxide has even better characteristics for the gate insulator. Fortunately, the atomic content of the lanthanoids, Zr, and Hf in the earth's crust is much larger than that of Ir, Bi, Sb, In, Hg, Ag, Se, Pt, Te, Ru, Au, as shown in Fig. 1.22.

$Al_2O_3$  [41,43] is another candidate, though dielectric constant is around 10. The biggest problem for the  $Al_2O_3$  is that film thickness dependence of the flatband shift due to the fixed charge is so strong that controllability of the flatband voltage is very difficult. This problem should be solved before it is used for the production. There is a possibility that Zr, Hf, La, and Pr silicates are used for the next generation gate insulator with the sacrifice of the dielectric constant to around 10 [31,35,37]. It was reported that the silicate prevent from the formation of micro-crystals and from the degradation in mobility as described before. Furthermore, there is a possibility that stacked  $Si_3N_4$  and  $SiO_2$  layers are used for mobile device application.  $Si_3N_4$  material could be introduced soon even though its dielectric constant is not very high [44–46], because it is relatively mature for use for silicon LSIs.

FIGURE 1.22 Clarke number of elements.

### 1.4 Gate Electrode

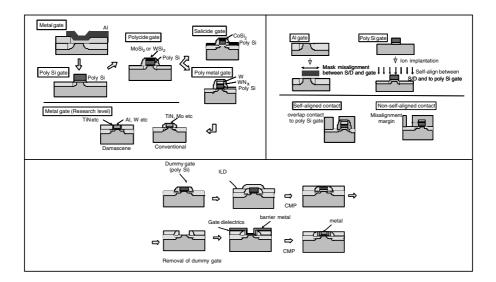

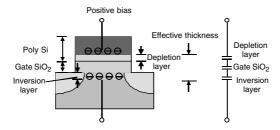

Figure 1.23 shows the changes of the gate electrode of MOSFETs. Originally, Al gate was used for the MOSFETs, but soon poly Si gate replaced it because of the adaptability to the high temperature process and to the acid solution cleaning process of MOSFET fabrication. Especially, poly gate formation step can be put before the S/D (source and drain) formation. This enables the easy self-alignment of S/D to the gate electrode as shown in the figure. In the metal gate case, the gate electrode formation should come to the final part of the process to avoid the high temperature and acid processes, and thus self-alignment is difficult. In the case of damascene gate process, the self-alignment is possible, but process becomes complicated as shown in the figure [47]. Refractory metal gate with conventional gate electrode process and structure would be another solution, but RIE (Reactive Ion Etching) of such metals with good selectivity to the gate dielectric film is very difficult at this moment.

As shown in Fig. 1.24, poly Si gate has a big problem of depletion layer formation. This effect would not be ignored when the gate insulator becomes thin. Thus, despite the above difficulties, metal gate is desirable and assumed to be necessary for future CMOS devices. However, there is another difficulty for the introduction of metal gate to CMOS. For advance CMOS, work function of gate electrode should be selected differently for n- and p-MOSFETs to adjust the threshold voltages to the optimum values. Channel doping could shift the threshold voltage, but cannot adjust it to the right value with good control of the short-channel effects. Thus, n<sup>+</sup>-doped poly Si gate is used for NMOS and p<sup>+</sup>-doped poly Si gate is used for PMOS. In the metal gate case, it is assumed that two different metals should be used for N- and PMOS in the same manner as shown in Table 1.3. This makes the process further complicated and makes the device engineer to hesitate to introduce the metal gate. Thus, for the short-range—probably to 70 or 50 nm node, heavily doped poly Si or poly SiGe gate electrode will be used. But in the long range, metal gate should be seriously considered.

**TABLE 1.3** Candidates for Metal Gate Electrodes (unit: eV)

|        |      | Dual Gate |              |                                |                      |  |  |

|--------|------|-----------|--------------|--------------------------------|----------------------|--|--|

| Midgap |      | N         | NMOS         |                                | OS                   |  |  |

| W      | 4.52 | Hf<br>Zr  | 3.9<br>4.05  | $RuO_2$ WN                     | 4.9<br>5.0           |  |  |

| Ru     | 4.71 | Al<br>Ti  | 4.08<br>4.17 | Ni<br>Ir                       | 5.15<br>5.27         |  |  |

| TiN    | 4.7  | Ta<br>Mo  | 4.19<br>4.2  | Mo <sub>2</sub> N<br>TaN<br>Pt | 5.33<br>5.41<br>5.65 |  |  |

FIGURE 1.23 Gate electrode formation change.

FIGURE 1.24 Depletion in poly-Si gate.

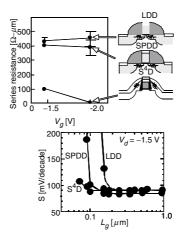

# 1.5 Source and Drain

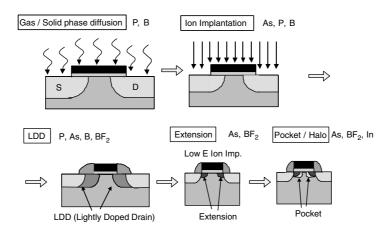

Figure 1.25 shows the changes of S/D (source and drain) formation process and structure. S/D becomes shallower for every new generation in order to suppress the short-channel effects. Before, the extension part of the S/D was called as LDD (Lightly Doped Drain) region and low doping concentration was required in order to suppress electric field at the drain edge and hence to suppress the hot-carrier effect. Structure of the source side becomes symmetrical as the drain side because of process simplicity. Recently, major concern of the S/D formation is how to realize ultra-shallow extension with low resistance. Thus, the doping of the extension should be done as heavily as possible and the activation of the impurity should be as high as possible. Table 1.4 shows the trends of the junction depth and sheet resistance of the extension requested by ITRS 2000. As the generation proceeds, junction depth becomes shallower, but at the same time, the sheet resistance should be reduced. This is extremely difficult. In order to satisfy this request, various doping and activation methods are being investigated. As the doping method, low energy implantation at 2-0.5 keV [48] and plasma doping with low energy [49] are thought to be the most promising at this moment. The problem of the low energy doping is lower retain dose and lower activation rate of the implanted species [48]. As the activation method, high temperature spike lamp anneal [48] is the best way at this moment. In order to suppress the diffusion of the dopant, and to keep the over-saturated activation of the dopant, the spike should be as steep as possible. Laser anneal [50] can realize very high activation, but very high temperature above the melting point at the silicon surface is a concern. Usually laser can anneal only the surface of the doping layer, and thus deeper portion may be necessary to be annealed by the combination of the spike lamp anneal.

**TABLE 1.4** Trend of S/D Extension by ITRS

|                                            | 1999    | 2000    | 2001    | 2002    | 2003    | 2004    | 2005    | 2008    | 2011    | 2014    |

|--------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Technology<br>node (nm)                    | 180     |         |         | 130     |         |         | 100     | 70      | 50      | 35      |

| Gate length (nm)                           | 140     | 120     | 100     | 85      | 80      | 70      | 65      | 45      | 32      | 22      |

| Extension $X_i$ (nm)                       | 42 - 70 | 36-60   | 30-50   | 25-43   | 24-40   | 20-35   | 20-33   | 16-26   | 11-19   | 8-13    |

| Extension sheet resistance $(\Omega/\Box)$ | 350-800 | 310–760 | 280-730 | 250–700 | 240–675 | 220–650 | 200–625 | 150–525 | 120–450 | 100–400 |

**FIGURE 1.25** Source and drain change.

TABLE 1.5 Physical Properties of Silicides

|                               | MoSi <sub>2</sub> | $WSi_2$ | C54–TiSi <sub>2</sub> | CoSi <sub>2</sub> | NiSi  |

|-------------------------------|-------------------|---------|-----------------------|-------------------|-------|

| Resistivity ( $\mu\Omega$ cm) | 100               | 70      | 10~15                 | 18~25             | 30~40 |

| Forming temperature (°C)      | 1000              | 950     | 750~900               | 550~900           | 400   |

| Diffusion species             | Si                | Si      | Si                    | Co*               | Ni    |

<sup>\*</sup>Si(CoSi), Co(Co<sub>2</sub>Si).

FIGURE 1.26 Elevated source and drain.

In order to further reduce the sheet resistance, elevated S/D structure of the extension is necessary, as shown in Fig. 1.26 [6]. Elevated S/D will be introduced at the latest from the generation of sub-30 nm gate length generation, because sheet resistance of S/D will be the major limiting factor of the device performance in that generation.

Salicide is a very important technique to reduce the resistance of the extrinsic part of S/D—resistance of deep S/D part and contact resistance between S/D and metal. Table 1.5 shows the changes of the salicide/silicide materials. Now  $CoSi_2$  is the material used for the salicide. In future, NiSi is regarded as promising because of its superior nature of smaller silicon consumption at the silicidation reaction [10].

# 1.6 Channel Doping

Channel doping is an important technique not only for adjusting the threshold voltage of MOSFETs but also for suppressing the short-channel effects. As described in the explanation of the scaling method, the doping of the substrate or the doping of the channel region should be increased with the downsizing of the device dimensions; however, too heavily doping into the entire substrate causes several problems, such as too high threshold voltage and too low breakdown voltage of the S/D junctions. Thus, the heavily doping portion should be limited to the place where the suppression of the depletion layer is necessary, as shown in Fig. 1.27. Thus, retrograde doping profile in which only some deep portion is heavily doped is requested. To realize the extremely sharp retrograde profile, undoped-epitaxial-silicon growth on the heavily doped channel region is the most suitable method, as shown in the figure [7–9]. This is called as epitaxial channel technique. The epitaxial channel will be necessary from sub-50 nm gate length generations.

**FIGURE 1.27** Retrograde profile.

FIGURE 1.28 Interconnect change.

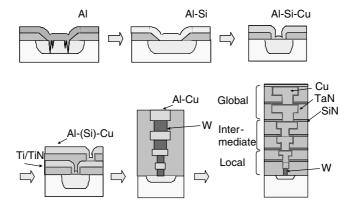

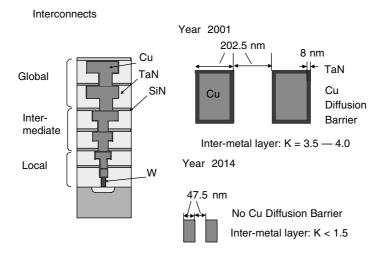

## 1.7 Interconnects

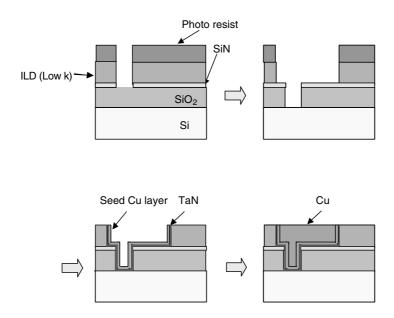

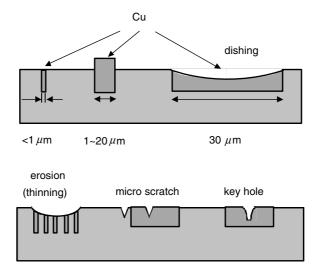

Figure 1.28 shows the changes of interconnect structures and materials. Aluminium has been used for many years as the interconnect metal material, but now it is being replaced by cupper with the combination of dual damascene process shown in Fig. 1.29, because of its superior characteristics on the resistivity and electromigration [51,52]. Figure 1.30 shows some problems for the CMP process used for the copper damascene, which is being solved. The major problem for future copper interconnects is the necessity of diffusion barrier layer, as shown in Fig. 1.31. The thickness of the barrier layer will consume major part of the cross-section area of copper interconnects with the reduction of the dimension, because it is very difficult to thin the barrier films less than several nanometers. This leads to significant increase in the resistance of the interconnects. Thus, in 10 years, diffusion-barrier-free copper interconnects process should be developed.

FIGURE 1.29 Dual damascene for Cu.

FIGURE 1.30 Dual damascene for Cu.

Reducing the interconnect capacitance is very important for obtaining high-speed circuit operation. Thus, development of low-k inter-deposition layer (IDL) is essential for the future interconnects shown in Table 1.6. Various materials as shown in Table 1.7 are being developed at this moment. Unfortunately, however, only the dielectric constant of 3.2–4.0 has been used for the products. Originally, low-k material with dielectric constant of less than 3.0 was scheduled to be introduced much earlier. However, because of the technological difficulty, the schedule was delayed in ITRS 2000, as shown in Table 1.6.

TABLE 1.6 Trend of Interconnect by ITRS

|                                  | 1999       | 2000        | 2001      | 2002      | 2003      | 2004        | 2005    | 2008                           | 2011     | 2014       |

|----------------------------------|------------|-------------|-----------|-----------|-----------|-------------|---------|--------------------------------|----------|------------|

| Technology node (nm)             | 180        |             |           | 130       |           |             | 100     | 70                             | 50       | 35         |

| Gate length (nm)                 | 140        | 120         | 100       | 85        | 80        | 70          | 65      | 45                             | 32       | 22         |

| Number of metal levels           | 6–7        | 6–7         | 7         | 7–8       | 8         | 8           | 8–9     | 9                              | 9–10     | 9–10       |

| Local (AI or Cu)<br>(nm)         | 500        | 450         | 405       | 365       | 330       | 295         | 265     | 185                            | 130      | 95         |

| Intermediate (AI or Cu) (nm)     | 640        | 575         | 520       | 465       | 420       | 375         | 340     | 240                            | 165      | 115        |

| Global (AI or Cu)<br>(nm)        | 1050       | 945         | 850       | 765       | 690       | 620         | 560     | 390                            | 275      | 190        |

| Dielectric constant (κ)          | 3.5–4.0    | 3.5–4.0     | 2.7–3.5   | 2.7–3.5   | 2.2-2.7   | 2.2-2.7     | 1.6–2.2 | 1.5                            | <1.5     | <1.5       |

| Interlevel metal                 | Fluorinate | ed silicate | Hydi      | rogen     | Organic   | polymer     | Xei     | rogel                          | Porous d | ielectrics |

| insulator                        | gla        | iss         | silsesqio | kane-type | Inorganic | dielectrics | Fluoro  | polymer<br>1s SiO <sub>2</sub> | and a    | ir gap     |

| Dielectric constant (κ) for DRAM | 4.1        | 4.1         | 4.1       | 3.0-4.1   | 3.0-4.1   | 3.0–4.1     | 2.5–3.0 | 2.5–3.0                        | 2.0–2.5  | 2.0–2.3    |

FIGURE 1.31 Interconnects.

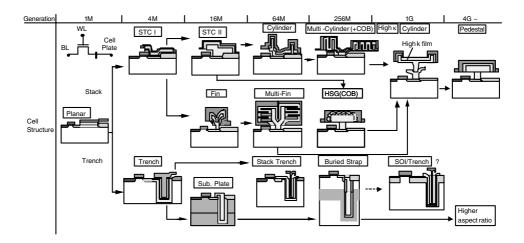

# 1.8 Memory Technology

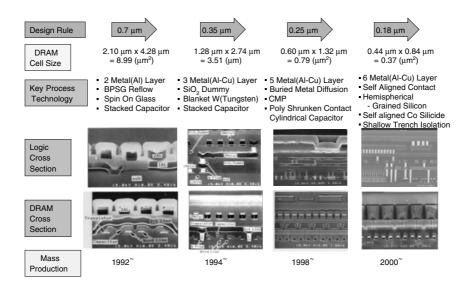

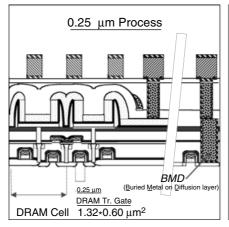

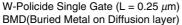

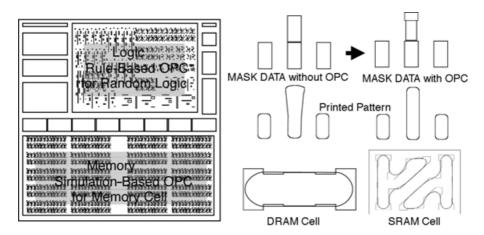

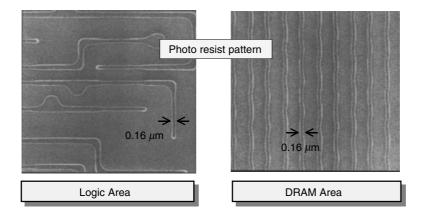

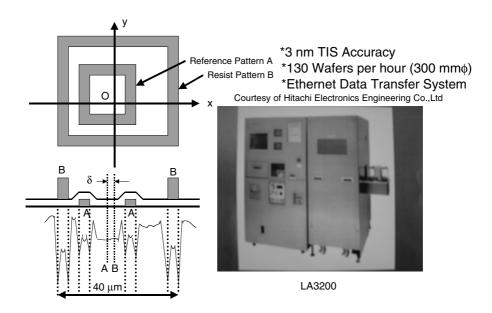

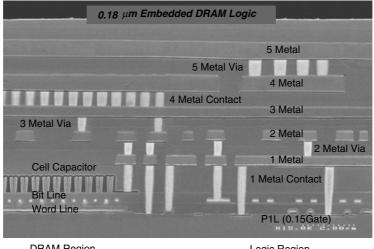

Memory device requires some special technologies. Figure 1.32, and Tables 1.8 and 1.9 show the change of DRAM cells. The cell structure becomes too complicated in order to secure the capacitor area in the small dimensions. To solve this problem, new high-k dielectrics and related metal electrode as shown in Table 1.8 have been already developed for production and new materials are also being investigated for future [53]. New dielectric materials are being developed not only for DRAM, but also for other memories such as FERAMs (Ferro-electric RAM) [54].

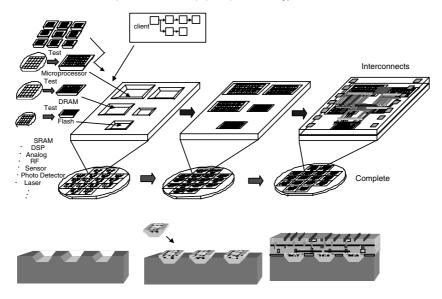

Although, the structure becomes very complicated, embedded DRAM logic LSIs [55] are attractive and necessary for the SOC (Silicon On a Chip) application. In the future, chip module technology will solve the complexity problem in which different functional chips are made separately and finally assembled on a chip.

TABLE 1.7 Candidates of Low-k Materials for Next Generation Interconnects

| Low $\kappa$ Materials     | erials Chemical Formula                                                                                                                                        |         | Deposition Method |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|

| Silicon dioxide            | SiO <sub>2</sub>                                                                                                                                               | 3.9–4.5 | PECVD             |

| Fluorinated silicate glass | $(SiO_2)_x \cdot (SiO_3F_2)_{1-x}$                                                                                                                             | 3.2-4.0 | PECVD             |

| Polyimide                  | $\left\{\begin{array}{c} N \\ CO \end{array}\right\} \left\{\begin{array}{c} CO \\ CO \end{array}\right\} \left\{\begin{array}{c} N \\ CO \end{array}\right\}$ | 3.1–3.4 | Spin on           |

| HSQ                        | $SiO_{1.5}H_{0.5}$                                                                                                                                             | 2.9-3.2 | Spin on           |

| Diamond-like carbon        | С                                                                                                                                                              | 2.7-3.4 | PECVD             |

| Parylene-N                 | $CH_2$                                                                                                                                                         | 2.7     | CVD               |

| DVS-BCB                    | (1)                                                                                                                                                            | 2.6-2.7 | Spin on           |

| Fluorinated polyimide      | (2)                                                                                                                                                            | 2.5-2.9 | Spin on           |

| MSQ                        | $SiO_{1.5}(CH_3)_{0.5}$                                                                                                                                        | 2.6-2.8 | Spin on           |

| Aromatic thermoset         | $-CF_2$                                                                                                                                                        | 2.6–2.8 | Spin on           |

| Parylene-F                 | a-C:F                                                                                                                                                          | 2.4-2.5 | CVD               |

| Teflon AF                  | $(CF_2CF_2)_n$                                                                                                                                                 | 2.1     | Spin on           |

| Mesoporous silica          | $SiO_2$                                                                                                                                                        | 2.0     | Spin on           |

| Porous HSQ                 | $SiO_{1.5}H_{0.5}$                                                                                                                                             | 2.0     | Spin on           |

| Porous aero gel            | $SiO_2$                                                                                                                                                        | 1.8-2.2 | Spin on           |

| Porous PTFE                | $(CF_2CF_2)_n$                                                                                                                                                 | 1.8-2.2 | Spin on           |

| Porous MSQ                 | $SiO_{1.5}(CH_3)_{0.5}$                                                                                                                                        | 1.7-2.2 | Spin on           |

| Xerogels (porous silica)   | $SiO_2$                                                                                                                                                        | 1.1–2.2 | Spin on           |

HSQ : Hydrogen Silsesquioxane

BCB : Benzocyclobutene MSQ : Methyl Silsesquioxane

Teflon: (PTFE+2,2 bis-trifluromethyl-4,5 difluoro-1,3 dioxole)

PTFE: Polytetrafluoroethylene

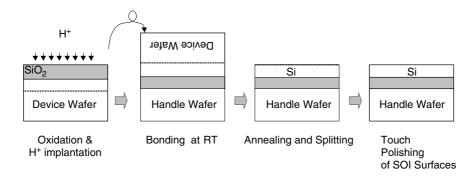

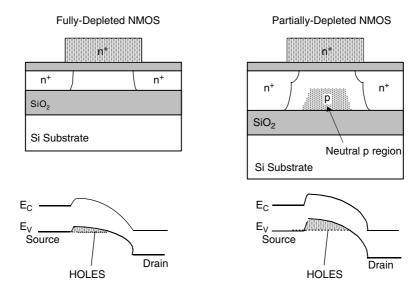

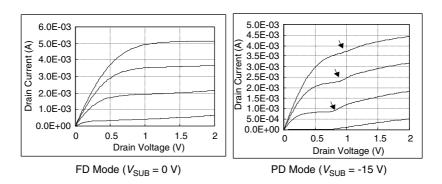

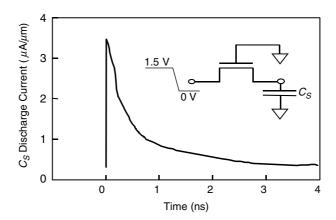

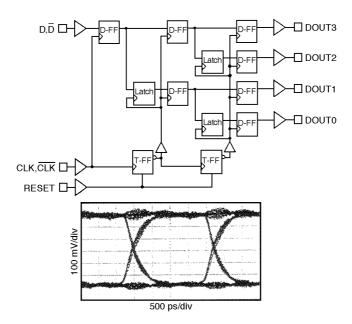

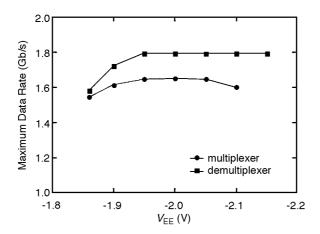

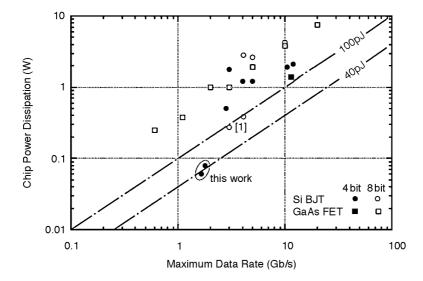

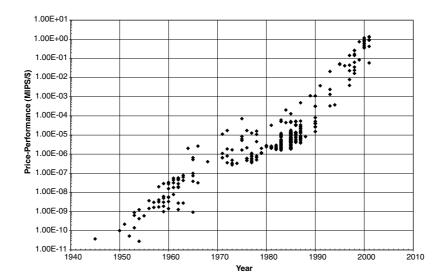

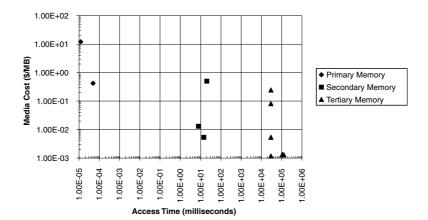

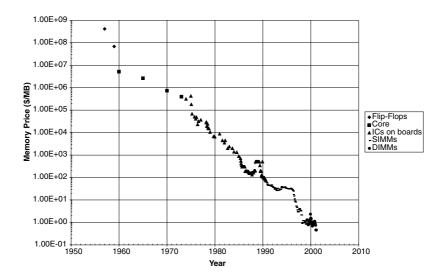

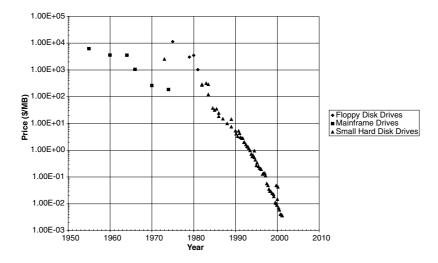

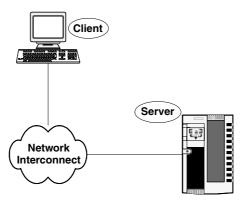

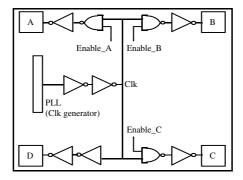

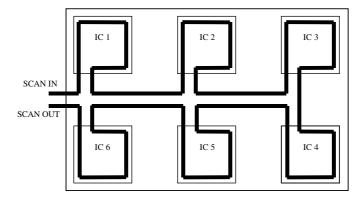

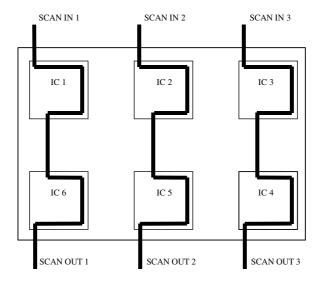

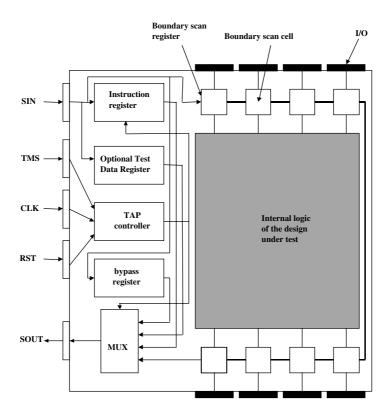

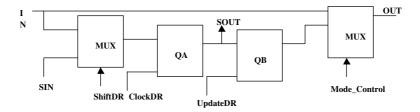

$$(1) \begin{bmatrix} \mathsf{CH_3} & \mathsf{CH_3} \\ \mathsf{Si-O-Si} \\ \mathsf{CH_3} & \mathsf{CH_3} \end{bmatrix}_{n}$$