# TimeQuest Timing Analyzer Quick Start Tutorial

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-TMQSTANZR-1.1

Software Version:9.1Document Version:1.1Document Date:© December 2009

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and /or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### Chapter 1. About this Tutorial

### Chapter 2. Quick Start Tutorial

| System Requirements                                            |     |

|----------------------------------------------------------------|-----|

| Procedures                                                     |     |

| Step 1: Open and Setup Your Design in the Quartus II Software  |     |

| Step 2: Setup the TimeQuest Timing Analyzer                    |     |

| Step 3: Perform Initial Compilation                            |     |

| Step 4: Launch the TimeQuest Timing Analyzer                   |     |

| Step 5: Create a Post-Map Timing Netlist                       |     |

| Step 6: Specify Timing Requirements                            |     |

| Step 7: Update the Timing Netlist                              | 2–4 |

| Step 8: Save the Synopsys Design Constraints (SDC) File        |     |

| Step 9: Generate Timing Reports for the Initial Timing Netlist |     |

| Step 10: Save Constraints to an SDC File                       |     |

| Step 11. Perform Timing-Driven Compilation                     |     |

| Step 12. Verify Timing in the TimeQuest Timing Analyzer        |     |

| Conclusion                                                     |     |

|                                                                |     |

### **Chapter 3. Script Examples**

| Commands and Tcl Scripts |  | . 3- | -1 |

|--------------------------|--|------|----|

|--------------------------|--|------|----|

### **Additional Information**

| Revision History        | About-1 |

|-------------------------|---------|

| How to Contact Altera   | About-1 |

| Typographic Conventions | About-1 |

# **1. About this Tutorial**

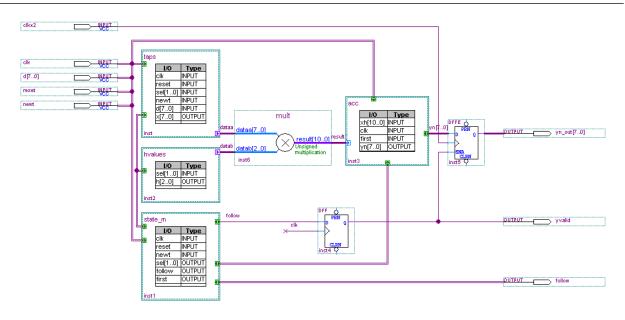

This tutorial describes the steps to constrain and perform static timing analysis with the TimeQuest Timing Analyzer. For this tutorial, use the **fir\_filter** design that ships with the Quartus<sup>®</sup> II software. Figure 1–1 shows the **fir\_filter** design schematic.

Figure 1–1. fir\_filter Design Schematic

# **System Requirements**

For this tutorial, use Stratix, Cyclone, MAX II, or newer device families (you can also use MAX 3000 and MAX 7000 device families) with the Quartus<sup>®</sup> II software beginning with version 6.0. APEX, FLEX, and Mercury device families are not supported.

# **Procedures**

Use the following steps to constrain and analyze a design with the TimeQuest Timing Analyzer. Each step includes the GUI procedure and the command-line equivalent.

### Step 1: Open and Setup Your Design in the Quartus II Software

In the Quartus II software, browse to and open the **fir\_filter** located in the <*qdesign folder*>/**fir\_filter**/ folder. Use the GUI or the command-line equivalent procedures in Table 2–1.

Table 2–1. Opening and Setting Up Your Design

| Quartus II Software GUI                                                                                                                                    | Command Line                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| On the File menu, click <b>Open Project</b> and browse to the project file < <i>Quartus II Installation</i><br>Folder>\qdesigns\fir_filter\fir_filter.qpf. | Type:<br>quartus_sh -s ↔<br>project_open fir_filter -revision \<br>filtref ↔ |

### Step 2: Setup the TimeQuest Timing Analyzer

By default, the Quartus II software uses the Classic Timing Analyzer as the timing analysis tool for designs targeting the Cyclone device family. Specify the TimeQuest Timing Analyzer as the timing analysis tool in the Quartus II software to use in the compilation flow for the **fir\_filter** project.

This step is not required for all projects. The newer FPGA families default to the TimeQuest Timing Analyzer.

Specify the TimeQuest Timing Analyzer as the timing analysis tool in the Quartus II software with the procedures in Table 2–2.

| Table 2–2. | Specifying the TimeQuest Timing Analyzer as Defau | ult |

|------------|---------------------------------------------------|-----|

|            |                                                   |     |

| Quartus II Software GUI                                                                     | Command Line                                     |

|---------------------------------------------------------------------------------------------|--------------------------------------------------|

| 1. On the Assignments menu, click <b>Settings</b> . The <b>Settings</b> dialog box appears. | Type:<br>set_global_assignment -name \           |

| 2. In the Category list, select Timing Analysis Settings                                    | USE_TIMEQUEST_TIMING_ANALYZER ON 🕶               |

| 3. Turn on Use TimeQuest Timing Analyzer during compilation.                                | To close the project, type: project_close exit ↔ |

| 4. Click <b>OK</b> .                                                                        |                                                  |

# Step 3: Perform Initial Compilation

Before applying timing constraints to the design, create an initial database with the procedures in Table 2–3. The initial database is generated from the post-map results of the design.

Table 2–3.

Performing Initial Compilation (Note 1)

| Quartus II Software GUI                                                                         | Command Line               |

|-------------------------------------------------------------------------------------------------|----------------------------|

| On the Processing menu, point to <b>Start</b> and click <b>Start Analysis &amp; Synthesis</b> . | Type:quartus_map filtref ↔ |

Note to Table 2–3:

(1) The quartus\_map is used to create a post-map database.

The Analysis & Synthesis step generates a post-map database.

You can also create a post-fit netlist for the initial database. However, creating a post-map is less time consuming and is sufficient for this tutorial example.

# Step 4: Launch the TimeQuest Timing Analyzer

Launch the TimeQuest Timing Analyzer to create and verify all timing constraints and exceptions with the procedures in Table 2–4. This command opens the TimeQuest shell.

Table 2-4. Launching the TimeQuest Timing Analyzer

| Quartus II Software GUI                                     | Command Line                                |

|-------------------------------------------------------------|---------------------------------------------|

| On the Tools menu, click <b>TimeQuest Timing Analyzer</b> . | Туре:                                       |

|                                                             | quartus_sta -s ↔                            |

|                                                             | project_open fir_filter -revision filtref 🕶 |

IP W

When you launch the TimeQuest Timing Analyzer directly from the Quartus II software, the current project is automatically opened.

If you use the GUI, select No when the following message appears:

"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?"

# Step 5: Create a Post-Map Timing Netlist

Before specifying the timing requirements, create a timing netlist. You can create a timing netlist from a post-map or post-fit database. In this step, create a timing netlist from the post-map database you created in "Step 3: Perform Initial Compilation" with the procedures in Table 2–5.

Table 2–5. Creating a Post-Map Timing Netlist

| TimeQuest Timing Analyzer GUI                                                                                           | TimeQuest Timing Analyzer Console      |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <ol> <li>On the Netlist menu, click Create Timing Netlist. The<br/>Create Timing Netlist dialog box appears.</li> </ol> | Type:create_timing_netlist -post_map 🕶 |

| 2. Under Input netlist, select Post-Map.                                                                                |                                        |

| 3. Click <b>OK</b> .                                                                                                    |                                        |

You cannot use the **Create Timing Netlist** command in the **Tasks** pane to create a post-map timing netlist. By default, the **Create Timing Netlist** requires a post-fit database.

# **Step 6: Specify Timing Requirements**

You must define two clocks in the **fir\_filter** design. Refer to Table 2–6 for a list of properties for each clock.

Table 2-6. Clocks in fir\_filter Design

| Clock Port Name | Requirement                     |

|-----------------|---------------------------------|

| clk             | 50 MHz with a 50/50 duty cycle  |

| clkx2           | 100 MHz with a 60/40 duty cycle |

Create the clocks in the **fir\_filter** design and assign the proper clock ports with the procedures in Table 2–7.

• For more information about constraints supported by the TimeQuest Timing Analyzer, refer to the *TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*.

Table 2–7. Creating Clocks and Assigning Clock Ports

| TimeQuest Timing Analyzer<br>GUI                                                                               | TimeQuest Timing Analyzer Console                                                                                         |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1. On the Constraints menu,<br>click <b>Create Clock</b> . The<br><b>Create Clock</b> dialog box<br>appears.   | Type:<br>#create the 50 MHz (20 ns) clock<br>create_clock -period 20 [get_ports clk]<br>#create the 100 MHz (10 ns) clock |

| 2. Specify the parameters in<br>Table 2–2 for the 50 MHz<br>clock. Repeat these step for<br>the 100 MHz clock. | create_clock -period 10 -waveform {0 6} [get_ports clkx2] ↔                                                               |

**For more information about creating clocks of different duty cycles, refer to the** *TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*.

After you complete the procedure shown in Table 2–7, the clock definition is complete.

# **Step 7: Update the Timing Netlist**

After you create timing constraints or exceptions, update the timing netlist to apply all timing requirements to the timing netlist (the new clk and clkx2 clock constraints) with the procedures in Table 2–8.

You must update the timing netlist whenever new timing constraints are applied.

#### Table 2-8. Updating the Timing Netlist

| TimeQuest Timing Analyzer GUI                                           | TimeQuest Timing Analyzer Console |

|-------------------------------------------------------------------------|-----------------------------------|

| In the <b>Tasks</b> pane, double-click the <b>Update Timing Netlist</b> | Type:update_timing_netlist ←      |

| command.                                                                |                                   |

# Step 8: Save the Synopsys Design Constraints (SDC) File

You have the option of creating an SDC file after specifying the clock constraints for the design and updating the timing netlist with the procedures in Table 2–9. Constraints that have been specified with the TimeQuest Timing Analyzer GUI or in the console are not automatically saved.

F

<sup>2</sup> If you inadvertently overwrite any of your constraints later in the design flow, use this initial SDC file to restore all of your constraints.

The initial SDC file can act as the "golden" SDC file that contains the original constraints and exceptions for the design.

#### Table 2-9. Saving the SDC File

| TimeQuest Timing Analyzer GUI                                                                                              | TimeQuest Timing Analyzer Console |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| <ol> <li>In the Tasks pane, double-click the Write SDC File<br/>command. The Write SDC File dialog box appears.</li> </ol> | Type:write_sdc filtref.sdc ←      |

| 2. Enter filtref.sdc in the <b>File Name</b> field.                                                                        |                                   |

The new **filtref.sdc** file contains the constraints and false path exceptions for the two clocks that you defined in "Step 6: Specify Timing Requirements".

The **Write SDC File** command can overwrite any existing SDC file. When this occurs, the new SDC file does not maintain order or comments. Therefore, Altera recommends saving a golden SDC file separately that you can manually edit with a text editor. This allows you to enter comments and organize the file to your own specifications.

# **Step 9: Generate Timing Reports for the Initial Timing Netlist**

After specifying timing constraints and updating the timing netlist, generate timing reports, which verify that all clocks are properly defined and applied to the correct nodes, for the two clocks you defined with the procedures in Table 2–10. The TimeQuest Timing Analyzer provides easy to use report generation commands that allow you to verify all timing requirements in the design.

Table 2–10. Report SDC Command

| TimeQuest Timing Analyzer GUI |                                                                       | TimeQuest Timing Analyzer Console | 1 |

|-------------------------------|-----------------------------------------------------------------------|-----------------------------------|---|

|                               | In the <b>Tasks</b> pane, double-click the <b>Report SDC</b> command. | Type: report_sdc 🕶                |   |

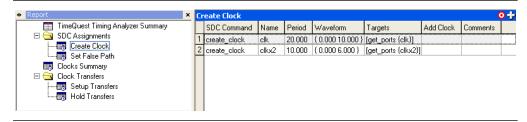

Figure 2–1 shows the Create Clock report that you generate when you click **Report SDC** in the **Tasks** pane.

Figure 2-1. Generating the SDC Assignments Report

| 2 |                     | × | reate Clock  | eate Clock |        |                  |                     |           |          |  |

|---|---------------------|---|--------------|------------|--------|------------------|---------------------|-----------|----------|--|

| k |                     |   | SDC Command  | Name       | Period | Waveform         | Targets             | Add Clock | Comments |  |

|   | E 🔄 SDC Assignments |   | create_clock | clk        | 20.000 | { 0.000 10.000 } | [get_ports {clk}]   |           |          |  |

|   | Create Clock        |   | create_clock | clkx2      | 10.000 | { 0.000 6.000 }  | [get_ports {clkx2}] |           |          |  |

|   |                     |   |              |            |        |                  |                     |           |          |  |

| • | Tasks               | × |              |            |        |                  |                     |           |          |  |

SDC Assignments reports all timing constraints and exceptions specified in the design. Two reports are generated: one for the clocks and one for the clock groups.

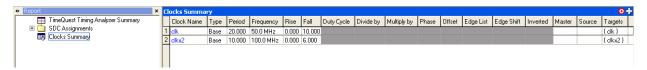

Generate a report that summarizes all clocks in the design with the procedures in Table 2–11.

Table 2–11. Generating the Report Clocks Report

| TimeQuest Timing Analyzer GUI                                            | TimeQuest Timing Analyzer Console |

|--------------------------------------------------------------------------|-----------------------------------|

| In the <b>Tasks</b> pane, double-click the <b>Report Clocks</b> command. | Type:report_clocks 🕶              |

Figure 2–2 shows the Clocks Summary report.

Figure 2–2. Clocks Summary Report

Use the **Report Clock Transfers** command to generate a report to verify that all clock-to-clock transfers are valid with the procedures in Table 2–12. This report contains all clock-to-clock transfers in the design.

#### Table 2–12. Generating the Report Clock Transfers

| TimeQuest Timing Analyzer GUI                                                     | TimeQuest Timing Analyzer Console |

|-----------------------------------------------------------------------------------|-----------------------------------|

| In the <b>Tasks</b> pane, double-click the <b>Report Clock Transfers</b> command. | Type:report_clock_transfers 🕈     |

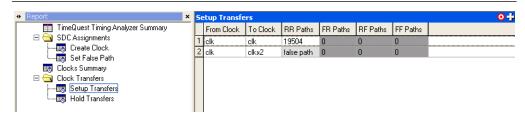

Figure 2–3 shows the Clock Transfers report.

#### Figure 2–3. Clock Transfers Report

| Report                                  | × | Se | tup Transfe | rs       |          |          |          |          | <b>⊙</b> + |

|-----------------------------------------|---|----|-------------|----------|----------|----------|----------|----------|------------|

| TimeQuest Timing Analyzer Summary       |   |    | From Clock  | To Clock | RR Paths | FR Paths | RF Paths | FF Paths |            |

| E C SDC Assignments                     | [ | 1  | clk         | clk      | 19504    | 0        | 0        | 0        |            |

| 📑 Clocks Summary<br>🗆 😋 Clock Transfers | [ | 2  | clk         | clkx2    | 16       | 0        | 0        | 0        |            |

|                                         |   |    |             |          |          |          |          |          |            |

| Hold Transfers                          |   |    |             |          |          |          |          |          |            |

|                                         |   |    |             |          |          |          |          |          |            |

The Clock Transfers report indicates that a clock-to-clock transfer exists between the clk source and the clkx2 destination. There are 16 instances where clk clocks the source node and where clkx2 clocks the destination node.

In the **fir\_filter** design, you do not have to analyze clock transfers from clk to clkx2 because they are false paths. Declare the paths from clk to clkx2 as false paths with the procedures in Table 2–13. When you complete this procedure, the TimeQuest Timing Analyzer indicates that the Clock Transfers report is outdated.

#### Table 2–13. Declaring False Paths

| TimeQuest Timing Analyzer GUI                                                                                                                                                                        | TimeQuest Timing Analyzer Console                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 1. In the Clock Transfers report, select <b>clk</b> in the <b>From Clock</b> column.                                                                                                                 | Type:<br>set_false_path -from [get_clocks clk] \ |

| 2. Right-click and select <b>Set False Paths Between Clock</b><br><b>Domains</b> . This command declares all paths from<br>registers clocked by clk to registers clocked by clkx2<br>as false paths. | -to [get_clocks clkx2] ↔                         |

Alternatively, use the set\_clock\_groups command to declare the paths between the two clock domains as false paths. For example, set\_clock\_groups -asynchronous -group [get\_clocks clk] -group [get\_clocks clkx2]. This command declares all paths from clk to clkx2 and from clkx2 to clk as false paths. This method is preferred.

Because you have added a new timing constraint, update the timing netlist with the procedure in Table 2–14.

#### Table 2–14. Updating the Timing Netlist

| TimeQuest Timing Analyzer GUI                                                    | TimeQuest Timing Analyzer Console |

|----------------------------------------------------------------------------------|-----------------------------------|

| In the <b>Tasks</b> pane, double-click the <b>Update Timing Netlist</b> command. | Type:update_timing_netlist ←      |

After you enter the set\_false\_path in the GUI, all generated report panels are labeled "Out of Date," indicating that the report panels do not contain results that reflects the current state of constraints or exceptions in the TimeQuest Timing Analyzer. To update the report panels, you must regenerate all of the reports.

At the command-line, re-enter the commands. In the GUI, right-click on any out-of-date report in the report panel list and select **Regenerate** or **Regenerate all**.

After you update the timing netlist, verify that the clock-to-clock transfer has been declared false with the procedures in Table 2–15.

Table 2–15. Verifying Using the Report SDC Command

| TimeQuest Timing Analyzer GUI               | TimeQuest Timing Analyzer Console |

|---------------------------------------------|-----------------------------------|

| In the Tasks pane, double-click Report SDC. | Type:report_sdc ←                 |

Figure 2-4 shows the new SDC Assignments report.

Figure 2-4. SDC Assignments Report

The report shown in Figure 2–4 indicates that the clock constraints and the false paths are correct.

Use the **Report Clocks** and **Report Clock Transfers** commands to verify that the two clocks have been removed from analysis. Figure 2–5 shows the Clock Transfers report.

Figure 2–5. Clock Transfers Report

The **RR Paths** column contains the comment "false path" to indicate that you have declared the clock domains as false paths.

# Step 10: Save Constraints to an SDC File

After you specify all clock constraints and false paths for the design, save the timing constraints and exceptions to an SDC file with the procedures in Table 2–16.

Table 2–16. Saving Constraints to an SDC File

| TimeQuest Timing Analyzer GUI                                                                                   | TimeQuest Timing Analyzer Console |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1. In the <b>Tasks</b> pane, double-click <b>Write SDC File</b> . The <b>Write SDC File</b> dialog box appears. | Type:write_sdc filtref.sdc 🛩      |

| 2. In the <b>File name</b> field, enter filtref.sdc.                                                            |                                   |

This procedure overwrites the previously created **filtref.sdc** file. If you overwrite an SDC with the **Write SDC File** command, your custom formatting and comments are removed in the new SDC file.

The **filtref.sdc** file contains the two clock constraints and the false path exceptions.

# Step 11. Perform Timing-Driven Compilation

After saving the constraints to the SDC file, run a full compilation on the design to optimize fitting to meet the constraints. However, before you start a full compilation, add the SDC to your project with the procedures in Table 2–17.

Table 2–17. Adding the SDC File to Your Project

| TimeQuest Timing Analyzer GUI                                                                                                    | TimeQuest Timing Analyzer Console               |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 1. On the Project menu, click <b>Add/Remove Files In Project</b> .<br>The <b>Add/Remove Files In Project</b> dialog box appears. | Type:<br>set global assignment -name SDC FILE \ |

| 2. Browse to and select the .sdc.                                                                                                | filtref.sdc 🕂                                   |

| 3. Click <b>OK</b> .                                                                                                             |                                                 |

After you add the SDC to your project, run a full compilation on the design with the procedures in Table 2–18.

#### Table 2–18. Running a Full Compilation

| TimeQuest Timing Analyzer GUI                    | TimeQuest Timing Analyzer Console     |

|--------------------------------------------------|---------------------------------------|

| On the Processing menu, click Start Compilation. | Type:quartus_shflow compile filtref 🕶 |

After compilation is complete, the TimeQuest Timing Analyzer generates a summary report of the clock setup and clock hold checks performed in the Compilation Report.

### Step 12. Verify Timing in the TimeQuest Timing Analyzer

To obtain detailed timing analysis data on specific paths, view timing analysis results in the TimeQuest Timing Analyzer.

After a full place-and-route is performed, launch the TimeQuest Timing Analyzer as described in "Step 4: Launch the TimeQuest Timing Analyzer".

Generate a post-fit timing netlist, read the SDC file, and update the timing netlist to generate reports about the latest compilation with the procedures in Table 2–19.

| TimeQuest Timing Analyzer GUI                                                                                    | TimeQuest Timing Analyzer Console                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In the <b>Tasks</b> pane, double-click the desired reporting command. For example, <b>Report All Summaries</b> . | Type:<br>create_timing_netlist<br>read_sdc filref.sdc<br>update_timing_netlist<br>report_clocks<br>create_timing_summary -setup<br>create_timing_summary -hold<br>create_timing_summary -recovery<br>create_timing_summary -removal<br>report_min_pulse_width -nworst 10 |

Table 2–19. Generating Reports About the Latest Compilation

When you double-click one of the reporting commands, the **Create Timing Netlist**, **Read SDC**, and **Update Timing Netlist** commands are sequentially executed in the **Tasks** pane, automatically setting up the timing netlist.

The clock setup check ensures that each register-to-register transfer does not violate the timing constraints you specified in the SDC. Verify that no violations have occurred by generating a clock setup summary check for all clocks in the design with the procedures in Table 2–20.

**Table 2–20.** Generating a Clock Setup Summary Check

| TimeQuest Timing Analyzer GUI                         | TimeQuest Timing Analyzer Console   |

|-------------------------------------------------------|-------------------------------------|

| In the Tasks pane, double-click Report Setup Summary. | Type:create_timing_summary -setup 🕶 |

Figure 2–6 shows the Summary (Setup) report.

#### Figure 2-6. Summary (Setup) Report

The clkx2 clock does not appear in the Summary (Setup) report because all clock paths between clk and clkx2 have been declared as false paths. In addition, the **fir\_filter** design does not contain any register-to-register paths where a destination register path is clocked by clkx2.

The **Slack** column in the Summary (Setup) report indicates that clk fails to meet the constraint by 11.588 ns. The **End Point TNS** column is the total of all total negative slack (TNS) for the specified clock domain. Use this value to gauge the amount of failing paths in the specified clock domain.

For the **fir\_filter** design, the **Slack** column equals the End Point TNS, indicating that there is only one failing path for the clk clock domain.

After you generate the Summary (Setup) report, generate a clock hold check summary for the design with the procedures in Table 2–21.

Table 2–21. Generating the Summary (Hold) Report

| TimeQuest Timing Analyzer GUI                        | TimeQuest Timing Analyzer Console  |

|------------------------------------------------------|------------------------------------|

| In the Tasks pane, double-click Report Hold Summary. | Type:create_timing_summary -hold 🕶 |

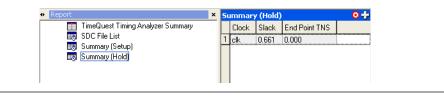

Figure 2–7 shows the Summary (Hold) report.

#### Figure 2-7. Summary (Hold) Report

The Summary (Hold) report indicates that the clk clock node meets the timing constraints by 0.661 ns.

Specify all timing constraints and exceptions prior to performing a full compilation with the procedures in Table 2–22. This ensures that the Fitter optimizes for the critical paths in the design.

You can use the **Report Unconstrained Paths** command to verify that you have constrained all paths in the **fir\_filter** design.

| Table 2-22. | Specifying | Timing | Constraints | and Exceptions |

|-------------|------------|--------|-------------|----------------|

|-------------|------------|--------|-------------|----------------|

| TimeQuest Timing Analyzer GUI                               | TimeQuest Timing Analyzer Console |

|-------------------------------------------------------------|-----------------------------------|

| In the Tasks pane, double-click Report Unconstrained Paths. | Type:report_ucp 🕶                 |

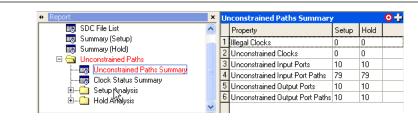

Figure 2–8 shows the Unconstrained Paths Summary report.

| Figure 2–8. | Unconstrained | Paths | Summary Report |

|-------------|---------------|-------|----------------|

|-------------|---------------|-------|----------------|

The Unconstrained Paths Summary report indicates that there are numerous unconstrained paths and details the types of paths.

To fully constrain this design, utilize the full set of SDC constraints provided by the TimeQuest Timing Analyzer.

To fully constrain the **fir\_filter** design, constrain all input and output ports. Use the **Set Input Delay** and **Set Output Delay** dialog boxes, or the set\_input\_delay and set\_output\_delay constraints to specify the input and output delay values.

Because additional constraints are applied to the design, create an additional SDC that contains only the input and output constraints with the text editor (for example, **inout\_delay.sdc**). Add the input and output delay assignments shown in Table 2–23 to the new SDC created in "Step 10: Save Constraints to an SDC File".

Table 2–23. Input and Output Delay Assignments

|    | The TimeQuest Timing Analyzer GUI                                                                                                                                                                                     | The TimeQuest Timing Analyzer Console                                                                                 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1. | On the Constraints menu, click <b>Set Input Delay</b> . The <b>Set Input Delay</b> dialog box appears.                                                                                                                | To constrain the input ports, type:<br>set input_delay -clock clk 2 \                                                 |

| 2. | Enter the following:<br><b>Clock name</b> : clk<br><b>Delay value</b> : 2<br><b>Targets</b> : [get_ports {d[0] d[1] d[2] d[3] \<br>d[4] d[5] d[6] d[7] newt reset}]                                                   | <pre>[get_ports {d* newt reset}]<br/>To constrain the output ports, type:<br/>set_output_delay -clock clk 1.5 \</pre> |

| 3. | On the Constraints menu, click <b>Set Output Delay</b> . The <b>Set Output Delay</b> dialog box appears.                                                                                                              | [get_ports {yn_out* yvalid follow}] ←                                                                                 |

| 4. | Enter the following:<br><b>Clock name</b> : clk<br><b>Delay value</b> : 1.5<br><b>Targets</b> : [get_ports {yn_out[0] yn_out[1] \<br>yn_out[2] yn_out[3] yn_out[4] yn_out[5] \<br>yn_out[6] yn_out[7] yvalid follow}] |                                                                                                                       |

All ports should be constrained in the design after you read the SDC containing the input and output delay constraints.

Remember to update the timing netlist after reading the new constraints. For more information, refer to "Step 7: Update the Timing Netlist".

To verify all ports are constrained in the design, regenerate the Unconstrained Paths Summary report (Figure 2–9).

Figure 2–9. Regenerated Unconstrained Paths Summary Report

| <ul> <li>Report</li> </ul>                                   | × | Ur | nconstrained Paths Summary      |       |      | 0+ |

|--------------------------------------------------------------|---|----|---------------------------------|-------|------|----|

| TimeQuest Timing Analyzer Summary                            |   | Γ  | Property                        | Setup | Hold |    |

| SDC File List                                                |   | 1  | Illegal Clocks                  | 0     | 0    |    |

|                                                              |   | 2  | Unconstrained Clocks            | 0     | 0    |    |

| Summary (Hold)<br>Unconstrained Paths<br>Tock Status Summary |   | 3  | Unconstrained Input Ports       | 0     | 0    |    |

|                                                              |   | 4  | Unconstrained Input Port Paths  | 0     | 0    |    |

|                                                              |   | 5  | Unconstrained Output Ports      | 0     | 0    |    |

| Egi clock status summary                                     |   | 6  | Unconstrained Output Port Paths | 0     | 0    |    |

Generate specific timing check reports for clocks or nodes in the design with the procedures in Table 2–24. The procedures in Table 2–24 generate a report where clk clocks the destination register to the design destination register bus acc:inst3|result and reports the top 10 worst paths.

| TimeQuest Timing Analyzer GUI                                                                                           | TimeQuest Timing Analyzer Console          |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 1. In the <b>Tasks</b> pane, double-click <b>Report Timing</b> . The <b>Report Timing</b> dialog box appears.           | Type:<br>report_timing -to_clock clk -to / |

| 2. Enter the following:<br><b>To Clock</b> : clk<br><b>To</b> : acc:inst3 result*<br><b>Report number of paths</b> : 10 | acc:inst3 result* -setup -npaths 10 🕶      |

| 3. Leave the other fields with the default setting.                                                                     |                                            |

Figure 2–10 shows the Report Timing report.

|        | Slack From N                 | ode              | <u> </u> | To Node       |          | Launch Clock | Latch | . Ck | ock Relationship            | Clock Skew       | Data Delay    | ~   |

|--------|------------------------------|------------------|----------|---------------|----------|--------------|-------|------|-----------------------------|------------------|---------------|-----|

| 1      |                              | n:inst1 filter.t |          | acc:inst3 res | adif[11] | clk          | clk   |      | 20.000                      | 0.000            | 8.383         |     |

| 2      |                              | n:inst1 filter.t |          | acc:inst3lres |          | clk          | clk   |      | 20.000                      | 0.000            | 8.382         |     |

| 3      |                              | n:inst1 filter.t |          | acc:inst3 res | sult[11] | clk          | clk   |      | 20.000                      | 0.000            | 8.371         | _   |

| 4      | 11.600 state_r               | ninst1 filter.t  | ap3      | acc:inst3 res | sult[11] | clk          | clk   |      | 20.000                      | 0.000            | 8.371         |     |

| 5      | 11.601 state_r               | n:inst1 filter.t | арЗ      | acc:inst3 res | sult[11] | clk          | clk   |      | 20.000                      | 0.000            | 8.370         |     |

| 6      | 11.601 state_r               | n:inst1 filter.t | ap3      | acc:inst3 res | sult[11] | clk          | clk   |      | 20.000                      | 0.000            | 8.370         | ~   |

| <      |                              |                  |          |               |          | )            |       |      |                             |                  |               | >   |

| _      |                              |                  |          |               |          |              |       | _    |                             |                  |               |     |

| th     | #1: Setup slack              | is 11.588        |          |               |          |              |       | P    | ath #1: Setup sla           | ack is 11.588    |               |     |

| Pal    | h Summary   Stati            | stics Data       | Path     | Waveform      |          |              |       |      | Path Summary S              | tatistics Data F | Path Waveform | 1   |

| _      | ta Arrival Path              |                  |          | IT GTOIDINI   |          |              |       |      |                             |                  |               |     |

| 7a     | Total                        | Incr             | BE       | Туре          | Fand     | ut Locatio   |       |      |                             |                  |               |     |

| 1      | 0.000                        | 0.000            | Inr      | Type          | Fan      |              |       |      |                             |                  |               |     |

| 2      | 0.000                        | 2.277            | _        |               | _        |              | -81   |      |                             |                  | -i F          | - ^ |

| 2<br>3 | 2.277                        | 2.277            | В        | _             |          |              | - 1   |      | Launch Clock <sup>Lau</sup> | unch             |               |     |

| 3<br>4 | □ 10.660                     | 8.383            | n        | _             |          |              | -     |      |                             |                  |               |     |

| 4<br>5 | 2.450                        | 0.303            |          | uTco          | 2        | LC_X24       |       |      | Setup Relation:             | ship 2           | 0.0 ns        |     |

| 5      | 2.450                        | 0.000            | BB       | CELL          | 9        | LC_X24       |       |      |                             |                  |               |     |

| 7      | 2.450                        | 0.412            | BB       | IC            | 1        | LC_X24       |       |      | Latch Clock                 |                  | Latch         | -   |

| /<br>B | 2.950                        | 0.412            | BB       | CELL          | 12       | LC_X24       |       |      | Laten Clock                 |                  |               |     |

| 。<br>く | j 2.300                      |                  | Inn      | LELL          | 12       |              |       |      |                             |                  |               | +   |

|        |                              |                  |          |               |          |              |       |      | Data Arrival                |                  | Å             |     |

| 1.00   | ta Required Pat              | 1                |          |               |          |              |       |      |                             | 2.277 ns         |               | T   |

| Ъ      | Total                        | Incr             | RF       | Туре          | Fano     | ut Locatio   | n     |      | Clock Delay                 | 2.2// fis        |               |     |

| Л      | 20.000                       | 20.000           |          |               |          |              |       |      |                             |                  |               |     |

|        |                              | 2.277            |          |               |          |              |       |      | Data Delay                  | 8.383            | ns            |     |

| 1<br>2 | □ 22.277                     |                  |          |               |          |              |       |      | -                           |                  |               |     |

| 1      | □ 22.277<br>22.277<br>22.248 | 2.277            | R        |               |          | LC_X28       |       |      |                             |                  |               |     |

Use the **Report Top Failing Paths** command in the **Tasks** pane to generate a report that details the top failing paths in the design.

# Conclusion

As you create new constraints or exceptions, rerun the Quartus II Fitter to optimize the design based on your new constraints or exceptions. Multiple iterations on the design may be necessary to achieve the desired results.

# **Commands and Tcl Scripts**

This section includes commands and accompanying Tcl scripts to execute the entire flow from the command line. Use this method to completely execute the entire flow.

Enter the command in Example 3–1 at a command prompt to source the scripts.

#### Example 3–1. Source the Scripts

```

quartus_sh -t timequest_setup.tcl +

quartus_sta -t main_postmap.tcl +

quartus_sh -t fit_sdc_setup.tcl +

quartus_sta -t main_postfit.tcl +

```

Example 3–2 shows the content of the **timequest\_setup.tcl** script. Use this script to specify the TimeQuest Timing Analyzer as the default timing analysis tool.

<sup>></sup> The Classic Timing Analyzer is the default timing analyzer in the Quartus II software.

**Example 3–2.** The timegest\_setup.tcl Script

```

#open the filtref project

project_open filtref

#set the TimeQuest analyzer as the default timing analyzer

set_global_assignment -name USE_TIMEQUEST_TIMING_ANALYZER ON

#close the project

project_close

#

```

Example 3–3 shows the content of the **main\_postmap.tcl** script. Use this script to create post-map data, set up the timing netlist, read in **golden.sdc**, and generate initial reports for the design.

```

Example 3–3. The main_postmap.tcl Script

```

```

#file main_postmap.tcl

#Include the flow package to create a post-map netlist

package require ::quartus::flow +

#open the project in TimeQuest

project_open filtref ←

#create a post-map database

execute_module -tool map ←

#create the timing netlist based on the post-map results

create_timing_netlist -post_map +

#read in the constraints from the golden SDC file

read_sdc golden.sdc ←

#update the timing netlist with the new constraints

update_timing_netlist ←

#generated a clock report

report_clocks 🕶

#generated a clock-to-clock report

report_clock_transfers +

#delete our post-map timing netlist

delete_timing_netlist 🕶

#close the TimeQuest project

project_close ←

```

Example 3–4 shows the content of the **fit\_sdc\_setup.tcl** script. Use this script to add the **golden.sdc** file to the **filtref** design. This allows the Quartus II Fitter to optimize the design according to the constraints you specify.

**Example 3–4.** The fit\_sdc\_setup.tcl Script

```

#open the filtref project

project_open filtref

#add the filtref.sdc file to our Quartus II project

set_global_assignment -name SDC_FILE golden.sdc

#close the project

project_close

```

Example 3–5 shows the content of the **main\_postfit.tcl** script. Use this script to create a post-fit database, set up the timing netlist, read in the **golden.sdc** and **io\_cons.sdc** files, and generate reports for the design.

```

Example 3–5. The main_postfit.tcl Script

```

```

#Include the flow package to create a post-fit netlist

package require ::quartus::flow +

#open the project in TimeQuest

project_open filtref ←

#create a post-fit database

execute_module -tool fit 🕶

#create a post-fit timing netlist

create_timing_netlist +

#read the golden SDC file and the I/O SDC file

read_sdc golden.sdc 🕂

read_sdc io_cons.sdc 🕶

#update the post-fit timing netlist with constraints

update_timing_netlist ←

#report unconstrained paths

report_clocks 🕶

create_timing_summary -setup 🛩

create_timing_summary -hold -

create_timing_summary -recovery 🕶

create_timing_summary -removal 🕶

report_ucp 🖊

#delete our post-map timing netlist

delete_timing_netlist +

#close the TimeQuest project

project_close 🕶

```

Example 3–6 and Example 3–7 show the contents of the **golden.sdc** and **io\_cons.sdc** files, respectively.

Example 3–6. The golden.sdc File

```

#create the 50 MHz 50/50 clock

create_clock -period 20 [get_ports clk]

#create the 100 MHz 60/40 clock

create_clock -period 10 -waveform {0 6} [get_ports clkx2]

#cut the clk and clkx2 domains

set_clock_groups -group [get_clocks clk] -group [get_clocks clkx2] #

```

#### Example 3–7. The io\_cons.sdc File

```

#set the input delays for the design

set_input_delay -clock clk 1.0 [get_ports {d[*] reset newt}]

#set the output delays for the design

set_output_delay -clock clk 1.5 [get_ports {yn_out[0] yn_out[1] \

yn_out[2] yn_out[3] yn_out[4] yn_out[5] yn_out[6] yn_out[7] yvalid follow}]

```

3–4

# **Revision History**

The following table shows the revision history for this user guide.

| Date          | Version | Changes Made                                                                   |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------|--|--|--|

| December 2009 | 1.1     | <ul> <li>Updated figures in Chapter 2.</li> </ul>                              |  |  |  |

|               |         | <ul> <li>Updated chapter for Quartus II software 9.1 functionality.</li> </ul> |  |  |  |

| May 2006      | 1.0     | Initial Release                                                                |  |  |  |

# **How to Contact Altera**

For the most up-to-date information about Altera® products, see the following table.

| Contact (Note 1)                | Contact<br>Method | Address                  |

|---------------------------------|-------------------|--------------------------|

| Technical support               | Website           | www.altera.com/support   |

| Technical training              | Website           | www.altera.com/training  |

|                                 | Email             | custrain@altera.com      |

| Non-technical support (General) | Email             | nacomp@altera.com        |

| (Software Licensing)            | Email             | authorization@altera.com |

Note:

(1) You can also contact your local Altera sales office or sales representative.

# **Typographic Conventions**

The following table shows the typographic conventions that this document uses.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                      |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bold Type with Initial Capital Let-<br>ters | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                   |  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, file names, file name extensions, and software utility names are shown in bold type. Examples: <b>f<sub>MAX</sub></b> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |  |

| Italic Type with Initial Capital Letters    | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                       |  |

| Italic type                                 | Internal timing parameters and variables are shown in italic type.                                                                                                                                                                                                           |  |

|                                             | Examples: $t_{PIA}$ , $n + 1$ .                                                                                                                                                                                                                                              |  |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file i="" name<="">&gt;, <i><project i="" name<="">&gt;.<b>pof</b> file.</project></i></file></i>                                                                              |  |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples:<br>Delete key, the Options menu.                                                                                                                                                              |  |

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                             |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                        |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDE-SIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is impor-<br>tant, such as the steps listed in a procedure.                                                                                                                                                                                    |

|                                     | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                     |

| $\checkmark$                        | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                      |

| IP                                  | The hand points to information that requires special attention.                                                                                                                                                                                                                                                          |

| CAUTION                             | A caution calls attention to a condition or possible situation that can damage or destroy the product or the user's work.                                                                                                                                                                                                |

| WARNING                             | A warning calls attention to a condition or possible situation that can cause injury to the user.                                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                               |

|                                     | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                           |