## Responsive Processor for Parallel/Distributed Real-Time Control

Nobuyuki Yamasaki Keio University / Electrotechnical Laboratory E-mail: yamasaki@{ics.keio.ac.jp, etl.go.jp} http://www.ny.ics.keio.ac.jp

## Abstract

Responsive Processor for Parallel/Distributed Real-Time Control integrates:

Processing Core (SPARC)

♦ <u>Responsive Link</u>(Real-Time Communication)

Computer I/O (SDRAM I/F, DMAC, PCI, USB, PIO, SIO, Timers, Counters, …)

Control I/O (ADC, DAC, PWM Generators, Pulse Counters, ...)

#### System-on-a-chip

for Parallel/Distributed Real-Time Control

Combination with some processors

Realization of various kinds of control systems

## Components of Responsive Processor

**Responsive Processor**

<u>Responsive Link</u> (Real-time communication)

## Control I/O

(ADC, DAC, PWM Generators, Counters, ...) Motor Sensor

. . .

Processing Core (SPARC)

## Responsive Processor

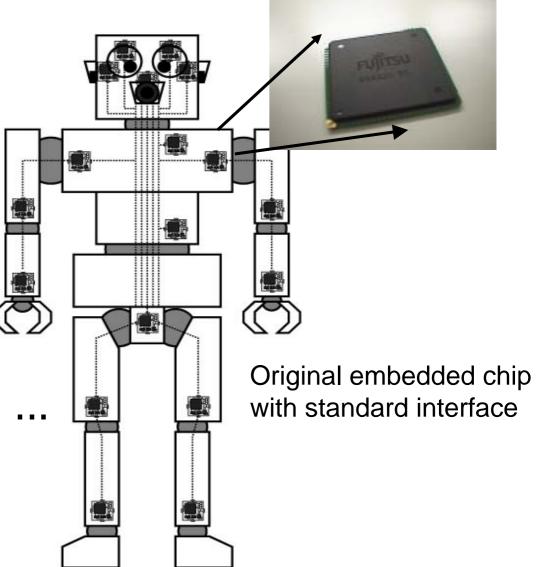

## **Applications**

### Functionally distributed control

- Robots

- Office Automation

- Factory Automation

- Home Automation

- Intelligent Buildings

- Amusement Systems, ...

## Event Processing for Embedded Control

- Embedded control systems must respond to external inputs (sensors, user inputs, etc.) and operate according to the inputs.

- External inputs(interrupts) may occur frequently and continuously.

- Short response time

- Short processing time

♦Control of devices(motors, sensors, etc.) → Time limitation.

## Responsive System

**Responsive** = Reactive + Real-time

Reactive: A characteristic in which a reflexive action occurs according to an external input

Real-Time: A characteristic in which the exactness of the system depends on not only the result but also the time it took to achieve the result Design Policy of Responsive System

Basic Strategy by Hardware

Shorter response time to external events

Shorter processing time for the events

### **Basic Tactics by Hardware**

Immediate transmission of events

Parallel processing with respect to different kinds of events

Concurrent processing in regard to the same kind of events

## How to Realize a Responsive System

- Generation of an event from a sensor

- Immediate transmission to the proper module to process the event

- Generation of several events simultaneously or continuously

- Different kinds of several events

- Parallel processing by function-specific modules

- Reduction of both processing and response time

- The same kind of several events

- Concurrent processing

- Reduction of response time

## Function-specific Parallel Computer

Each module controls different I/O functions

Coarse grain function-specific tasks

Each module can be treated as an agent

MIMD

Parallel computer architecture for embedded control systems

# Current Real-Time Communication IEEE-1394(FireWire, iLink, DV) USB

Soft Real-Time Communication : Isochronous transfer

Error correction is not supported in case of the isochronous mode.

Central Control : Low robustness

Maximum connection number is limited:

(IEEE-1394 : 63, USB : 127 )

Topology is fixed. (Tree structure)

## Trade-off on Real-Time Communication

Soft real-time : Guarantee of band width

Maximization of Throughput

Hard real-time : Guarantee of latency

Minimization of Latency

| PACKET SIZE | LARGE | SMALL |

|-------------|-------|-------|

| Throughput  | High  | Low   |

| Latency     | Long  | Short |

## **Responsive Link** for Real-Time Communication

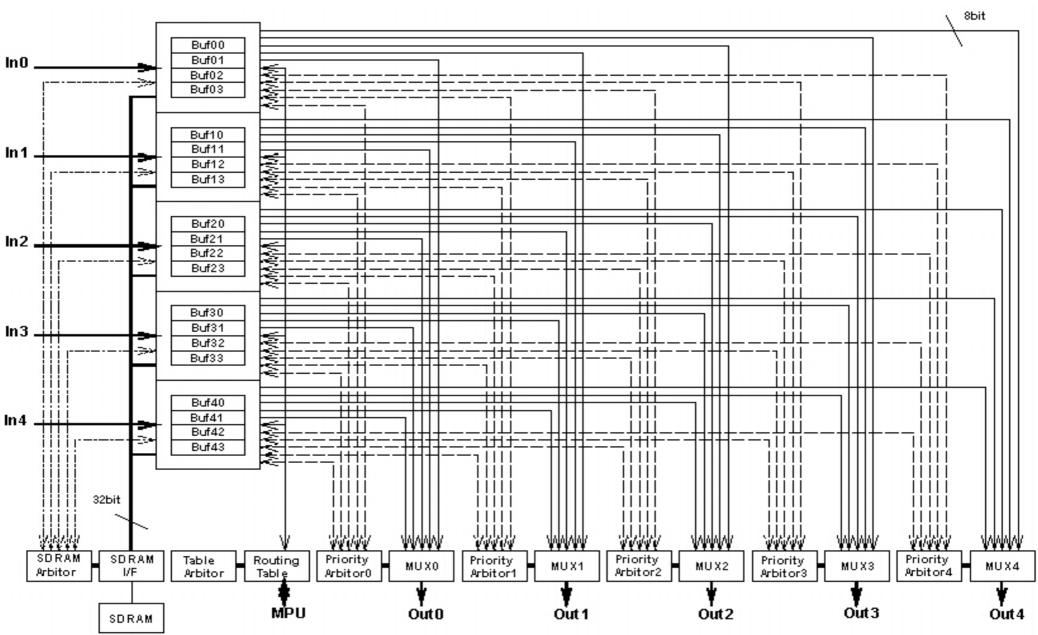

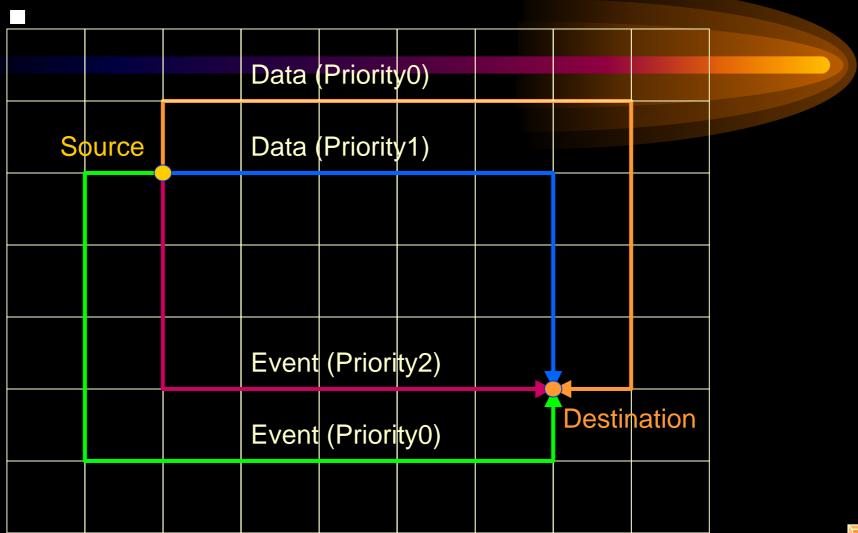

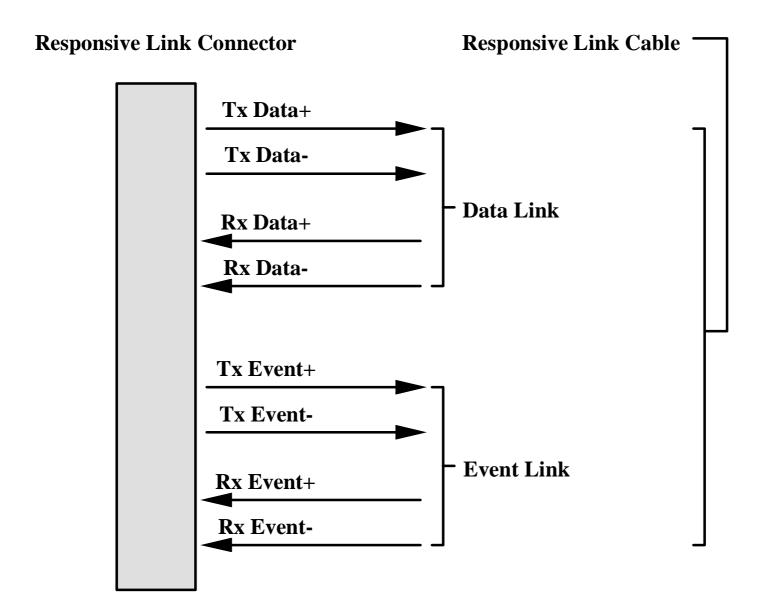

- Split transmission of data and events

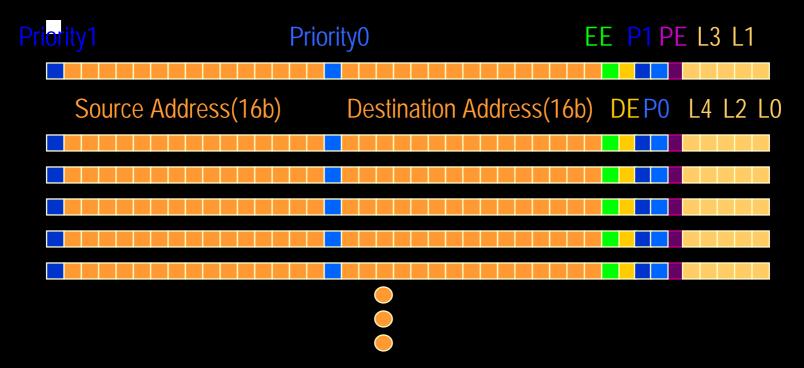

- Fixed packet size: 64B data, 16B event

- Full-duplex and differential I/F

- Hardware routing

- Independent routing of data and events

- <u>Cut-through switch with overtaking function</u> (The packet with higher priority can overtake other packets at each node.)

- <u>Priority replacement</u> (Packet priority can be replaced with new priority at each node.)

- When the network address is same but priority is different, the different route can be reset to realize exclusive lines or detours.

- ♦ <u>Automatic error correction</u>

- Flexible link speed (12.5 to 100M bps)

Point-to-point link configurable for any topology

Required Functions

## Split Lines for Event and Data

## Data Link

Soft real-time communication for bulky data

- Multimedia data transmission (images, voice, etc.)

Relatively large fixed packet size (64B)

- Relatively large fixed packet size (64B)

- Total throughput is important

## Event Link

Hard real-time communication for control

Inter-processor interrupt and synchronization

Relatively small fixed packet size (16B)

Low latency for relatively few packets is important

#### Data PacketFormat (64B)

## Packet Format

|          |      |         |          |          |         |         | _   |

|----------|------|---------|----------|----------|---------|---------|-----|

| Source A | ddr. |         | De etina | tion Add | r.      |         | 5   |

|          |      |         |          |          |         |         |     |

|          |      |         |          |          |         |         |     |

|          |      |         |          |          |         | L       |     |

|          |      |         |          |          |         |         |     |

|          |      |         |          |          |         |         |     |

|          |      |         |          |          |         |         |     |

|          |      | Paylo   | ad       |          |         |         | 1   |

|          |      |         |          |          |         |         | 1   |

|          |      |         |          |          |         |         | [   |

|          |      |         |          | _        |         | 1       | 1   |

|          |      |         |          | _        |         | (       |     |

|          |      |         |          | _        |         |         |     |

|          |      |         |          | _        |         |         |     |

|          |      |         |          | _        |         |         |     |

|          | 0    | ontrols | . Statu∎ |          |         |         |     |

|          |      |         |          |          |         |         |     |

|          |      |         |          |          |         | 1       |     |

| lbyte    |      |         |          |          |         | Ý       |     |

|          | ,    |         | -        | Contro   | l& Sta  | tus For | ms  |

|          |      |         |          |          |         |         | _   |

| bit      | 0    | 0       | Full     | -        |         | Data Le |     |

|          | 1    | Dirty)  | Dirty1   | Dirt;2   | Dirt;S  | Dirty4  |     |

|          | 2    | Dirt;S  | Dirt;9   | Dirty10  | Dirty11 | Dirty12 | Dir |

#### Event Packet Format (16B)

| Source A | ddr.       | De atination | ı Adıdır. |

|----------|------------|--------------|-----------|

|          | Interrupt  | le vel       |           |

|          | Interrup t | vector       |           |

|          | Control 8  | statu.       |           |

#### at (32bits)

| 162 | 0 | 0      | Full   |         |         | Data Le | ngti     |                 |         |

|-----|---|--------|--------|---------|---------|---------|----------|-----------------|---------|

|     | 1 | Dirt;0 | Dirty1 | Dirt;2  | Dirt;S  | Dirty4  | Dirt;5   | Dirtys          | Dirt;7  |

|     | 2 | Dirt;S | Dirt;9 | Dirty10 | Dirty11 | Dirty12 | Dirty13  | Dirty14         | Dirty15 |

|     | 3 | Start  | Brid   | Int.    | Fetel   | Correct | Serial N | Jmper( <b>c</b> | λnt)    |

#### Frame Format (14bits)

|       | Data bit | Redundancy bits |

|-------|----------|-----------------|

| 1 1 1 |          | fiedundahcybit∎ |

### Cut-through Switch with Overtaking Function

## Control of Overtaking Buffers

## Routing Table

It is possible to set different routes in case of the same network address when the priorities are different. (Default route is priority 0.)

It is possible to replace a packet priority with a new priority at each node.

## Routing according to Priority

## Low Level Communication

- Forward Error Correction(FEC)

- Cyclic hamming code

- Sbit data + 4bit redundant code

- Bit stuffing

- NRZI(Non Return to Zero Inverted)

- DPLL(Digital Phase-Lock-Loop)

- Synchronous frame (Setup Pattern)

- Flexible link speed (100Mbaud, 50Mbaud, 25Mbaud, 12.5Mbaud)

Responsive Link I/F

**Required Functions**

### A questionnaire survey by using robotics and control mailing lists

Required functions, developing environments, operating systems, etc.

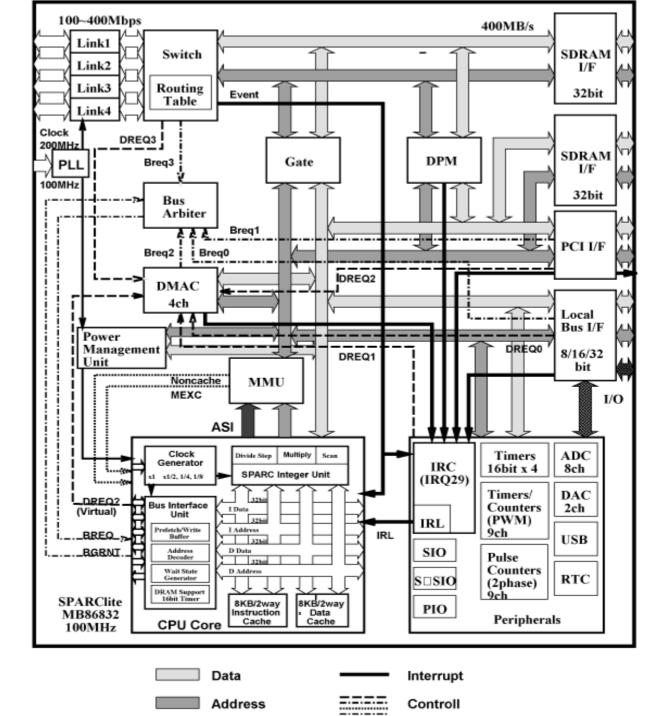

## Functions of Responsive Processor

- Processing Core (SPARC 100MHz)

- Power Management Unit (100, 80, 60, 40, 20 [MHz], Sleep)

- MMU (64way)

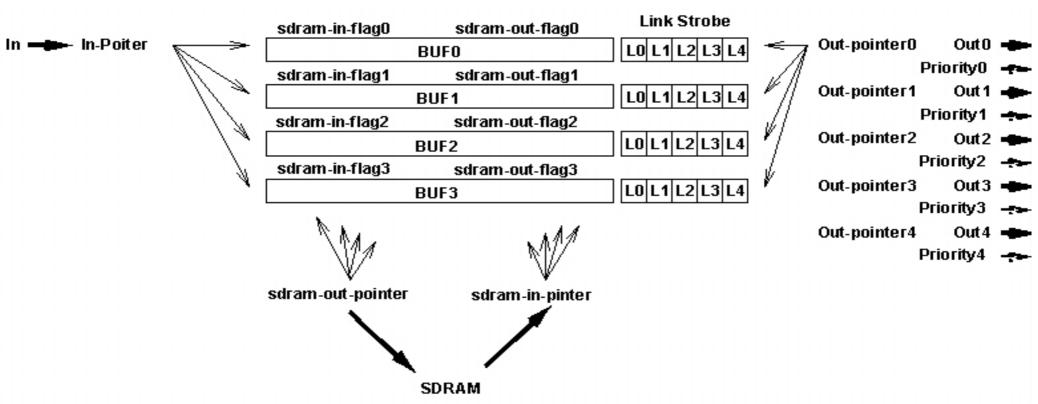

- <u>Responsive Links</u> (4 links, 200, 100, 50, 25 [MHz])

- DMAC (4channels, Bus swapping, Bus sizing)

- SDRAM I/F (2channels, 100MHz)

- PCI I/F (Master/Target)

- USB I/F (Function, Hub)

- PWM Generators (50MHz, 9channels)

- Pulse Counters (24bit, 9channels)

- Timers/Counters (16bit, 4channels)

- Real-Time Clock

- A/D Converters (10bit, 8channels)

- D/A Converters (8bit, 2channels)

- Interrupt Controllers (43channels)

- SIO (RS-232C, 2channels)

- ◆ PIO (16bit), ...

Diagram of Responsive Processor

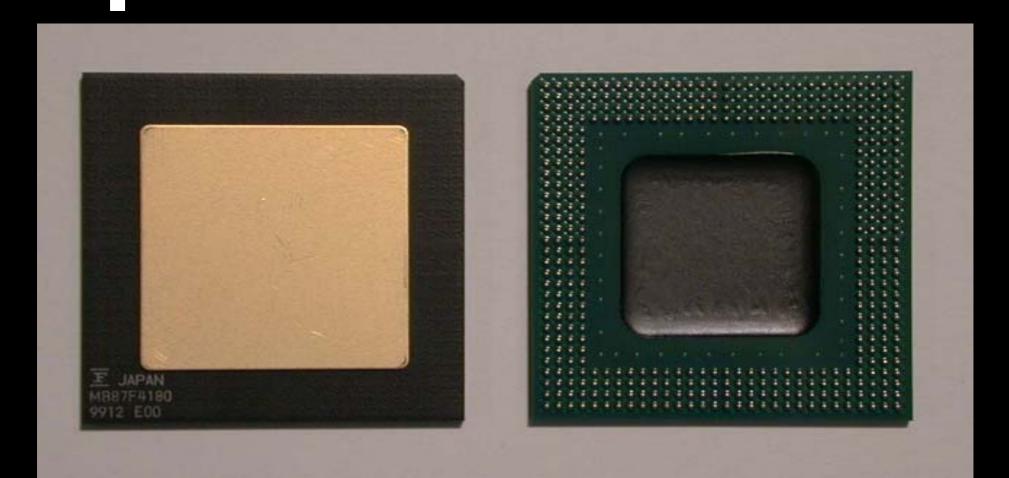

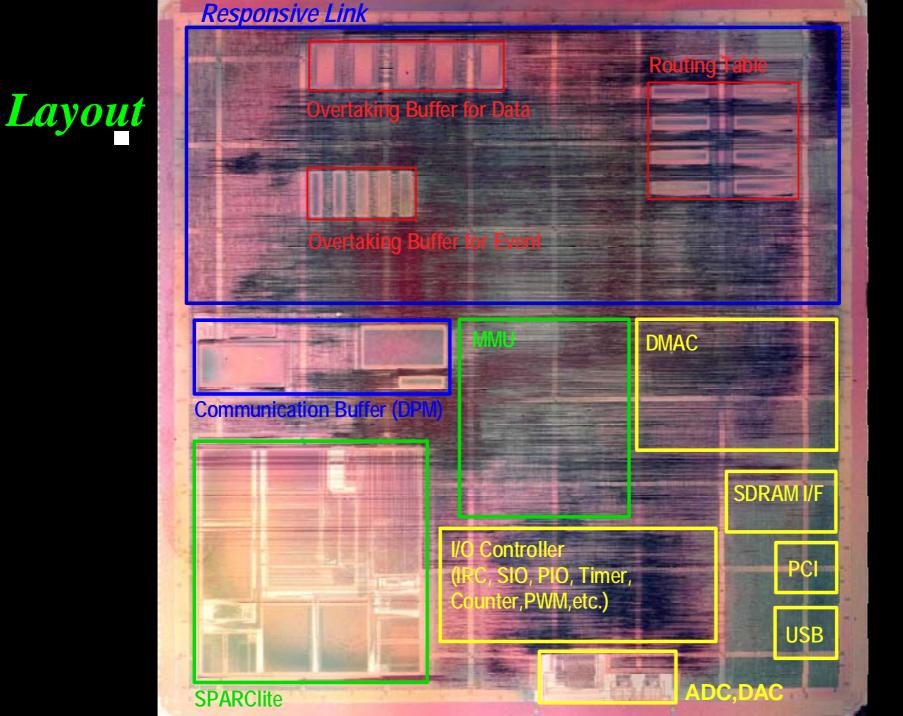

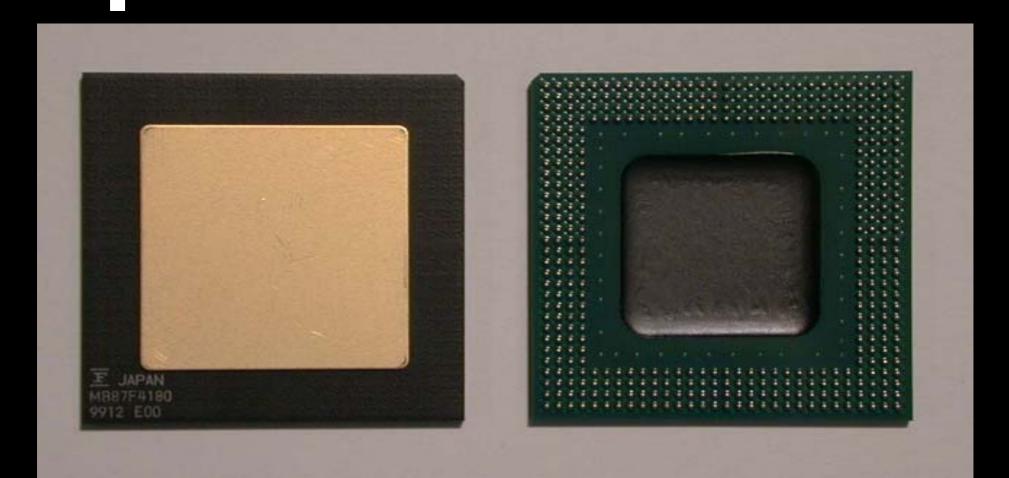

## Hardware Design Rules

Process: 0.35 µm, CMOS, 4 layered metal

Usable gates: 2,378 k gates

Die size: 14.5 mm x 14.5mm = 210mm2

Package: 416pin BGA (40mm x 40mm)

Voltage: 3.3V

Max. power: 2W

## Responsive Processor

## **Performance** (Speed v.s. Power)

| Performance of MPU |     |     |     |     |     |       |  |  |

|--------------------|-----|-----|-----|-----|-----|-------|--|--|

| Clock(MHz)         | 100 | 80  | 60  | 40  | 20  | Sleep |  |  |

| Speed(MIPS)        | 121 | 97  | 73  | 48  | 24  | 0     |  |  |

| Power(W)           | 1.0 | 8.0 | 0.6 | 0.4 | 0.2 | 0.01  |  |  |

### Performance of Responsive Link

| Clock (MHz)              | 200 | 100 | 50   | 25   |

|--------------------------|-----|-----|------|------|

| Max. Speed (Mbaud)       | 100 | 50  | 25   | 12.5 |

| Speed of Data (Mbps)     | 67  | 33  | 17   | 8    |

| Latency of Event( µ sec) | 3.1 | 6.2 | 12.5 | 25   |

| Power (W)                | 0.2 | 0.1 | 0.05 | 0.02 |

Latency of Event (Worst) = 1 ( $\mu$  sec) + 2 ( $\mu$  sec/hop) x n (hop)

PCI card (PCI half size)

CardBus card (PCMCIA size)

Embedded board (Credit card size)

## PCI Card

## **Developing Environment**

- Cross development on Windows PC via PCI, USB, or RS-232C

- GNU tools (gcc, as, Id, make, etc.)

- Source level debugging by GDB

- Host OS : Linux, FreeBSD, Solaris, Windows

gdb sparolite

<u>G</u>db <u>E</u>dit <u>W</u>indow <u>D</u>ebug <u>H</u>elp

- 8 ×

WinGDR 🗃 日 Source 1 Reg1 × qØ 00000000 1FFFFFFF 0000000A mon.c **q**4 00000A00 02080000 02000000 volatile unsigned long \*ptr; 00 03010000 FFFFF000 **FFFF6000** int i, j; 04 FFFFFFF FFFFFFF 0207F8A8 char buf[BUFSIZ]; 10 00000010 020165BC 02016500 char \*token; 14 02016B00 0201B000 0201A989 10 FFFFFFF 0201A848 02019400 ASI4put(0x03010000, 0xfffff000); **i**4 FFFFFFF FFFFFFF 0207FD30 00000000 OFOOOFCO 00000004 while( 1 ) { 02010200 02010264 00000000 DC printf( "MON>" ); dda1 00000000 00000000 00000000 if( !fgets( buf, BUFSIZ, stdin ) dcr 00000000 00000003 break; PC 0x20102a0 <main+44>: 020102A0 edit( buf ); ngr OF GOOF CO if( !(token = strtok( buf, " \t\n usage( "mon" ); - 🗆 × Command Log1 continue: (qdb) (ddb) break main type = \*token; Note: breakpoint 1 also set at pc 0x2010280. if( !(token = strtok( NULL. Breakpoint 2 at 0x2010280: file mon.c, line 40. usage( "mon" ); (qdb) j main continue; Continuing at 0x2010280. ۰. Breakpoint 1, main () at mon.c:40 printf( "MON>" ); 40 ASI4put(0x03010000, 0xfffff000); if( !fqets( buf, BUFSIZ, st (gdb) step break; while( 1 ) { 42 edit( buf ); (gdb) next if( !(token = strtok( buf, printf( "MON>" ); 43 usage( "mon" ); (gdb) 40#90 12

Operating Systems

Commercial

VxWorks

pSOSystem

µ iTRON

OS-9

Research

♦ RT-Mach

♦ µ PULSER

♦ RT-Linux

## Standardization

## ISO/IEC JTC1 SC25 WG4 Responsive Link SG

**Responsive Link SG:** Matsushita Electric Industrial Co., Mitsubishi Electric Corporation, Fujitsu Limited, Hitachi, STARC, Electrotechnical Laboratory, Keio University, Kyusyu University

JTC1 SC25 WG4: RWCP, NTT, Oki Electric Industry, Yokogawa Electric Corporation, Mitsubishi Electric, Fujitsu Limited, Matsushita Communication Industrial Co., Toshiba Corporation, Hitachi Limited, SONY, NEC, Electrotechnical Laboratory, Nihon Unisys, Victor data systems, Japanese Standards Association, Sumitomo Electric industry Conclusions

Real-Time Control integrates:

*Responsive Link*Processing Core (SPARC)

Computer I/Os

Control I/Os

Easy processor connection Flexible configuration