Frédéric Lang Francesco Flammini (Eds.)

# Formal Methods for Industrial Critical Systems

19th International Conference, FMICS 2014 Florence, Italy, September 11–12, 2014 Proceedings

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany

# Formal Methods for Industrial Critical Systems

19th International Conference, FMICS 2014 Florence, Italy, September 11-12, 2014 Proceedings

Volume Editors

Frédéric Lang Inria, 38330 Montbonnot, France E-mail: frederic.lang@inria.fr

Francesco Flammini Ansaldo STS, 80147 Naples, Italy E-mail: francesco.flammini@ansaldo-sts.com

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-319-10701-1 e-ISBN 978-3-319-10702-8 DOI 10.1007/978-3-319-10702-8 Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014946586

#### LNCS Sublibrary: SL 2 - Programming and Software Engineering

#### © Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in ist current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

This volume contains the papers presented at FMICS 2014, the 19th International Workshop on Formal Methods for Industrial Critical Systems, which took place on September 11–12, 2014, in Florence, Italy.

The FMICS 2014 workshop took place during the one-week scientific event FLORENCE 2014, which also hosted the 12th International Conference on Formal Modeling and Analysis of Timed Systems (FORMATS 2014), the 11th International Conference on Quantitative Evaluation of SysTems (QEST 2014), the 33rd International Conference on Computer Safety, Reliability and Security (SAFECOMP 2014), and the 10th European Workshop on Performance Engineering (EPEW 2014).

The aim of the FMICS workshop series is to provide a forum for researchers who are interested in the development and application of formal methods in industry. In particular, FMICS brings together scientists and engineers who are active in the area of formal methods and interested in exchanging their experiences in the industrial usage of these methods. The FMICS workshop series also strives to promote research and development for the improvement of formal methods and tools for industrial applications.

The topics of interest include, but are not limited to:

- Design, specification, code generation, and testing based on formal methods

- Methods, techniques, and tools to support automated analysis, certification, debugging, learning, optimization, and transformation of complex, distributed, dependable, real-time systems, and embedded systems

- Verification and validation methods that address shortcomings of existing methods with respect to their industrial applicability, e.g., scalability and usability issues

- Tools for the development of formal design descriptions

- Case studies and experience reports on industrial applications of formal methods, focusing on lessons learned or identification of new research directions

- Impact of the adoption of formal methods on the development process and associated costs

- Application of formal methods in standardization and industrial forums

This year we received 26 submissions. Papers had to pass a rigorous review process in which each paper received three reports. The international Program Committee of FMICS 2014 decided to select 13 papers for presentation during the workshop and inclusion in these proceedings. The contributions focused on the following main topics:

- Cyber-physical systems

#### VI Preface

- Computer networks

- Railway control systems

- Verification methods

- Hardware and software testing

The workshop program was therefore organized in sessions according to these topics.

The workshop also featured invited talks by Pietro Marmo (Ansaldo STS, Italy), and by David Parker (University of Birmingham, UK).

Following a tradition established over the past few years, the European Association for Software Science and Technology (EASST) offered an award to the best FMICS paper. This year, the reviewers selected two contributions ex aequo:

- "Assertion-Based Monitoring in Practice Checking Correctness of an Automotive DSI3 Sensor Interface," by Thang Nguyen and Dejan Nickovic

- "Improving Static Analyses of C Programs with Conditional Predicates," by Sandrine Blazy, David Bühler and Boris Yakobowski

We would like to thank the FLORENCE 2014 general chair Enrico Vicario (University of Florence) for taking care of all the local arrangements in Florence and the FMICS 2014 local organization chair Alessandro Fantechi (University of Florence) for liaising between FMICS and FLORENCE 2014 organizations. We also thank the FMICS 2014 publicity chair Wendelin Serwe (Inria and LIG, France) and the webmasters Marco Paolieri and Simone Mattolini (University of Florence) for contributing to the international visibility of the workshop. Finally, we thank the ERCIM FMICS working group coordinator Radu Mateescu (Inria Grenoble and LIG) for his help, EasyChair for supporting the review process, Springer for the publication, all Program Committee members and external reviewers for their substantial reviews and discussions, all authors for their submissions, and all attendees of the workshop. Thanks to all for your contribution to the success of FMICS 2014.

September 2014

Frédéric Lang Francesco Flammini

# Organization

## **Program Committee**

Maria Alpuente Alvaro Arenas Jiri Barnat Cinzia Bernardeschi Simona Bernardi Jean-Paul Blanguart Eckard Böde Rocco De Nicola Michael Dierkes Susanna Donatelli Cindv Eisner Alessandro Fantechi Jérôme Feret Francesco Flammini Wan Fokkink Andrew Gacek Stefania Gnesi Matthias Güdemann Keijo Heljanko Jan Jurjens Frederic Lang Tiziana Margaria Pedro Merino Benjamin Monate Gethin Norman David Parker **Charles** Pecheur Ralf Pinger Wendelin Serwe Hans Svensson Jaco van de Pol Valeria Vittorini Angela Vozella

Universitat Politècnica de Valencia, Spain IE University, Spain Masarvk University, Czech Republic University of Pisa, Italy Centro Universitario de la Defensa, AGM, Zaragoza, Spain Astrium Satellites, France Offis. Germany IMT Lucca, Italy Rockwell Collins, France University of Turin, Italy IBM Research - Haifa, Israel Università di Firenze, Italy CNRS and ENS and Inria, France Ansaldo. Italy Vrije Universiteit Amsterdam and CWI, The Netherlands Rockwell Collins, USA ISTI-CNR, Italy Systerel, France Aalto University, Finland TU Dortmund and Fraunhofer ISST Inria and LIG, France University of Potsdam, Germany University of Málaga, Spain TrustInSoft, France University of Glasgow, UK University of Birmingham, UK Université catholique de Louvain, Belgium Siemens AG, Germany Inria and LIG, France Quviq, Sweden University of Twente, The Netherlands University of Naples Federico II, Italy CIRA, Italy

# Additional Reviewers

Ballis, Demis Bauch, Petr Ferrari, Alessio Houtmann, Clément Isberner, Malte James, Phillip Kuismin, Tuomas Margheri, Andrea Romero, Daniel Tinacci, Marco Abstracts of Invited Talks

# 20 Years Past and (Hopefully) 20 Years to Come: My Experience in Ansaldo STS with Formal Methods and Railways

Pietro Marmo<sup>\*</sup> Ansaldo STS, Italy Mailsa

Abstract. On next November, 20 years will have passed since the first time I used a "formal method" for a real job in my company. Actually it was a Petri Net model used to evaluate the safety of a two out of three system. Since then, I have experimented a whole set of formal methods (formal languages, model-checking, Theorem Proving, stochastic nets, etc.), either for ad hoc studies with universities and research centers, or for European research projects. Many of them aimed at providing a fully automatic environment with the power of mathematics and the ease of use of a toy but few have found real applications with valuable results. All those years have brought many improvements and more and more utilizations of formal methods are now possible in industry. In this talk we present the challenges that are required to formal methods in railways, where they have won and where they have lost in the past, together with a glance at what will be required and with what possible results in the next twenty years (or so).

Keywords: Formal Method, Petri Net, Railway, AnsaldoSTS.

\* Contact Author

# Quantitative Verification: Formal Guarantees for Timeliness, Reliability and Performance

David Parker

School of Computer Science, University of Birmingham, UK

**Abstract.** Quantitative verification is a technique for analysing quantitative aspects of a system's design, such as timing, probabilistic behaviour or resource usage. It provides a means of automatically deriving formal guarantees on a wide range of system properties, such as timeliness, reliability or performance, for example, "the airbag will always deploy within 20 milliseconds after a crash" or "the probability of both sensors failing simultaneously is less than 0.001". Recent years have seen significant advances in the underlying theory, verification techniques and tool support in this area, and these methods have been applied to an impressive array of systems, from wireless networking protocols to robotic systems to cardiac pacemakers.

This talk will give an overview of the state-of-the-art in quantitative verification, focusing in particular on probabilistic model checking, a quantitative verification technique for the analysis of systems with stochastic behaviour. The talk will explain the key ideas behind the approach, highlight some of the application areas where it has been successful, with particular emphasis on case studies with industrial involvement, describe a few of the current research directions in the area and discuss some of the challenges which remain.

# Table of Contents

| Formal Verification of Steady-State Errors in Unity-Feedback Control                                                                                                                 |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Systems                                                                                                                                                                              | 1   |

| Muhammad Ahmad and Osman Hasan                                                                                                                                                       |     |

| Assertion-Based Monitoring in Practice – Checking Correctness of an<br>Automotive Sensor Interface<br>Thang Nguyen and Dejan Ničković                                                | 16  |

| Analysis of Real-Time Properties of a Digital Hydraulic Power<br>Management System<br>Pontus Boström, Petr Alexeev, Mikko Heikkilä, Mikko Huova,<br>Marina Waldén, and Matti Linjama | 33  |

| Formal Analysis of a Fault-Tolerant Routing Algorithm for a<br>Network-on-Chip<br>Zhen Zhang, Wendelin Serwe, Jian Wu, Tomohiro Yoneda,<br>Hao Zheng, and Chris Myers                | 48  |

| Formal Specification and Verification of TCP Extended with the<br>Window Scale Option<br>Lars Lockefeer, David M. Williams, and Wan J. Fokkink                                       | 63  |

| Learning Fragments of the TCP Network Protocol<br>Paul Fiterău-Broștean, Ramon Janssen, and Frits Vaandrager                                                                         | 78  |

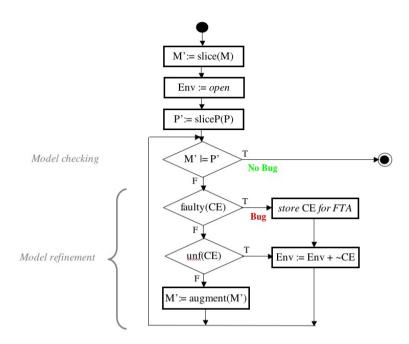

| On the Validation of an Interlocking System by Model-Checking<br>Andrea Bonacchi and Alessandro Fantechi                                                                             | 94  |

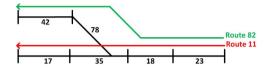

| Deadlock Avoidance in Train Scheduling: A Model Checking<br>Approach<br>Franco Mazzanti, Giorgio Oronzo Spagnolo,<br>Simone Della Longa, and Alessio Ferrari                         | 109 |

| An Open Alternative for SMT-Based Verification of SCADE Models<br>Henning Basold, Henning Günther, Michaela Huhn, and<br>Stefan Milius                                               | 124 |

| Improving Static Analyses of C Programs with Conditional<br>Predicates                                                                                                               | 140 |

| σαπατιπό σπασή, σαυτά σαπιότ, απά συτις τακουσωρκί                                                                                                                                   |     |

| Detecting Consistencies and Inconsistencies of Pattern-Based  |     |

|---------------------------------------------------------------|-----|

| Functional Requirements                                       | 155 |

| Christian Ellen, Sven Sieverding, and Hardi Hungar            |     |

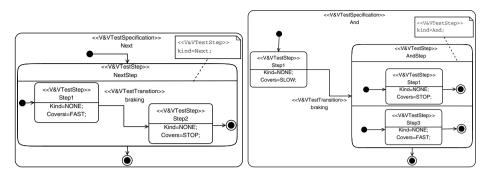

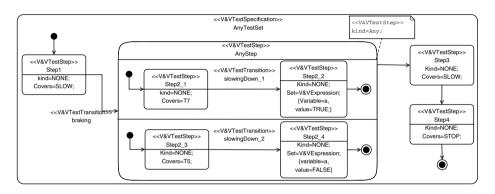

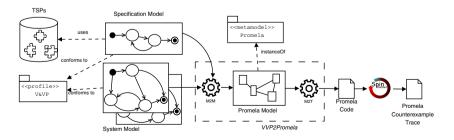

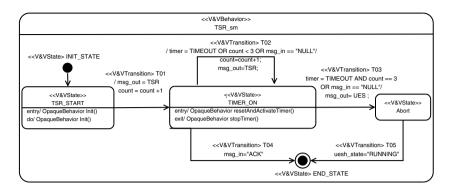

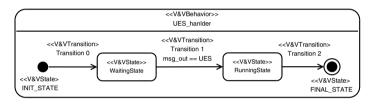

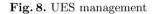

| Test Specification Patterns for Automatic Generation of Test  |     |

| Sequences                                                     | 170 |

| Ugo Gentile, Stefano Marrone, Gianluca Mele,                  |     |

| Roberto Nardone, and Adriano Peron                            |     |

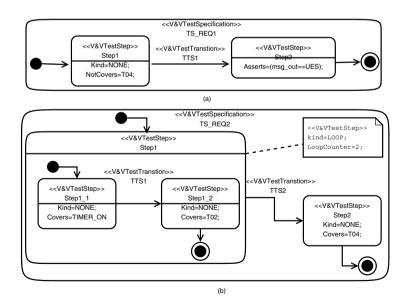

| Randomised Testing of a Microprocessor Model Using SMT-Solver |     |

| State Generation                                              | 185 |

| Brian Campbell and Ian Stark                                  |     |

|                                                               |     |

| Author Index                                                  | 201 |

# Formal Verification of Steady-State Errors in Unity-Feedback Control Systems

Muhammad Ahmad and Osman Hasan

School of Electrical Engineering and Computer Science (SEECS), National University of Sciences and Technology (NUST), Islamabad, Pakistan {muhammad.ahmad,osman.hasan}@seecs.nust.edu.pk

Abstract. The meticulousness of steady-state error analysis of unityfeedback control systems has always been of vital significance as even a trifling glitch in this analysis may result in grievous penalties. To ensure a rigorous steady-state error analysis, this paper presents the formal verification of a generic relationship that is applicable to all kinds of inputs and types of unity-feedback control systems. This formalization builds upon the multivariate calculus theories of HOL-Light and our prior work on developing formal models of feedback control systems. To illustrate the usefulness of this result, the paper presents the formal steady-state error analysis of a Pulse Width Modulation (PWM) pushpull DC-DC converter, which is an extensively used component in various power-electronics and aerospace applications.

## 1 Introduction

Control systems [18] form an integral part of all automated systems used in a wide range of safety-critical applications, including industrial automation, surgical robots, automobiles and aerospace systems. These control systems work along with the given systems (plants) and are designed in such a way that they ensure the desired behavior of their corresponding systems while adhering to the stability constraints and allowable error margins.

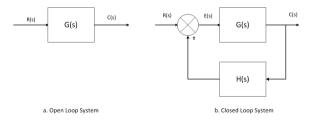

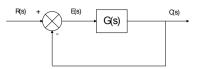

Control systems can be configured in an open or a closed loop topology [18]. In open-loop systems, the controller generates the control signals based on a reference or input signal R(s), as shown in Fig. 1.a. A disadvantage of this kind of configuration is that the controller has no information about the output of the plant (with open-loop transfer function G(s)) and thus cannot cater for unexpected disturbances. To overcome this limitation, control systems are often configured in a feedback or closed loop pattern where the output of the plant C(s) is measured and compared with a reference or an input signal R(s), as shown in Fig. 1.b. This error signal E(s) is then used for decision making in the controller to compensate for disturbances. A unity-feedback is a frequently used closed-loop system where the output of the system is compared with the reference input signal as is, i.e., without any gain or loss in the feedback path.

F. Lang and F. Flammini (Eds.): FMICS 2014, LNCS 8718, pp. 1-15, 2014.

<sup>©</sup> Springer International Publishing Switzerland 2014

The quality of the control system is judged based on its steady-state response [19], i.e., the response of the system when a large number of iterations in the closed-loop have taken place and the steady-state conditions have been attained. Steady-state error gives a parametric measure for the controllability of system and how well the system will respond to certain disturbances.

The steady-state analysis of unity-feedback control systems is performed in the Laplace domain because this choice allows us to model the main system in terms of the transfer functions of its sub-systems, as a block diagram. The overall transfer function of the plant G(s) is then expressed as follows by manipulating the transfer functions of its subsystems using a set of predefined rules[18]:

$$G(s) = \frac{1}{s^b} \frac{Y(s)}{Z(s)} \tag{1}$$

where the integer variable  $b: 0, 1, 2 \cdots$  categorizes the system type or the number of integrators in the forward path[18], and Y(s) and Z(s) represent the zeros and poles of G(s) apart from  $\frac{1}{s^b}$ . Now, the net transfer function for unity-feedback error model is mathematically expressed as[18]:

$$E(s) = \frac{R(s)}{1 + G(s)} \tag{2}$$

where R(s) models the input to our system, which in the case of steady-state error analysis is traditionally taken to be as the *unit step*  $(\frac{1}{s})$ , ramp  $(\frac{1}{s^2})$  and *parabola*  $(\frac{1}{s^3})$  functions. The steady-state error is measured at a very large time, i.e., when the time t tends to infinity. Thus, it can be defined in the Laplace domain by applying the Final Value Theorem to the error model:

$$e_{\infty} = \lim_{s \to 0} sE(s) \tag{3}$$

Traditional methods, like paper-and-pencil proof methods and computer simulations and numerical methods, cannot guarantee the accuracy of the abovementioned steady-state error analysis. The paper-and-pencil based analysis methods are error prone due to the human involvement. Moreover, it is quite often the case that many key assumptions of the results obtained of sub-system using

Fig. 1. Control System Configurations

paper-and-pencil proof methods are not documented, which may lead to to erroneous systems. Computer simulations and numerical methods, such as MathWorks Simulink [17], cannot guarantee accurate results while dealing with feedbackcontrol systems mainly due to their inherent non-exhaustive nature coupled with the imprecision of computer arithmetics. The mathematical models of control systems can also be analyzed in computer algebra systems (CAS), such as Mathematica [15]. CAS are very efficient for computing mathematical solutions symbolically, but are also not completely reliable due to the presence of unverified huge symbolic manipulation algorithms.

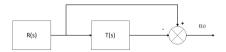

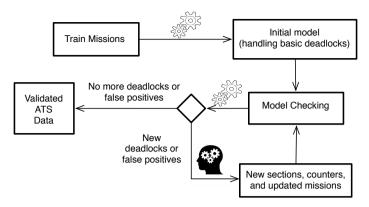

In order to overcome the above-mentioned limitations, the usage of formal methods in the safety-critical domain of control system analysis is increasingly being investigated [20,3]. However due to the continuous nature of the steadystate error analysis, automated theorem provers and model checking tools cannot ascertain absolute precision of analysis. Higher-order logic theorems provers have shown some promising results and a detailed review of the literature will be presented in the next section. One of the most interesting contributions, related to the formal steady-state analysis of control systems, is the higher-order-logic formalization of the basic building blocks[12], like forward transfer functions, summing junctions, feedback loops and pickoff points, of control systems using the multivariate analysis theories available in the HOL-Light theorem prover. These foundations can be built upon to formally specify a wide range of control systems in higher-order logic and reason about their steady-state errors within the sound core of a theorem prover. The process involves the verification of the error function for the given system based on its structure and the behavior its sub-blocks. This is followed by the verification of the limit of the error function of the given system, according to Equation (3), using the multivariate analysis libraries of HOL-Light. The approach was illustrated by verifying the steadystate error of a solar tracking control system. However, the reasoning process about the steady-state error model with closed loop transfer function T(s), shown in Fig. 2, is very cumbersome, the reason being the extensive user interaction requirement in verifying the limiting behavior, expressed in Equation (3), for the net expression for the error model of the given system. Moreover, this reasoning process has to be repeated all over again if the steady-state for a different type of input (unit step, ramp or parabola) is required for the same system, which is a very common occurrence in steady-state error analysis.

The main scope of this paper is to overcome the above mentioned issues. We build upon the formalization of the control system blocks of [12] to formalize the error model for the unity-feedback control systems. Moreover, we formally

Fig. 2. Steady-State Error Model

verify a generic expression for the steady-state error of unity-feedback control systems using the multivariate analysis theories of HOL-Light. The unique feature of this expression is that it can be used to reason about the steady-state error of any system type and input. Moreover, it facilitates reusability when reasoning about the state-state error of the same system while considering different inputs. The quest for minimizing the user interaction in the higher-order-logic theorem-proving based analysis for steady-state errors led us to develop this useful relationship, which to the best of our knowledge has not been reported in the control systems literature before. In order to illustrate the utilization and practical effectiveness of our formalization for verifying real-world control systems, we use it to conduct the steady-state error analysis of the Pulse Width Modulation (PWM) push-pull DC-DC converters[8], which is a widely used component in power electronics and many safety-critical aerospace applications. In order to evaluate the usefulness of our work for control system engineers, we engaged a domain expert; trained her with basic theorem proving abilities in a couple of weeks and assigned her the task to use our formalization for analyzing the PWM push-pull DC-DC converter and her experiences are also shared in this paper.

### 2 Related Work

ClawZ [4] allows us to translate models of control systems developed in MathWorks Simulink into Z language specifications, which are then verified by proving the equivalence of the controller implementation using Ada in ProofProver. Another similar approach is presented in [1] in which the author translates the discretetime Simulink model to Circus notations, which combines Z language and refinement calculus and then compares a parallel Ada implementation. An interesting methodology adopted in [7] calls for using the Timed Interval Calculus (TIC) library to capture the behavior of Simulink blocks, which could be verified in a theorem prover. A similar approach was adapted by Mahony, and modeling and analysis of feedback control systems was introduced using the DOVE environment [16]. Model checking has also been successfully used to analyze dynamic systems by abstracting the behavior of the system to a state-space model [22]. Herencia-Zapana [13] proposed to formally analyze control software properties by first expressing the stability proofs as C code annotations and then translating them to PVS proof obligations and automatically verifying them. All these pioneering frameworks are based on automatic formal verification tools and thus require some sort of abstraction mechanism to model the exact behavior of real-world control systems and their environments, which are always continuous in nature.

In order to formally model and analyze continuous models of control systems, Boulton et al. provided some reasoning support for verifying frequency response of continuous-time control systems using Hoare logic using the HOL98 theorem prover [6]. The main idea is to reason about the gain and phase relationships of a control system using the gain and phase relationships of its subsystems in the block diagram. This framework does not provide generic functions to model arbitrary block diagrams for control systems and also lacks reasoning support for complex number analysis principles, such as limits and summation, which are essential to reason about many control system design related parameters, such as steady-state errors and stability. In order to overcome these shortcomings, Boulton et al [5] proposed to use automated symbolic methods to replace the classical graphical charts, such as Nichole and Bode plots along with their formal models. Based on this principle, the authors developed a prototype tool using Maple and the PVS system. Maple is used to compute the verification conditions for the given control system and PVS is used to discharge these conditions using theorem proving principles. Due to the usage of Maple, the accuracy of the analysis is again somewhat compromised as has been mentioned above.

The foremost foundation of analyzing the steady-state error of control systems is the formalization of complex number analysis theories. The multivariate calculus theories of HOL-Light theorem prover [11] fulfill this requirement. These theories have been recently used to formalize the basic building blocks of control systems [12] and the Laplace theory [21], which are the most relevant contributions to our work. We build upon and enhance the results reported in [12] to analyze steady-state errors of unity-feedback control systems and facilitate the formal reasoning process by verifying a generic expression for steady-state error in this paper. The recent formalization of Laplace theory[21] opens up many interesting research directions in the context of our work since now we can link our formalization to the time-domain as well.

### 3 Preliminaries

In this section, we give a brief introduction to the multivariate analysis theories in the HOL-Light theorem prover and the block diagram formalization of [12]. The intent is to provide some preliminaries to make the paper self contained and thus facilitate its understanding for a wider audience, including both formal methods and control communities.

#### 3.1 Multivariate Calculus Theories in HOL-Light

A *n*-dimensional vector is represented as a  $\mathbb{R}^n$  column matrix of real numbers in HOL-Light. All of the vector operations are then handled as matrix manipulations. This way, complex numbers can be represented by the data-type  $\mathbb{R}^2$ , i.e, a column matrix having two elements [9]. In this formalization of complex numbers, the first real number represents the real part and the second real number represents the imaginary part of the given complex number[10]. The main advantage of this choice is that all the topological and analytic formalization developed for vectors is inherited by the complex numbers.

Definition 1: Complex Number ⊢ ∀ x y. complex (x,y) = vector [x; y]

The following mappings allow us to obtain the real and imaginary components of a complex number:

**Definition 2:** Real and Imaginary Components of a Complex Number  $\vdash \forall z$ . Re z = z\$1

$\vdash \forall z. \text{ Im } z = z\$2$

Here the notation z n represents the  $n^{th}$  component of a vector z. A real number a can be converted to an equivalent complex number as follows:

**Definition 3:** Cx $\vdash \forall z. Cx(a) = complex(a, \&0)$

The normalization of a complex number is also a widely used phenomena and has been formalized in HOL-Light [10] as follows:

**Definition 4:** Normalization of a Complex Number  $\vdash \forall z$ . norm z = sqrt (Re z pow 2 + Im z pow 2)

where sqrt represents the HOL-Light square root function for real numbers.

The concept of limit of a function is used in our formalization to model the steady-state error and is formalized in HOL-Light as follows:

**Definition 5:** Limit of a function  $\vdash \forall f \text{ net. lim net } f = (@l. (f \rightarrow l) \text{ net})$

The function lim is defined using the Hilbert choice operator  $\mathfrak{G}$  in the functional form. It accepts a *net* with elements of arbitrary data-type A and a function f, of data-type  $A \to \mathbb{R}^m$ , and returns  $l:\mathbb{R}^m$ , i.e., the value to which the function f converges to at the given net.

Similarly, we also use the following theorem in our development:

**Theorem 1:** Sum of a geometric Progression

$\label{eq:constraint} \begin{array}{l} \vdash \ \forall \ z. \ \text{norm} \ z \ \leqslant \& 1 \ \Rightarrow \\ & ((\lambda \texttt{k.z pow} \ \texttt{k}) \ \texttt{sums} \ z \ \texttt{pow} \ \texttt{n} \ / \ (\texttt{Cx}(\& 1) \ - \ \texttt{z})) \ (\texttt{from n}) \end{array}$

Where the function f sums k (from n) ensures that the infinite summation of a multivariate sequence f is equal to k with n as the starting point.

#### 3.2 Formalization of Block Diagrams in Control Systems

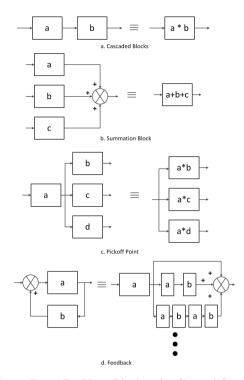

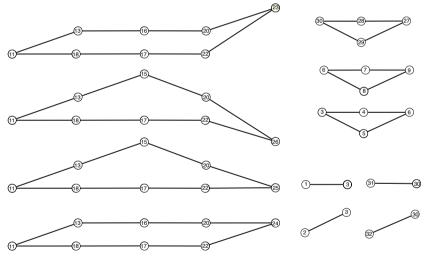

This section provides a set of formal definitions [12] of the basic building blocks of control systems, given in Fig. 3. These definitions can in turn be used to formalize a wide range of control systems in higher-order logic. The net transfer function of n subsystems connected in *cascade* is the product of their individual laplace transfer functions (Fig. 3.a).

**Definition 6:** Cascaded Subsystems

$\vdash$  series [] = Cx (&1)  $\land$  ( $\forall$  h t. series (CONS h t) h \* series t)

The function **series** accepts a list of complex numbers, corresponding to the transfer functions of all the given subsystems, and recursively returns their product. Here two type injections & and Cx are used to transform a positive integer to its corresponding real and complex number, respectively.

Fig. 3. Basic Building Blocks of a Control System

Fig. 3.b depicts a *summation junction* of transfer functions where the net transfer functions of a set of incoming branches is formed by adding their individual transfer functions. The formalization of this behavior accepts a list of complex numbers and returns their sum.

**Definition 7:** Formalization of Summation Junction

⊢ sum\_junction [] = Cx (&0) ∧ (∀ h t. sum\_junction(CONS h t) h + sum\_junction t)

The *pickoff point* represents a subsystem connected to a network of parallel branches of subsystems (Fig. 3.c):

The function **pickoff**, accepts a complex number **a**, corresponding to the transfer function of the first subsystem, and a list of complex numbers, corresponding to the transfer functions of the subsystems in the branches, and returns a list of complex numbers corresponding to the equivalent block diagram. The *feedback* block (Fig. 3.d), is the foremost element required to model closed-loop control systems. Due to the feedback signal, it primarily represents an infinite summation of branches that comprises of serially connected subsystems.

Definition 9: Branch of a Feedback Loop

⊢ ∀ a b n. feedback\_branch a b 0 = Cx (&1) ∧

feedback\_branch a b (SUC n) = series [a; b] \*

(feedback\_branch a b n)

The function feedback\_branch accepts the forward path transfer function a, the feedback path transfer function b and the number of the branches n. It returns the net transfer function for n branches of a feedback loop as a single complex number. Now, the infinite summation of all branches of the feedback loop can be modeled as the following HOL-Light function:

The HOL-Light function infsum (from n) f above provides the infinite summation a multivariate sequence f with n as the starting point. Now, we can model the behavior of the feedback loop in HOL-Light as follows:

#### **Definition 11:** Feedback

$\vdash \forall$  a b. feedback a b = series [a; (feedback\_loop a b)]

The function feedback accepts the forward path transfer function a and the feedback path transfer function b and returns the net transfer function by forming the series network of the summation of all the possible infinite branches and the final forward path transfer function, since the output is taken after the forward path a.

A couple of simplification theorems used in this paper, are as follows:

**Theorem 2:** Feedback loop simplification  $\vdash \forall a b. norm (a * b) < \&1 \Rightarrow feedback a b = a / (Cx(\&1) - a * b)$

The proof of Theorem 2 is primarily based on the infinite summation of a geometric series [10], given in Theorem 1.

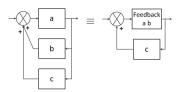

Similarly, the equivalence relationship between the block diagrams, shown in Fig. 4, has been formally verified as follows:

**Theorem 3:** Feedback loop simplification

∀ a b c. (norm (a\*b) + norm (a\*c)) < &1⇒

feedback a (sum\_junction (pickoff Cx(&1) [b;c])) =

feedback (feedback a b) c</pre>

The proof of Theorem 3 utilizes Theorem 2 along with some complex arithmetic reasoning. We use this theorem to convert any non-unity-feedback control system into a unity-feedback control system required for steady-state error analysis.

Fig. 4. Multiple Feedback Simplification Rule

## 4 Steady-State Error Analysis

We now present the formal verification of a generic expression that can be used to reason about the steady-state error of any unity-feedback system (Fig. 5), irrespective of its type and input. We proceed in this direction by first formalizing a generalized representation of the transfer function according to Equation (1).

**Definition 12:** General Transfer function  $\vdash \forall Y Z a. general_tf Y Z b = (\lambda s. Y s / (s pow b * Z s))$

The function general\_tf accepts two complex functions Y and Z of data type  $\mathbb{R}^2 \to \mathbb{R}^2$  along with a complex number b and returns the transfer function using the lambda abstraction format.

Now, the error model of unity-feedback systems in terms of the generalized representation of G(s), according to Equation (2), is as follows:

**Definition 13:** Steady-state-error-model

$\vdash \forall$  G a. uf\_error\_model G a = ( $\lambda$ s. series [Cx (&1) /s pow a; feedback\_loop (G s) (--Cx(&1))])

The function uf\_error\_model accepts a variable  $G : \mathbb{R}^2 \to \mathbb{R}^2$ , which represents the general transfer function, and a complex number  $a : \mathbb{R}^2$ , which generalizes the input type, i.e., if the input is a unit step then a = 1 and similarly a = 2and a = 3 for the ramp and parabola inputs, respectively. The function uses the functions **series** and **feedback** to capture the structure of the error model of the unity-feedback system, depicted in Fig. 5, and returns its net transfer function with data type  $\mathbb{R}^2 \to \mathbb{R}^2$ .

Now, the steady-state error can be formally defined as the limit of the net transfer function of the error model, as given in Equation (3),

```

Definition 14: steady-state-error

\vdash \forall E. steady\_state\_error E = lim (at (Cx(\&O))) (\lambda s. s (E s))

```

where the function  $\lim(\operatorname{at}(\operatorname{vec} i))(\lambda x.f x)$ , represents the limit of a function f at point i, i.e.,  $\lim_{x\to i} f(x)$  in HOL-Light. The function steady\_state\_error accepts a variable  $E : \mathbb{R}^2 \to \mathbb{R}^2$ , which represents the net transfer function of the error, and returns its corresponding steady-state error as a complex value.

Now, based on the above definitions, we verified our generic expression as the following theorem

Fig. 5. Steady-State Error of Unity-Feedback Systems

#### **Theorem 4:** Unity-feedback steady-state error

```

\begin{array}{l} \vdash \forall \ Y \ Z \ a \ b \ l \ m. \quad (\forall \ s. \ Z \ continuous \ at \ s) \ \land \ \neg(1 \ = \ Cx(\&0)) \ \land \\ \neg(m \ + \ l \ = \ Cx(\&0)) \ \land \ 0 \ \le \ b \ \land \ 1 \ \le \ a \ \land \ a \ \le \ b+1 \ \land \ (Y \ \to \ l) \\ (at \ Cx(\&0)) \ \land \ (Z \ \to \ m) \ (at \ Cx(\&0)) \ \land \ \neg(Z \ (Cx(\&0)) \ = \ Cx(\&0)) \ \land \\ (?k. \ \&0 \ < k \ \land \ (\forall s. \ norm \ s \ < k \ \Rightarrow \ norm \ (Y \ s \ / (s \ pow \ b \ * \ Z \ s)) \ < \ \&1)) \\ \Rightarrow \ steady\_state\_error \ (uf\_error\_model \ (general\_tf \ Y \ Z \ b) \ a) \ = \\ (if \ b \ = \ 0 \ then \ m \ / \ (m+1) \ else \ if \ a \ = \ b+1 \ then \ m \ / \ l \\ \ else \ Cx(\&0)) \end{array}

```

The first three assumptions are used to avoid singularities. The next two assumptions declare the allowable ranges of the system type and input characterization variables, respectively. The next assumption ( $a \le b+1$ ) defines the upper bound of the input type based on the type of the system. The next two assumptions ensure that the variables, l and m, represent the limiting values of the functions Y and Z at point 0, respectively. The last assumption is required for the feedback simplification. To the best of our knowledge, this relationship between the type of the system and its allowable input, given in Theorem 4, is not mentioned in most of the control systems literature. To ascertain our finding, we consulted some control systems experts and they confirmed our results. Missing such corner cases is a common problem in paper-and-pencil based mathematical analysis and simulation and is one of the major causes for faulty system designs. The proof of Theorem 4 is based on various properties of limit of a complex function and complex arithmetic reasoning.

The formalization presented so far in this section consumed about 300 manhours, which are mainly spent in the user guided verification due to the undecidable nature of the higher-order logic. Our proof script is available at [2]. The main benefit of this development, however, is that it greatly facilitates the formal reasoning about unity-feedback control system properties by reducing the human interaction in such proofs, as will be illustrated in the next section.

It is important to note that the universal quantification over the variables Y, Z, a and b in Theorem 4 allows us to use this result for reasoning about steady-state error of any unity-feedback control system irrespective of its type, input and behavior. To the best of our knowledge, such a generic relationship for the steady-state error for unity-feedback systems has not been reported in the control systems literature.

Now, we outline the step-wise process for reasoning about the steady-state error of unity-feedback systems using Theorem 4. The first step is to use the formal definitions, given in Section 3, to develop a formal model of the given system using its structural description. Next, we verify the equivalence of this model and the expression general\_tf Y Z b, by choosing appropriate assignments of the functions Y and Z and the variable b. Next, we express the theorem for the steady-state error of the given unity-feedback system: steady\_state\_error (uf\_error\_model (<transfer function of the given system>) a) = <steady state error>. Now, using Theorem 4 along with the fact that all of its assumptions hold for the given values of Y, Z, a and b, we can conclude the proof of steady-state error of the given unity-feedback system. In order to illustrate the effectiveness and practical utilization of Theorem 4 and the above mentioned process, we analyze a real-world control system in the next section.

## 5 Application: Pulse Width Modulation (PWM) push-pull dc-dc Converter

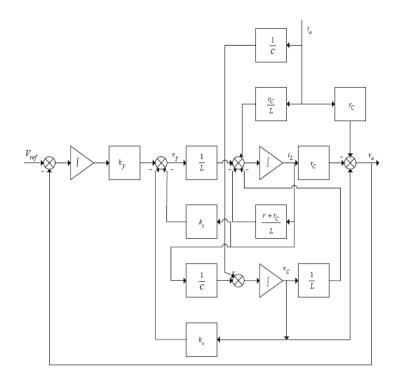

The Pulse Width Modulation(PWM) push-pull dc-dc converters are widely used to step down dc voltages and thus have many applications in areas, like aerospace applications, where dc voltage is produced and consumed. The steady-state response of this electronic device is of utmost importance and thus has been extensively studied [14,8]. A commonly used model [8] for steady-state error analysis of the PWM push-pull dc-dc converter is given in Fig. 6.

In this section, we share the experiences of a control system specialist in verifying the steady-state error relationship for the PWM push-pull dc-dc converter using our formalization. This person is a graduate student of Electrical Engineering and her research interests are in the area of mathematical analysis of control systems. The person had taken academic courses on discrete mathematics, programming languages and calculus but had no background about formal methods. We provided a two week HOL-Light extensive training to the person with major focus on formal reasoning about complex arithmetic and limits. During the course of the training as well as the case study, the person struggled in understanding the syntactical and type checking errors of HOL-Light and thus was significantly assisted in this regard.

The person initiated the exercise by developing the following higher-orderlogic model for the block diagram, given in Fig. 6. Initially, she got confused in defining multiple feedback paths while using the function pickoff and mistakenly used the transfer function of 1/s instead of 1 in the pre-fan-out block. She caught this mistake herself during the second step of our proposed approach, where the equivalence of the formal model is verified with the one obtained via the general\_tf function and the correct definition is given below:

Fig. 6. Steady-State Error Model of PWM push-pull dc-dc converters

```

Definition 15: PWM push pull dc-dc converter

∀ L C r rc Ky Kv Ki s.

dc_dc_converter L C r rc Ky Kv Ki s =

series [ Cx(&1)/s ; Ky ; feedback ( series [Cx(&1)/L;

feedback (Cx(&1)/s) (--sum_junction (pickoff (Cx(&1))

[(r+rc)/L; series [Cx(&1)/s; Cx(&1)/C; Cx(&1)/L]]))])

(--sum_junction (pickoff (Cx(&1)) [Ki;

series [Kv; Cx(&1)/s; Cx(&1)/C]])); sum_junction [rc;

series [Cx(&1)/s; Cx(&1)/C]]]

```

Where the -- symbol represents the minus operator in HOL-Light. The variables L, C, r and rc donate inductor, capacitor, the equivalent resistance in series with an inductor and the equivalent resistance in series with a capacitor, respectively. While kv, ki and ky are the voltage, current and feedback loop gains, respectively. None of these variables can be zero for the correct operation of the dc-dc converter. A subgoal of the equivalence theorem is given below, where the structure of the PWN push pull dc-dc converter is simplified to obtain its corresponding characteristic equation given in [8]:

**Theorem 5:** dc-dc converter Transfer function simplification

⊢ ∀ L C s r rc Ky Kv Ki.

¬( C \* L \* r \* rc \* Ki \* Kv \* Ky = Cx (&0)) ∧ ¬(s = Cx (&0)) ∧

¬(s pow 2 \*C \*L + s\*C\*(r + rc) +Cx(&1) = Cx(&0)) ∧

norm (inv s \* --((r+rc) \* inv L + inv (s\*C\*L))) < &1 ∧

norm ((s \* C) / ( s pow 2 \* C \* L + s \* C \* (r + rc) +

Cx(&1)) \* --(Ki + Kv \* inv (s \*C))) < &1

⇒ dc\_dc\_converter L C r rc Ky K Ki s =

(Ky \* (s\*C\*rc +Cx(&1))) / (s pow 3 \* C\* L + s pow 2 \*

C \* (r+rc+Ki) + s (Cx(&1)+Kv))</pre>

Note that none of the physical values in the model can be zero and this is ensured by the first assumption. The next two assumptions are used to avoid singularities and the last two assumptions are required for solving the feedback paths. Our control engineer was not able to guess the right set of assumptions upfront and thus added the missing assumptions during the reasoning process based on the feedback she got from the generated subgoals. Thus, it was clearly observed in this exercise that interactive theorem provers do guide their users to find the right set of assumptions.

Since our given model is a Type 1 system, therefore its steady-state-error for the unit step input should be zero[14]. The result is verified as:

**Theorem 6:** Steady-State Error for step input

```

\vdash \forall L C r rc Ky Kv Ki.

\neg (C * L * r * rc * Ki * Kv * Ky = Cx (&0)) \land

\neg (Cx (&1) + Kv = --Ky) \land

\neg (Cx (&1) + Kv = Cx (&0)) \land

(?k. &0 < k \land

(\foralls. norm s < k

<math>\Rightarrow norm ((Ky * (s * C * rc + Cx (&1))) /

(s pow 1 * (C * L * s pow 2 + s * C * (r + rc + Ki) +

Cx (&1) + Kv))) < &1))

\Rightarrow steady_state_error (uf_error_model (general_tf

(\lambdas.Ky * (s*C*rc + Cx(&1))) (\lambdas.C*L* s pow 2 +

s*C*(r+rc+Ki) + Cx(&1) + Kv ) 1) 1) = Cx(&0)

```

The first assumption ensures that none of the component in the dc-dc converter has a zero value and the next three assumptions are uesd to avoid singularities. The last assumption is for the feedback simplification.

The verification of the above theorem involves the equivalence theorem, as described in the previous section, along with Theorem 4. Besides the above theorem, the control engineer also verified the relationship of the steady-state error for ramp input. The theorem is described below:

**Theorem 7:** Steady-State Error for ramp input

⊢ ∀ L C r rc Ky Kv Ki. ¬( C \* L \* r \* rc \* Ki \* Kv \* Ky = Cx (&0)) ∧

```

\neg (Cx (\&1) + Kv = --Ky) \land

\neg (Cx (\&1) + Kv = Cx (\&0)) \land

(?k. \&0 < k \land

(\foralls. norm s < k

\Rightarrow norm ((Ky * (s * C * rc + Cx (&1))) /

(s pow 1 * (C * L * s pow 2 + s * C * (r + rc + Ki) +

Cx (&1) + Kv))) < &1))

\Rightarrow steady_state_error (uf_error_model (general_tf

(<math>\lambdas. Ky * (s*C*rc + Cx(&1))) (\lambdas. C*L* s pow 2 +

s*C*(r+rc+Ki) + Cx(&1) + Kv ) 1) 2) = (Cx(&1) + Kv) / Ky

```

The reasoning process was very similar to the one used for Theorem 6 since the same values for the functions Y and Z are used in these theorems. Further details about its verification can be found in our proof script[2].

The exercise of involving a control systems engineer for conducting these proofs was quite a learning experience for us as well. Some of the feedback that we got is shared here. The user faced many issues in interpreting the type checking and syntactical error messages generated by HOL-Light and this was the most frustrating issue for him. Thus, this is an area that can be improved. Moreover, the person was not too comfortable with the text-based interface of the theorem prover and suggested to bring in a more user-friendly graphical interface, specially for control system analysis. On the other hand, the user was quite amazed at the feedback she got from the theorem prover in understanding the behavior of the control system model and the requirement of an exhaustive set of assumptions to verify any theorem. She felt that this sort of rigorous analysis is a dire need in the case of safetycritical control system design. It was quite encouraging for us that the engineer was able to verify the goals with the basic understanding of limits and complex numbers in HOL-Light. This fact also demonstrates the effectiveness of our generic theorem.

## 6 Conclusions

This paper presents a formal framework to reason about the net transfer functions and steady-state errors of unity-feedback control systems within the sound core of a theorem prover HOL-Light. The main contribution of the paper is the formal verification of a generic theorem that facilitates in the formal reasoning about any kind of unity-feedback system. For illustration purposes, we presented a formal analysis of a PWM push pull dc-dc converter. Some of the interesting future directions of our work are to formally analyze the stability of control systems and establishing a link between the formalized Laplace transform theory[21] to be able to link time and Laplace domain models of a control system.

## References

Clayton, P., Cavalcanti, A., O'Halloran, C.: From Control Law Diagrams to Ada via Circus. Formal Aspects of Computing 23(4), 465–512 (2011)

- Ahmad, M.: Formal Verification of Steady State Errors in Unity-Feedback Control Systems (2014), http://save.seecs.nust.edu.pk/students/ahmad/ sseufcs.html

- Alur, R.: Formal Verification of Hybrid Systems. In: Embedded Software, pp. 273– 278 (2011)

- Arthan, R., Caseley, P., O'Halloran, C., Smith, A.: ClawZ: Control Laws in Z. In: Formal Engineering Methods, pp. 169–176 (2000)

- Boulton, R.J., Gottliebsen, H., Hardy, R., Kelsey, T., Martin, U.: Design Verification for Control Engineering. In: Boiten, E.A., Derrick, J., Smith, G.P. (eds.) IFM 2004. LNCS, vol. 2999, pp. 21–35. Springer, Heidelberg (2004)

- Boulton, R.J., Hardy, R., Martin, U.: A Hoare Logic for Single-Input Single-Output Continuous-Time Control Systems. In: Maler, O., Pnueli, A. (eds.) HSCC 2003. LNCS, vol. 2623, pp. 113–125. Springer, Heidelberg (2003)

- Dong, J.S., Chen, C., Sun, J.: A Formal framework for Modeling and Validating Simulink diagrams. Formal Aspects of Computing 21(5), 451–483 (2009)

- Czarkowski, D., Pujara, L.R., Kazimierczuk, M.K.: Robust Stability of State-Feedback Control of PWM DC-DC push-pull Converter. IEEE Transaction on Industrial Electronics 42(1), 108–111 (1995)

- Harrison, J.: A HOL Theory of Euclidean Space. In: Hurd, J., Melham, T. (eds.) TPHOLs 2005. LNCS, vol. 3603, pp. 114–129. Springer, Heidelberg (2005)

- Harrison, J.: Formalizing Basic Complex Analysis. Studies in Logic, Grammar and Rhetoric 10, 151–165 (2007)

- Harrison, J.: The HOL Light Theory of Euclidean Space. Journal of Automated Reasoning 50(2), 173–190 (2013)

- Hasan, O., Ahmad, M.: Formal analysis of steady state errors in feedback control systems using HOL-light. In: Proceedings of the Conference on Design, Automation and Test in Europe, DATE 2013, pp. 1423–1426 (2013)

- Herencia-Zapana, H., Jobredeaux, R., Owre, S., Garoche, P.-L., Feron, E., Perez, G., Ascariz, P.: PVS Linear Algebra Libraries for Verification of Control Software Algorithms in C/ACSL. In: Goodloe, A.E., Person, S. (eds.) NFM 2012. LNCS, vol. 7226, pp. 147–161. Springer, Heidelberg (2012)

- Hote, Y.: A New Approach to Time Domain Analysis of Perturbed PWM pushpull DC-DC Converter. Journal of Control Theory and Applications 10(4), 465–469 (2012)

- Lutovac, M.D., Tošic, D.V.: Symbolic Analysis and Design of Control Systems using Mathematica. International Journal of Control 79(11), 1368–1381 (2006)

- Mahony, B.: The DOVE approach to the Design of Complex Dynamic Processes. In: Workshop on Formalising Continuous Mathematics, pp. 167–187. NASA Conference Publication (2002)

- 17. MathWorks Simulink (2012), http://www.mathworks.com/products/simulink

- 18. Nise, N.S.: Control System Engineering. Wiley and Sons (2003)

- 19. Ogata, K.: Modern Control Engineering. Prentice-Hall (1997)

- Pike, L.: Pervasive Formal Verification in Control System. In: Formal Methods in Computer-Aided Design. Panel Discussion (2011)

- Taqdees, S.H., Hasan, O.: Formalization of Laplace Transform Using the Multivariable Calculus Theory of HOL-Light. In: McMillan, K., Middeldorp, A., Voronkov, A. (eds.) LPAR-19. LNCS, vol. 8312, pp. 744–758. Springer, Heidelberg (2013)

- Tiwari, A., Khanna, G.: Series of Abstractions for Hybrid Automata. In: Tomlin, C.J., Greenstreet, M.R. (eds.) HSCC 2002. LNCS, vol. 2289, pp. 465–478. Springer, Heidelberg (2002)

# Assertion-Based Monitoring in Practice – Checking Correctness of an Automotive Sensor Interface

Thang Nguyen<sup>1,\*</sup> and Dejan Ničković<sup>2</sup>

<sup>1</sup> Infineon Technologies AG, Austria Thang.Nguyen@infineon.com

<sup>2</sup> AIT Austrian Institute of Technology GmbH, Vienna, Austria dejan.nickovic@ait.ac.at

**Abstract.** In this paper, we evaluate the assertion-based monitoring technology for mixed-signal systems by applying it to real-world case study from the automotive domain.

We first motivate the case study by presenting the state-of-the-practice verification and validation work-flow typically used in the automotive industry. We identify the shortcomings of this work-flow, and propose a more rigorous and automated methodology based on monitoring correctness of simulated mixed signal designs with respect to assertions, which formalize in Signal Temporal Logic (STL) the requirements from the design specification.

We apply the assertion-based monitoring framework for mixed signal designs to check the correctness of Distributed System Interface (DSI3) in a modern airbag system-on-chip application. We present all the relevant steps in our proposed work-flow, evaluate the results and discuss the framework's benefits as well as its identified missing features.

## 1 Introduction

A modern car is a system-of-systems (SoS) that merges a number of embedded elements that are often developed independently. The systems in a car are heterogeneous, combining digital controllers with analog sensors and actuators. They interact with their physical environment and are interconnected through the vehicle physics, as well as communication protocols. This results in complex interactions generating emergent behaviors that are not predictable in advance. Many components in a car, such as the airbag systems, are *safety critical*. Hence, correct system integration in the automotive domain is crucial to achieve high standards with respect to safety.

Due to the heterogeneity and the complexity of components and sub-systems in modern cars, verification and validation (V&V) poses a major challenge in the

<sup>\*</sup> The research leading to these results has received funding from the ARTEMIS Joint Undertaking under grant agreement Nr. 295311 and the Austrian Research Promotion Agency FFG under the program "Forschung, Innovation und Technologie fr Informationstechnologien (FIT-IT).

F. Lang and F. Flammini (Eds.): FMICS 2014, LNCS 8718, pp. 16-32, 2014.

<sup>©</sup> Springer International Publishing Switzerland 2014

automotive domain and represents the main bottleneck in the design process. Verification by simulation and manual testing are the dominant methods used in the V&V practice of the automotive industry. However, these techniques have the weakness of being ad-hoc, inefficient and prone to human errors.

The research community has investigated a number of approaches that address V&V issues for mixed-signal systems. Formal verification of systems combining continuous and discrete dynamics has been mainly studied by the *hybrid systems* [18,2] community. It consists in computing over-approximations of reachable sets of states of the circuit, modeled as a hybrid automaton (differential equations with mode switching). Despite the important progress achieved in this research field in recent years [13], such technique [6,14,17,24,1] still cannot scale up to the size and complexity of transistor-level circuit models. In addition to hybrid system verification, there are other orthogonal analytical approaches to study similar systems. For instance, static analysis and abstract interpretation were used to develop a framework for inferring continuous time properties of systems consisting of synchronous components that interact by quasi-synchronous composition [5].

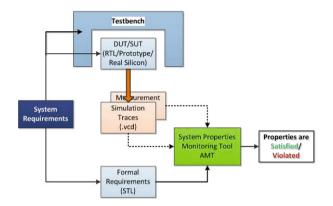

Assertion-based monitoring is a promising technology for verification of analog and mixed-signal (AMS) designs, i.e. designs that consist of interacting digital and analog components. It successfully exports some well-established ingredients from digital verification to the AMS domain, while retaining the relative simplicity and scalability of the simulation-based verification. In essence, assertionbased monitoring frameworks consist of an assertion language used to formalize the requirements that describe the correct interaction between analog and digital components, including timing constraints due to the communication delays. The formal assertions are then automatically translated into *monitors*, programs that read simulation traces of the design-under-test and check for the assertion satisfaction/violation.

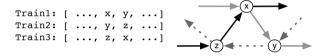

Signal Temporal Logic (STL) [19,20] is an assertion language extending Linear Temporal logic (LTL) [22]. LTL enables declarative, formal and compact specification of reactive system requirements. Its original use was for evaluating sequences of states and events in digital systems. A typical property stated in temporal logic is always (req -> eventually! ack). This property says that it is always the case that a request **req** eventually triggers an acknowledgment ack. STL extends LTL to specification of properties involving both digital and real-valued variables defined over dense time. Offline monitoring of STL was implemented in the tool AMT [21]. The monitoring flow based on using STL for formalizing assertions and monitoring them with AMT is depicted in Figure 1. This specification language has been successfully used in the past for monitoring in various application domains, such as analog circuits [16], biochemical reactions [7], synthetic biological circuits [4] and music [11]. STL has also been extended in several other directions. In [11], the authors developed a first attempt of time-frequency logic-based (TFL) specification, and successfully applied it to detect music patterns. TFL expresses frequencies as atomic predicates (using sliding FFT to evaluate the intensity of the signal around a frequency) and time

using intervals and the classic temporal operators. The classic qualitative semantics of STL was recently extended with more powerful and precise notions of quantitative semantics [12,10,9] (or robustness degree), providing a real value measuring the level of satisfaction or violation for a trajectory of the property of interest. Several tools, such as BIOCHAM [23], S-TaLiRo [3] and Breach [8], are available to perform robustness analysis on the time series collected in wet-lab experiments or produced by simulation-based techniques.

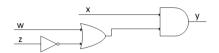

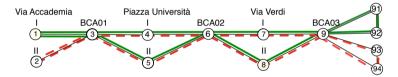

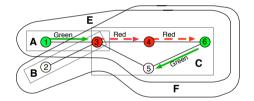

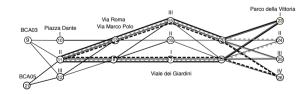

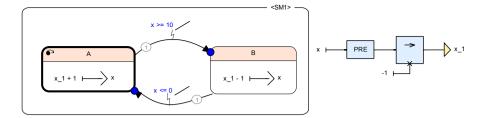

Fig. 1. Assertion-based monitoring flow with STL assertion language and AMT tool

In this work, we apply the assertion-based monitoring framework from Figure 1 to check the correctness of a sophisticated automotive sensor interface integration in a modern system-on-chip (SoC) airbag system, developed by Infineon Austria AG. The correct integration of the SoC with its sensor interface is specified in the Distributed System Interface (DSI3) protocol standard [15]. We present the work-flow of the case study in which we use STL to formalize DSI3 requirements and AMT tool to monitor the simulation traces. We evaluate the case study results and discuss the lessons that we learned regarding the applicability of this approach in industry.

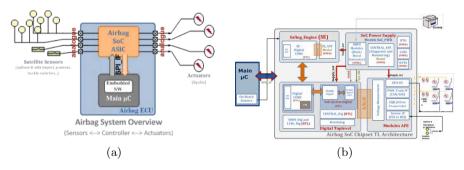

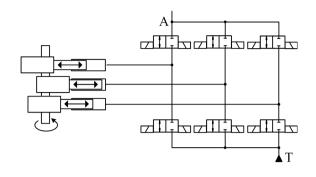

# 2 Verification Flow in the Automotive Domain – State-of-the-Practice

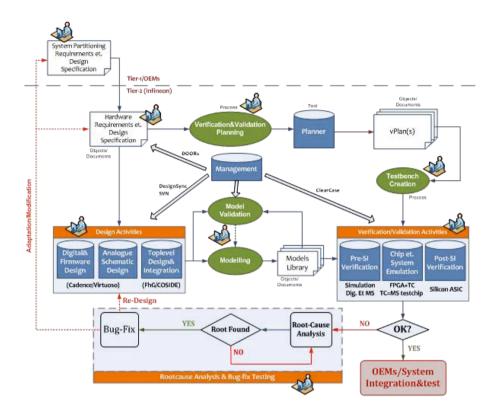

Figure 2 illustrates the state-of-the-practice verification work-flow by Power Train and Safety department at Infineon Technology Austria AG. The work-flow describes as well collaboration between Tier-1 (system developer and integrator) and Tier-2+ (HW - Hardware and SW Software element developers) teams. The work-flow starts with the requirements and specifications phase at the Tier-1 level. In this step system functionalities and related HW/SW components are defined. The HW requirements are provided to Tier-2 supplier, e.g.

Fig. 2. Verification workflow for complex mixed signal IC development

Infineon so that HW concept and design specification can be further defined. Right after this phase, the design and verification/validation activities will be launched (almost in parallel). The design activities covers conceptual and design work, which including digital and firmware design, analog schematic design and top-level integration. Most of the tasks defined during design phase are mainly done under the Cadence Virtuoso/AMS-Designer tooling environment, whereas for the proof-of-concept, the COSIDE (Complex System Integrated Development Environment) from Fraunhofer IIS is used. Nearly at the same time, verification engineering team also based on the hardware requirements and design specification starts their verification and validation planning process. This process (with the support from some planning tools, e.g.: in-house tool) results in a verification plan which then used by verification/validation engineer for test bench creation. The verification plan is categorized with different verification approaches including:

**Pre-silicon verification** covers all type of simulation at different design level (block, module and chip top-level) using different techniques from mixed-signal to mixed-abstraction simulation.

- Emulation at integrated circuit (IC) and system level uses FPGA with mixed-signal test chip as an early prototype for verifying many scenarios that are very impractical or impossible to simulate. These scenarios are usually long term test, stress test or sensor data transmission test over a long period of time (e.g.: could result in data interception of million sensor message). This approach is an innovative approach, developed by Infineon and its customer. The approach has been recently accepted as publication in the SAE Journal of Passenger Car Electrical and Electronic System (SAE Society of Automotive Engineer).

- **Post-silicon Verification** refers to verification of the real IC in the lab. It is an extension of those test scenarios which could not be done using emulation system. This is due to the fact that emulation system is mainly designed to cover certain safety critical functions (e.g.: sensor interfaces or the deployment interfaces) but not the full design functionalities. Through extensive tests done in the lab, the post-silicon verification should maximize the test coverage at HW component level before being delivered to the system integrator Tier-1 supplier.

Finally, the rootcause analysis and bug-fix testing is considered as an undesired part of the verification activities. However, when a bug is found, rootcause analysis and bug-fix testing could significantly contribute to increase the verification as well as the project timing and effort. This is because the bug-fix could be a change in the design (re-design) of a modification/adaptation in the specification. In any case, this would trigger the verification regression run, meaning cost in time and effort. Despite the fact that verification/validation activities for mixed-signal IC development are well established, the verification work-flow above still involves simulation and manual testing methods used in the practice of the automotive industry. These methods consist in verification engineers creating input stimuli, executing simulation models and observing the waveforms for correctness. They are known for the following weaknesses: ad-hoc, inefficient and prone to human errors. In addition, it is widely accepted that for complex mixedsignal multi-cores System-on-Chip (SoC) IC products, verification accounts for around 60%-70% of the total development. This is especially true for automotive safety critical SoC product with a high number of analogue interfaces to the physical components, e.g.: an airbag SoC chipset in an automotive airbag system application. As such, any approaches which could help to reduce design and verification effort, improve time-to-market and product quality, e.g.: formal verification, boost up verification runs using hardware acceleration platform and verification automation are of extreme interest.

# 3 Signal Temporal Logic

In this section, we give a brief overview of the Signal Temporal Logic (STL) that we use to formalize the case study requirements. For the full details regarding the assertion language and the monitoring algorithms for STL, we refer the reader to [20]. We consider the STL logic with both *future* and *past* operators, interpreted over a finite multi-dimensional signal w. A signal w is a partial function  $w : \mathcal{T} \to \mathbb{B}^m \times \mathbb{R}^n$ , where  $\mathcal{T}$  is the interval [0, d) denoting a time domain of duration d. Let  $X = \{x_1, \ldots, x_m\}$  be the set of real valued variables and  $P = \{p_1, \ldots, p_n\}$  the set of STL propositions. We denote by  $w|_x$  and  $w|_p$  the projection of the signal wto a real-valued or propositional variable  $x \in X$  or  $p \in P$ . A *Boolean constraint* over X is a predicate of the form  $x \circ c$ , where  $x \in X$ ,  $o \in \{<, <=, =, >=, >\}$  and  $c \in \mathbb{Q}$ . The syntax of an STL formula  $\varphi$  over X and P is defined by the grammar

$$\begin{array}{l} \alpha := p \mid x \circ c \\ \varphi := \alpha \mid \operatorname{not} \varphi \mid \varphi_1 \text{ or } \varphi_2 \mid \varphi_1 \text{ until!}_I \varphi_2 \mid \varphi \text{ since!}_I \varphi_2 \end{array}$$

where  $p \in P$ ,  $x \in X$ ,  $c \in \mathbb{Q}$  is a constant and I is an interval of the form [a, b], [a, b), (a, b], (a, b),  $[a, \infty)$  or  $(a, \infty)$  where  $0 \le a \le b$  are rational numbers. As in LTL, basic STL operators can be used to derive other standard Boolean and temporal operators, in particular the time-constrained eventually!, once!, always, and historically operators:

| $\texttt{eventually!}_{I} \varphi = true \texttt{ until!}_{I} \varphi$ | $	ext{once!}_{I} arphi = true 	ext{ since}_{I} arphi$ |

|------------------------------------------------------------------------|-------------------------------------------------------|

| $always_I \varphi = not eventually!_I not \varphi$                     | $historically_I \varphi = not once_I not \varphi$     |

The semantics of an STL formula  $\varphi$  with respect to an *n*-dimensional signal w is described via the satisfiability relation  $(w, t) \models \varphi$ , indicating that the signal w satisfies  $\varphi$  at time t, according to the following recursive definition, where  $\mathcal{T}$  is the time domain.

$$\begin{array}{ll} (w,t) \models x \circ c & \leftrightarrow w|_{x}[t] \circ c \\ (w,t) \models p & \leftrightarrow p[t] = 1 \\ (w,t) \models \operatorname{not} \varphi & \leftrightarrow (w,t) \not\models \varphi \\ (w,t) \models \varphi_{1} \operatorname{or} \varphi_{2} & \leftrightarrow (w,t) \models \varphi_{1} \operatorname{or} (w,t) \models \varphi_{2} \\ (w,t) \models \varphi_{1} \operatorname{until}_{I} \varphi_{2} \leftrightarrow \exists t' \in (t \oplus I) \cap \mathcal{T} (w,t') \models \varphi_{2} \text{ and} \\ & \forall t'' \in (t,t') (w,t'') \models \varphi_{1} \\ (w,t) \models \varphi_{1} \operatorname{since}_{I} \varphi_{2} \leftrightarrow \exists t' \in (t \ominus I) \cap \mathcal{T} (w,t') \models \varphi_{2} \text{ and} \\ & \forall t'' \in (t',t) (w,t'') \models \varphi_{1} \end{array}$$

$$(1)$$

A formula  $\varphi$  is satisfied by w if  $(w, 0) \models \varphi$ .

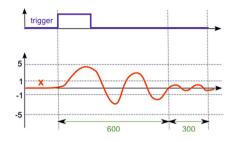

*Example 1.* An example of a property that can be expressed in STL is a mixed signal stabilization property that has the following requirements:

- The absolute value of a continuous signal x is always less than 5;

- When the (Boolean) trigger rises, within 600 time units abs(x) has to drop below 1 and stay like that for at least 300 time units.

This property is illustrated in Figure 3 and expressed in STL as:

```

always (abs(x) < 6 and

(rise(trigger) \rightarrow eventually!_{[0,600]} always_{[0,300]} (abs(x) < 1)))

```

Fig. 3. Example: stabilization property

## 4 Case Study

#### 4.1 Case Study Description

The increasing number of airbags in a vehicle, the requirement to comply with stricter safety requirements, while costs must be reduced has brought automotive airbag system application to a new approach with SoC design, shown in Figure 1. Consequently, verification has dramatically increasingly challenges the design of complex mixed-signal System-on-Chip (SoC) products. This is especially true for automotive safety critical SoC products with a high number of analogue interfaces to the physical components, e.g.: an airbag SoC chipset in an automotive airbag system application.

**Fig. 4.** A typical airbag system: (a) overview; (b) airbag SoC chipset top-level implementation architecture

During the operation, the sensors (buckle switches, accelerometers, pressure sensors, etc.) mounted in key locations of the vehicle, continuously measure the positions of impact, the severity of the collision and other variables. This information is provided to the airbag SoC chipset in form of analog signals. The airbag SoC chipset translates the analog sensor signals into digital words. The translated digital sensor data is reported to the main uC via the SPI (Serial Peripheral Interface) communication. Based on this information the airbag main uC decides if, where (location) and when the airbags (e.g.: actuators) is deployed. Accordingly, this makes the verification (computer-based simulation) and validation (lab evaluation) of the airbag SoC product, especially the sensor interfaces become a challenging task, mainly because of:

- Verification for the airbag SoC and its sensor interfaces has to cover real-time embedded mixed signal domains.

- Failure during the reception, decoding and processing of sensor data in the airbag controller system can originate unexpected or false deployment events of the airbag system putting human safety in danger.

- Most of the functionalities of sensor interfaces can only be verified at the system level of the chip and at the system application level. Only using classical mixed-signal simulation approach becomes a bottle neck.

- Many verification scenarios of the sensor interfaces such as long-term verification run with checking of millions sensor data frames are not suitable using computer-based simulation.

In addition, reducing time-to-market and first time right design in automotive electronics industry, which are key requirements in project to win customer and market share, has posed a great challenge to the design and verification team. With this case study, we are evaluating the assertion-based monitoring methodology on the modern airbag system application with the focus on the new airbag sensor interface using the new DSI3 standard, promoted by the DSI consortium<sup>1</sup>. DSI3 goals are to improve performance, reduce cost and promote open standard but still remains at the lowest cost possible compare to the current widely used PSI5 standard. Higher performance is achieved among others, by increased communication speed from the slave sensor to the master.

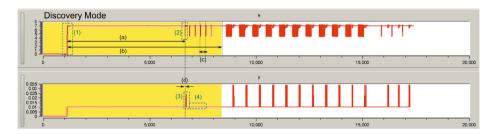

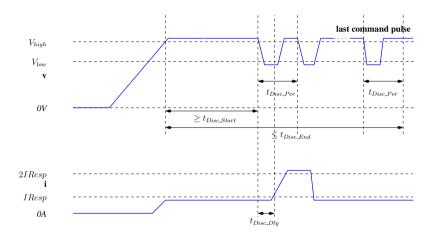

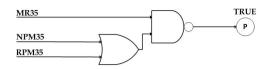

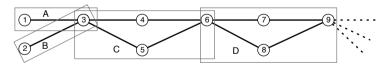

#### 4.2 Formalization of DSI3 Discovery Mode Requirements

In this section, we formalize DSI3 discovery mode requirements, illustrated in the highlighted section of Figure 5. In the DSI3 discovery mode,  $\mu C$  interacts with the sensor interfaces via the voltage (v) and current (i) lines. It is the initial phase of the DSI3 standard protocol and it works as follows. First, the power apply is turned on, resulting in the voltage ramp from 0V to V\_high (phase (1) in Figure 5). Then,  $\mu C$  issues commands for probing the presence or absence of sensors. These commands are converted by the SoC to analog pulses carried over the voltage lines. In Figure 5, (2) shows a discovery pulse command. A sensor that is connected to the sensor interface responds by an inverted analog pulse carried over the current line (shown in (3) of Figure 5). Finally, if a sensor is not connected to the sensor interface, the discovery pulse command is not followed by any response on the current line, as illustrated in (4) of Figure 5.

In addition to the correct ordering of events, described in the previous paragraph, the DSI3 Bus Standard also defines a number of timing requirements that must be met by any correct implementation of the protocol:

<sup>&</sup>lt;sup>1</sup> http://www.dsiconsortium.org

- 1. The minimal time between the moment that the power is applied and the first discovery pulse command is sent, as shown by (a) in Figure 5;

- 2. The maximal total duration of the discovery mode, measured between the moment that the power is applied and the end of the sensor probing by the  $\mu C$ , as illustrated by (b) in Figure 5;

- 3. The expected time between any two consecutive discovery pulse commands ((c) in Figure 5); and

- 4. The expected time between a discovery pulse command and the response by the sensor (or its lack of response if the sensor is not connected), as shown by (d) in Figure 5.

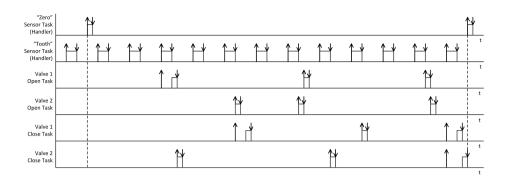

Fig. 5. DSI3 Discovery Mode requirements - overview

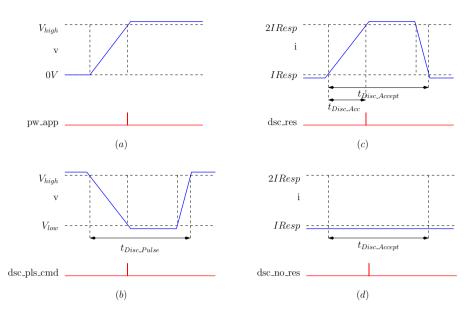

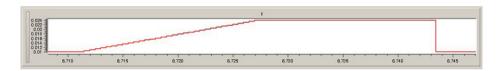

**Specification of Events of Interest.** In order to be able to formalize these timing properties defined by the DSI3 Bus Standard, we first must be able to accurately characterize and recognize the "events" corresponding to power application, discovery pulse commands, the sensor response and its lack of response. The graphical specification of these patterns is shown in Figure 6.

We first consider applying power to the SoC, illustrated in Figure 6 (a), which is characterized by a ramp that goes from 0V to  $V_{high}$ . We consider that the power is on, characterized by the event pw\_app, when the voltage signal goes above  $V_{high}$ .

```

% Regions of interest

1: define b:v_zero := a:v == 0;

2: define b:v_above_high := a:v >= Vhigh;

3: define b:v_between_high_zero := a:v > 0 and a:v <= Vhigh;

% Power applied

4: define b:pw_app :=

5: rise(b:v_above_high) and

6: (b:v_between_high_zero since! fall(b:v_zero);</pre>

```

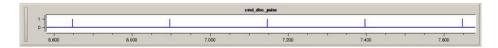

A *discovery pulse command* is carried on the voltage line and is characterized by its *shape* and *duration*, as shown in Figure 6 (b). The DSI3 standard requires

**Fig. 6.** Graphical specification of events of interest: (a) power applied; (b) discoverly pulse command; (c) sensor response; and (d) sensor no response

that the distance between two consecutive discovery pulse commands is  $t_{Disc\_Per}$  (± tolerance). In order to formalize this requirement in STL (shown in the next paragraph), we first define the regions of interest that are needed to capture a discovery pulse command (lines 1-3). We then characterize the correct shape of the pulse (lines 4-7) and its duration (lines 8-11), resulting in the specification of the discovery pulse command (line 12).

```

% Regions of interest

define b:v_above_high := a:v >= Vhigh;

1:

2:

define b:v_below_low := a:v <= Vlow;

3:

define b:v\_between\_high\_low := a:v >= Vlow and a:v <= Vhigh;

% Pulse shape

define b:cmd_dp_shape :=

4:

5:

fall(b:v_above_high) and

6:

(b:v_between_high_low_until! b:v_below_low_until!

b:v_between_high_low until! b:v_above_high);

7:

% Pulse end-to-end timing

define b:cmd_dp_e2e_timing :=

8:

fall(b:v_above_high) and

9:

((not rise(b:v_above_high)) until![tDisc_Pulse-tol:tDisc_Pulse+tol]

10:

11:

rise(b:v_above_high));

```

```

% Pulse = shape + end-to-end timing

12: define b:cmd_dp := b:cmd_dp_e2e_timing and b:cmd_dp_shape;

```

The specification of the sensor response (dsc\_res) and no response (dsc\_no\_res) patterns (Figures 6 (c) and (d)) is very similar to the specification of the discovery pulse command, and we skip their presentation due to the lack of space.

Assertions for DSI3 Discovery Mode Requirements. After specifying events of interest, we are ready to formalize the requirements that relate these events and define the timing constraints between them, as described in the DSI3 bus protocol, and summarized in Figure 7.

Fig. 7. Graphical specification of DSI3 discovery mode requirements

We start with the requirement saying that between the power applied event and the first discovery pulse command, there must be at least  $t_{Disc\_Start}$  time elapsed. We formalize this requirement with the following assertion.

```

% Timing between power applied and first discovery pulse commands

1: first_disc_cmd_dly assert:

2: always (b:pw_app -> (((not b:cmd_dp ) until![tDisc_Start:inf]

3: b:cmd_dp);

```