### A Methodology for the Design and Implementation of

### Communication Protocols for Embedded Wireless Systems

by

Thomas Eugene Truman

B.S. (University of California, Berkeley) 1992 M.S. (University of California, Berkeley) 1994

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

#### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Robert W. Brodersen, Chair Professor Jan M. Rabaey Professor Paul Wright

Spring 1998

### This dissertation of Thomas Eugene Truman is approved:

Chair

Date

Date

Date

University of California, Berkeley

Spring 1998

A Methodology for the Design and Implementation of Communication Protocols for Embedded Wireless Systems

Copyright 1998

by

Thomas Eugene Truman

#### Abstract

A Methodology for the Design and Implementation of Communication Protocols for Embedded Wireless Systems

> by Thomas Eugene Truman

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert W. Brodersen, Chair

Communication protocol design involves 4 complementary domains: specification, verification, performance estimation, and implementation. Typically, these technologies are treated as separate, unrelated phases of the design: formal specification, formal verification, and implementation, in particular, are rarely approached from an integrated systems perspective. For systems that are implemented using a combination of hardware and software, a significant technical barrier to this integration is the lack of an automated, formal mapping from an abstract, high-level specification to a detailed implementation in either synchronous hardware or non-deterministically interleaved software threads.

This dissertation presents a design methodology that uses a combination of formal and informal mappings to refine a high-level specification into an implementation. A taxonomy of formal languages that are commonly used for protocol or finite-state machine (FSM) description is developed and used to identify when a particular formal model is most useful in the design flow. The methodology relies on an informal specification to develop a formal description that can be formally verified at the asynchronous message-passing behavioral level. Central to the methodology is application of compositional refinement verification to relate a synchronous implementation finite-state machine to an asynchronous specification state machine. An architectural template for an embedded communication system is used to facilitate the mapping between the specification and a software implementation, and a prototype operating system and low-level interface units provide the necessary interprocess communication infrastructure between hardware and software.

Professor Robert W. Brodersen, Chair

# Dedication

In memory of my grandfather, John M. Hornbeck, Sr., 1920-1994 and my sister, Loriann H. Truman, 1969-1992

# Contents

| Chapter 1                                                                                                                                                                                                                                                                                                                     | 1                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Introduction                                                                                                                                                                                                                                                                                                                  | 1                |

| 1.1 Overview                                                                                                                                                                                                                                                                                                                  | 1                |

| <ul> <li>1.2 Dimensions of the Problem Space: Specification, Verification, Performance Estimation, and Implementation.</li> <li>1.2.1 The specification problem.</li> <li>1.2.2 The verification problem.</li> <li>1.2.3 "Correctness" and performance.</li> <li>1.2.4 Relating abstract models to implementation.</li> </ul> | 5<br>6<br>7<br>8 |

| 1.3 Abstract Services and the OSI Protocol "Stack" 1                                                                                                                                                                                                                                                                          | 10               |

| 1.4 An approach to integrating protocol design disciplines 1                                                                                                                                                                                                                                                                  | 15               |

| 1.5 Summary of Contributions 1                                                                                                                                                                                                                                                                                                | 19               |

| 1.6 Outline of the dissertation                                                                                                                                                                                                                                                                                               | 20               |

| Chapter 2                                                                                                                                                                                                                                                                                                                     | 2                |

| System Requirements2                                                                                                                                                                                                                                                                                                          | 2                |

| 2.1 Overview                                                                                                                                                                                                                                                                                                                  | 22               |

| 2.2 An informal high-level description of the InfoPad system                                                                                                                                                                                                                                                                  | 25               |

| 2.3 A "message-passing" architectural partitioning.       2         2.3.1 The InfoNet network infrastructure       3         2.3.1.1 Mobility support       3         2.3.1.2 Multimedia I/O support       3         2.3.2 Architecture of the InfoPad terminal.       3                                                      | 31<br>31<br>32   |

| 2.4 Service Requirements: Performance aspects vs. functional aspects                                                                                                                                                                                                                                                          | 36               |

| 2.5 Following the methodology through to implementation: the design of the InfoPad terminal                                                                                                                                                                                                                                   |                  |

| 2.5.1 Hardware support for remote I/O |    |

|---------------------------------------|----|

| 2.5.1.1 Design trade-offs             |    |

| 2.5.1.2 IPbus Description             |    |

| 2.5.2 Wireless Interface Subsystem    |    |

| TX Interface                          |    |

| RX Interface                          |    |

| FPGA Interface                        |    |

| 2.5.3 Microprocessor Subsystem        | 55 |

| 2.5.4 Microprocessor Interface Chip   |    |

| 2.5.5 User Interface I/O Peripherals  |    |

| 2.5.5.1 Graphics Subsystem            |    |

| 2.5.5.2 Pen Subsystem                 |    |

| 2.5.5.3 Audio Subsystem               |    |

| 2.5.5.4 Video Interface               |    |

| 2.5.6 Evaluation and Measurements     | 59 |

| 2.5.6.1 Architectural Evaluation      |    |

| Processor Utilization                 |    |

| Remote-I/O Processing Latency         | 61 |

| Communications Protocol Support       |    |

| 2.5.6.2 Implementation Evaluation     |    |

| Power consumption                     |    |

| Form factor                           |    |

| 2.6 Summary                           | 67 |

| 6.0 Summary                           |    |

| Chapter | 3 | • • • • • • • • • • • • • • • • • • • • | 6 | 9 | ) |

|---------|---|-----------------------------------------|---|---|---|

|---------|---|-----------------------------------------|---|---|---|

## Protocol Design and Formal Specification Languages ......69

| 3.1 Overview                                         | 69 |

|------------------------------------------------------|----|

| 3.2 Specification of Protocols                       | 70 |

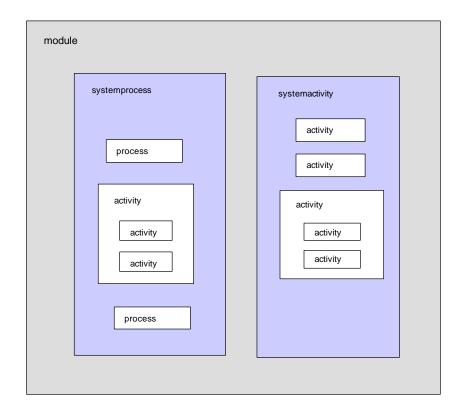

| 3.2.1 A formal model of protocol systems             | 71 |

| 3.2.2 Models of concurrency and communication        | 73 |

| 3.2.2.1 Semantics of event ordering                  | 74 |

| 3.2.2.2 True- and quasi-parallelism                  |    |

| 3.2.2.3 Communication Synchrony                      |    |

| 3.2.3 Formal Languages for Protocol Specification    |    |

| 3.2.3.1 Standardized FDTs for Protocol Specification |    |

| Estelle                                              | 81 |

| SDL                                                  |    |

| LOTOS                                                | 88 |

| 3.2.3.2 Specialized Languages                        |    |

| 3.2.3.3 The Synchronous Languages                    |    |

| 3.2.4 Summary of Formal Languages                    |    |

| y 0.0                                                |    |

| Chapter 494                                                                                                                                                                                                                                                                                                                                                                                         | F      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Practical Approaches to the Formal<br>Verification of Communication<br>Protocols94                                                                                                                                                                                                                                                                                                                  | ł      |

| 4.1 Overview of formal verification       94         4.2 Model Checking       97                                                                                                                                                                                                                                                                                                                    |        |

| 4.2.1 Symbolic Model Checking.984.2.2 Partial Order Reduction.1004.2.3 Symmetry Reduction1024.2.4 Compositional Refinement Verification.103                                                                                                                                                                                                                                                         | 5      |

| Chapter 5                                                                                                                                                                                                                                                                                                                                                                                           | }      |

| A Hardware Implementation<br>Methodology Using Refinement<br>Verification108                                                                                                                                                                                                                                                                                                                        | 5      |

| 5.1 Overview                                                                                                                                                                                                                                                                                                                                                                                        | 3      |

| 5.2 Refinement and verification of a generalized data transfer network                                                                                                                                                                                                                                                                                                                              | Ĺ      |

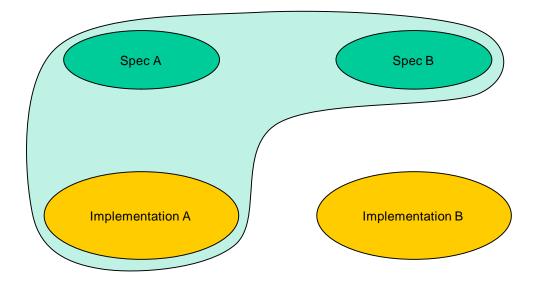

| 5.3 Zen and the art of protocol abstraction       114         5.3.1 A divide-and-conquer approach       115         5.3.2 Generalized interfaces       116         5.3.2.1 Specifications, implementations, and abstract variables       117         Abstract variables       118         Symmetry reductions       118         5.3.2.2 The role of refinement maps and witness functions       121 | 53739  |

| 5.4 Refinement Verification in SMV.1245.4.1 Layers.1245.4.2 Refinement1265.4.3 Abstract signals.1275.4.4 Symmetry reduction techniques1285.4.4.1 Restrictions on Scalarsets1285.4.4.2 Dealing with asymmetry128                                                                                                                                                                                     | 437339 |

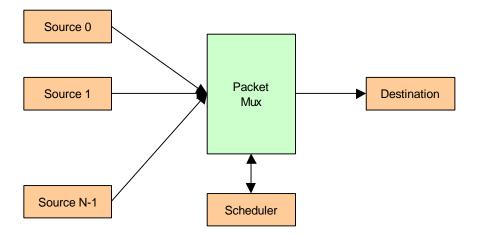

| 5.5 SDL Specification of a Packet Multiplexing system                                                                                                                                                                                                                                                                                                                                               |        |

| 5.6 Sequential implementation of the switch                                                                                                                                                                                                                                                                                                                                                         |        |

| 5.7 Outline of the proof                                                                                                                                                                                                                                                                                                                                                                            |        |

| 5.8 SMV Specification       136         5.8.1 Specifying data integrity at the atomic transfer level       136         5.8.1.1 The atomicSend layer       136         5.8.1.2 The input_spec layer       138                                                                                                                                                                                        | 3      |

| 5.8.1.3 The output_spec layer                                             | 141       |

|---------------------------------------------------------------------------|-----------|

| 5.8.1.4 The recv_spec layer                                               | 143       |

| 5.8.2 Switch input refinement: unordered, sequential transfers into the s | witch 143 |

| 5.8.2.1 The seqSend layer                                                 | 144       |

| 5.8.2.2 The seqStore layer                                                | 145       |

| 5.8.2.3 Proving sequential transfers imply atomic transfers               | 147       |

| 5.8.3 Switch output refinement                                            | 152       |

| 5.8.3.1 The seqFetch layer                                                | 153       |

| 5.8.3.2 Proving sequential output meets the specification                 | 154       |

| 5.8.4 Receiver Specification                                              | 156       |

| 5.8.5 Proving completeness and ordering at the receiver                   | 157       |

| 5.8.5.1 Breaking symmetric structures                                     | 158       |

| 5.9 Verification results                                                  | 159       |

| Chapter 6 | 6 1 | <b>61</b> |

|-----------|-----|-----------|

|-----------|-----|-----------|

## An Implementation Methodology for Embedded Systems......161

| 6.1 Overview                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2 The relationship between specification languages and implementation                                                                                                                                                                                                                                                                   |

| 6.3 An architectural template for wireless systems1676.3.1 A domain-specific implementation template1706.3.2 A template for computation and communication in mixedhardware/software implementations1726.3.3 Partitioning strategy: the SDL process as the smallest partitioning unit1736.3.3.1 System partitioning and code generation175 |

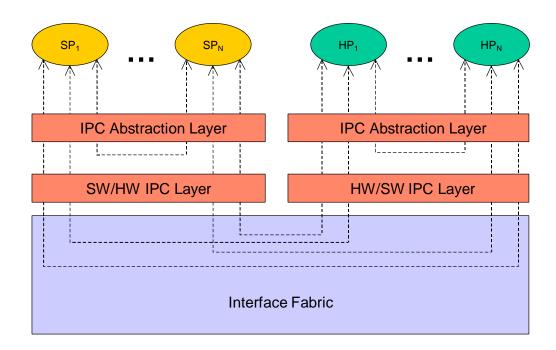

| 6.4 Interprocess communication support                                                                                                                                                                                                                                                                                                    |

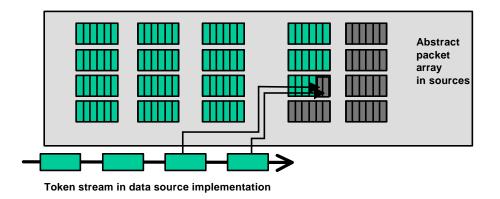

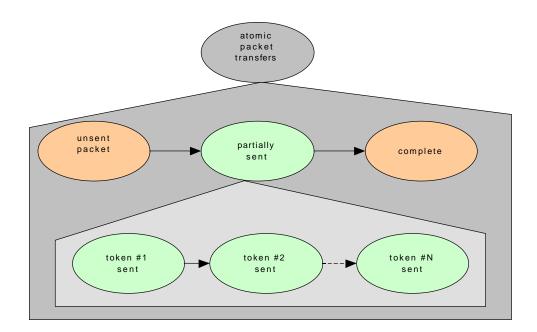

| 6.5 IPos: operating system support in the InfoPad system1846.5.1 Data sources, sinks and streams1866.5.1.1 Hardware-hardware and software-software sources and sinks1876.5.1.2 Crossing the hardware/software boundary1896.5.2 Timers191                                                                                                  |

| 6.6 Current status and possible extensions                                                                                                                                                                                                                                                                                                |

| <b>Chapter 7</b> | ••••••••••••••••                        | 195 |

|------------------|-----------------------------------------|-----|

| Chapter /        | ••••••••••••••••••••••••••••••••••••••• | 190 |

### Practical strategies for integrating formal methods in protocol design and implementation......195

| 7.1 Overview                                                                                                                                                                                                                           | 95                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 7.2 An informal system-level specification       1         7.2.1 Delay, bandwidth and reliability constraints       1         7.2.2 System-level services for I/O servers and clients       1                                          | 197                      |

| 7.3 Designing the data link protocol                                                                                                                                                                                                   | 201                      |

| 7.4 Physical layer interface27.4.1.1 Bit-level synchronization27.4.1.2 Frame synchronization27.4.1.3 Discussion of heuristics and design tradeoffs27.4.1.4 Signal strength measurements & antenna diversity2                           | 205<br>207<br>208        |

| 7.5 Media access protocol for frequency-hopping modems                                                                                                                                                                                 | 213<br>214<br>215<br>215 |

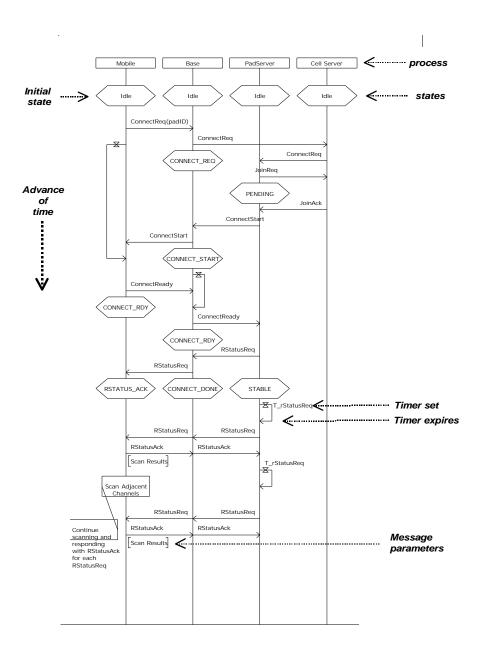

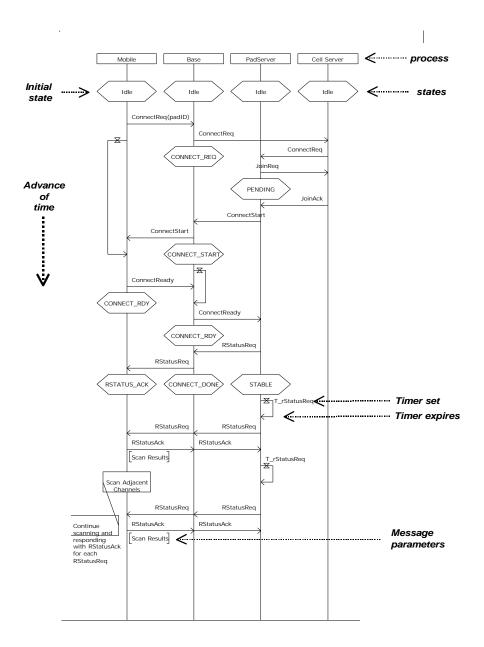

| 7.6 Link management protocols       2         7.6.1.1 Overview of message sequence charts       2         7.6.2 Establishing the link       2         7.6.3 Maintaining the link       2         7.6.3.1 Handoff between cells       2 | 219<br>220<br>223        |

| 7.7 Formal description and verification of the system       2         7.7.1 Message Sequence Chart specifications       2         7.7.2 SDL specifications       2         7.7.3 Promela       2                                       | 227<br>228               |

| Chapter 8                                                                                                                                                                                 | 232        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Conclusions and Future Work                                                                                                                                                               | 232        |

| Bibliography                                                                                                                                                                              | 236        |

| Appendix A                                                                                                                                                                                | 241        |

| Measurement-based characterizat<br>an indoor wireless channel                                                                                                                             |            |

| A.1 Introduction                                                                                                                                                                          |            |

| A.2 Measurement Setup                                                                                                                                                                     |            |

| A.3 Results of Measurements<br>A.3.1 Stationary Environment<br>A.3.2 Non-stationary Environment                                                                                           |            |

| <ul> <li>A.4 Analysis</li> <li>A.4.1 Rate of change of signal strength</li> <li>A.4.2 Frequency dependence of time-variation</li> <li>A.4.3 Time-dependence of channel quality</li> </ul> | 251<br>252 |

| A.5 Conclusion                                                                                                                                                                            | 259        |

| Appendix B                                                                                                                                                                                | 260        |

| Finite-state model for mobility                                                                                                                                                           |            |

| protocols in InfoPad                                                                                                                                                                      | 260        |

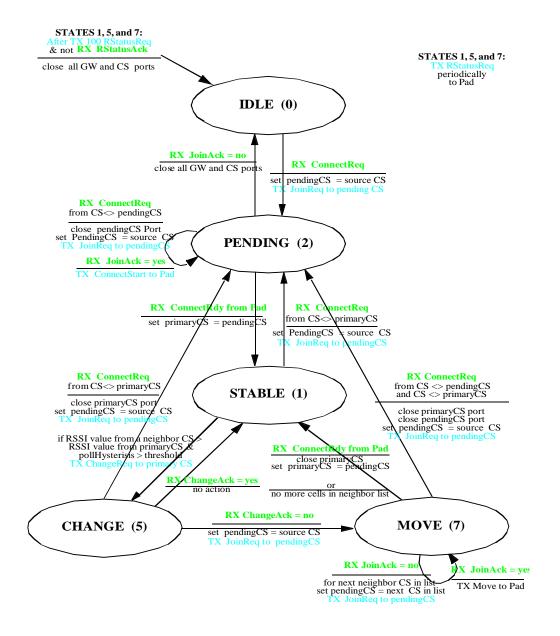

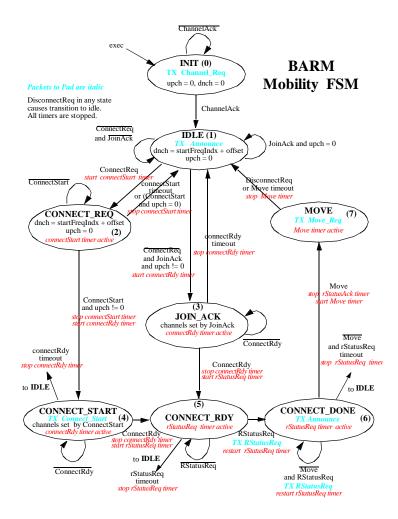

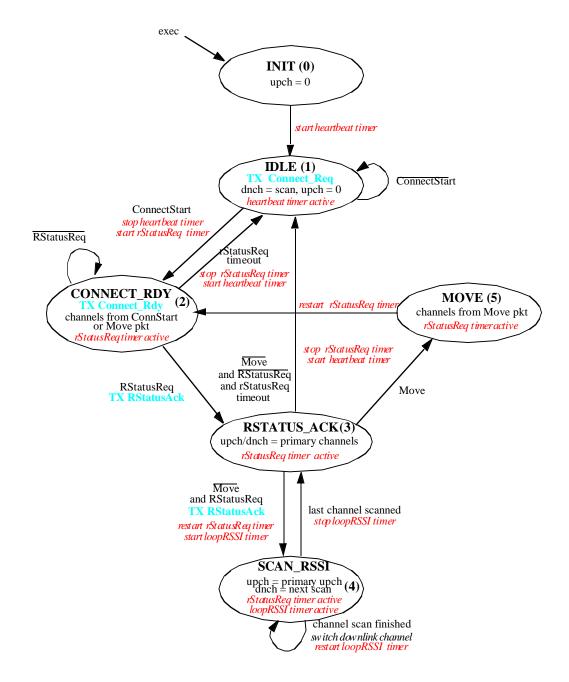

| <ul> <li>B.1 State transition diagrams for InfoNet/InfoPad protocols</li> <li>B.1.1 Pad Server</li> <li>B.1.2 Basestation</li> <li>B.1.3 Mobile Client</li> </ul>                         |            |

| B.2 Promela Code                                                                                                                                                                          |            |

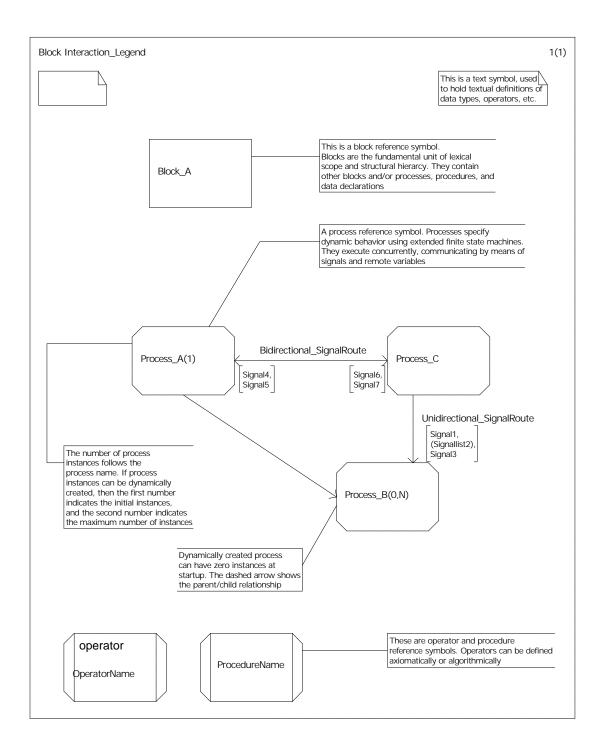

| Appendix C<br>Glossary of notation and SDL lege                                                                                                                                           |            |

| C.1 Notation |

|--------------|

|--------------|

# List of Figures

| Figure 1– 1. OSI Protocol Layers                                                                                                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Figure 1– 2. Mixed Formal/Informal design flow for data link protocols16                                                                         |  |  |  |  |  |

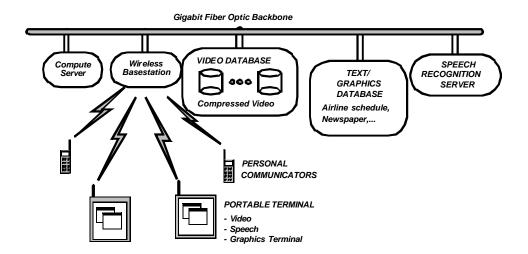

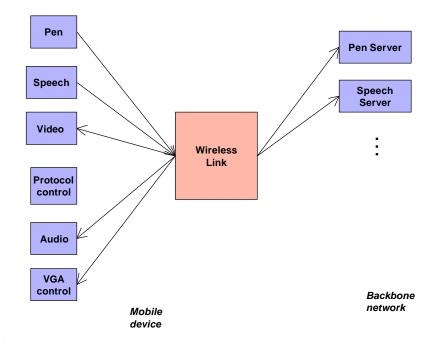

| Figure 2– 1. The InfoPad System Architecture26                                                                                                   |  |  |  |  |  |

| Figure 2– 2. Message sequence chart illustration (explanatory items in bold) $\dots 29$                                                          |  |  |  |  |  |

| Figure 2– 3. The InfoPad portable multimedia terminal                                                                                            |  |  |  |  |  |

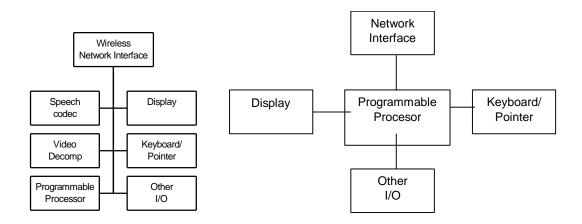

| Figure 2– 4. InfoPad computation resource partitioning (left) vs. traditional computer architecture (right)                                      |  |  |  |  |  |

| Figure 2– 5. IPBus and architectural organization of dataflow                                                                                    |  |  |  |  |  |

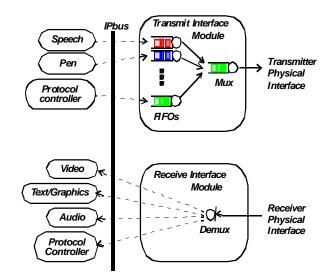

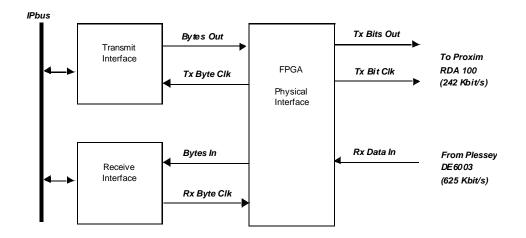

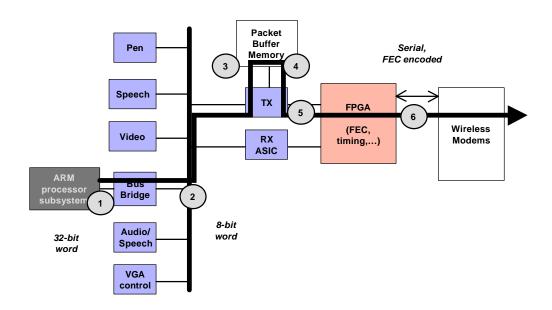

| Figure 2– 6. Block diagram of wireless interface subsystem                                                                                       |  |  |  |  |  |

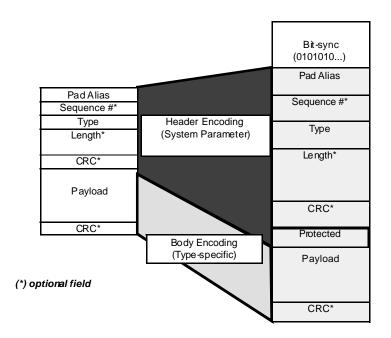

| Figure 2– 7. Packet Format                                                                                                                       |  |  |  |  |  |

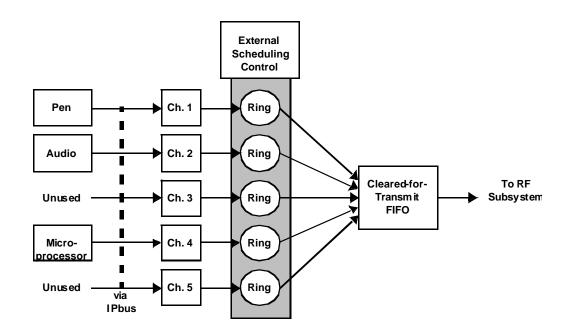

| Figure 2– 8. Logical organization of the TX buffering scheme                                                                                     |  |  |  |  |  |

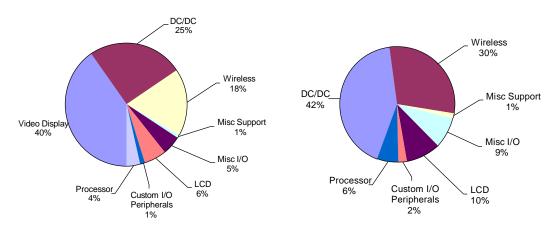

| Figure 2– 9. Power breakdown by subsystem with video display (left) and without video display (right)64                                          |  |  |  |  |  |

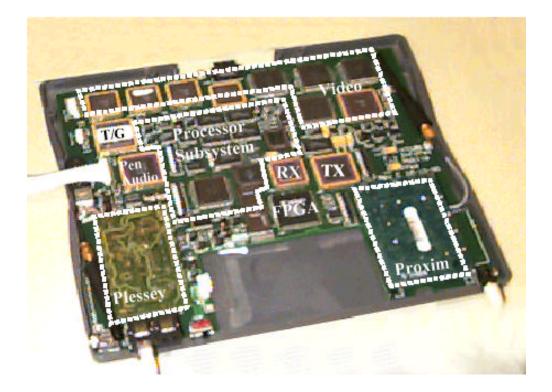

| Figure 2– 10. Interior view of the InfoPad terminal                                                                                              |  |  |  |  |  |

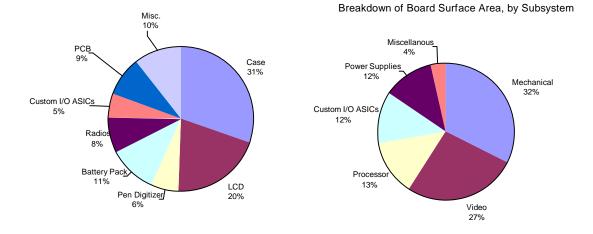

| Figure 2– 11. Weight Breakdown by Subsystem (left), and surface area of board by subsystem (right)67                                             |  |  |  |  |  |

| Figure 3– 1. Multiple assignment in synchronous parallelism77                                                                                    |  |  |  |  |  |

| Figure 3– 2. Pseudo-code for concurrent processes                                                                                                |  |  |  |  |  |

| Figure 3– 3. Estelle concurrency constructs                                                                                                      |  |  |  |  |  |

| Figure 3– 4. Inter-module communication in Estelle                                                                                               |  |  |  |  |  |

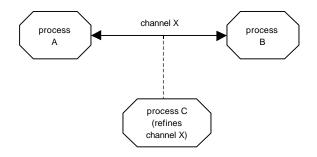

| Figure 3– 5. SDL channel refinement example                                                                                                      |  |  |  |  |  |

| Figure 4– 1. Interleaved process pseudo code10                                                                                                   |  |  |  |  |  |

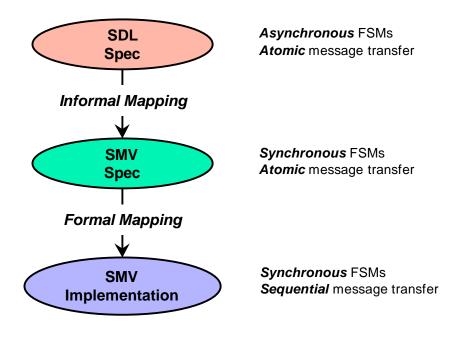

| Figure 5– 1. A "semi-formal" refinement methodology110                                                                                           |  |  |  |  |  |

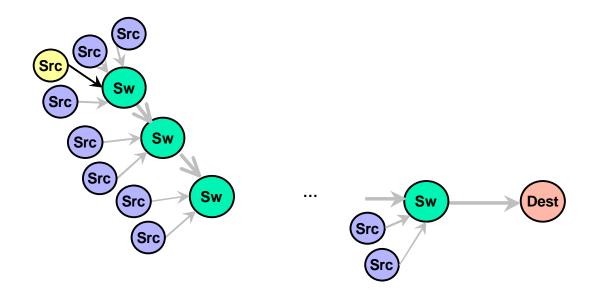

| Figure 5– 2. Generalized data transfer network110                                                                                                |  |  |  |  |  |

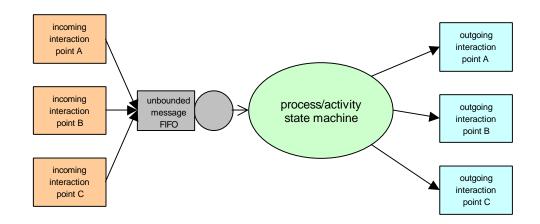

| Figure 5– 3. Message-passing view of system architecture112                                                                                      |  |  |  |  |  |

| Figure 5– 4. The InfoPad implementation architecture                                                                                             |  |  |  |  |  |

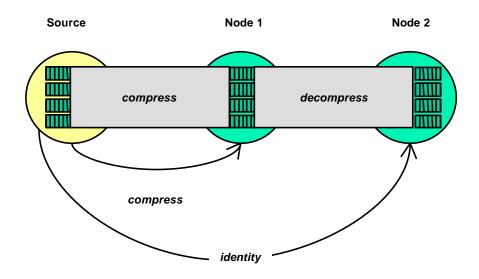

| Figure 5– 5. Example of a generalized interface: <i>specifications</i> define relationships between the original source and the node of interest |  |  |  |  |  |

| Figure 5– 6. Using abstract history variables to remember the past119                                                                            |  |  |  |  |  |

| Figure 5– 7. Refinement hierarcy123                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5– 8. Simplifying the verification problem by using abstractions in the environment                                                                                              |

| Figure 5– 9. Packet Mux System                                                                                                                                                          |

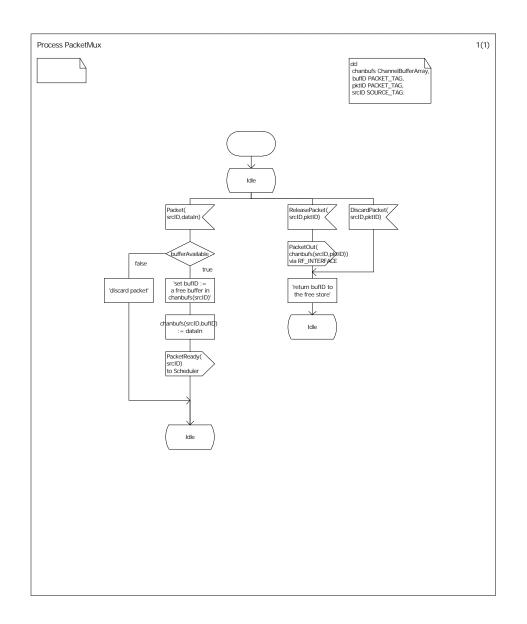

| Figure 5– 10. SDL Specification for Packet Mux132                                                                                                                                       |

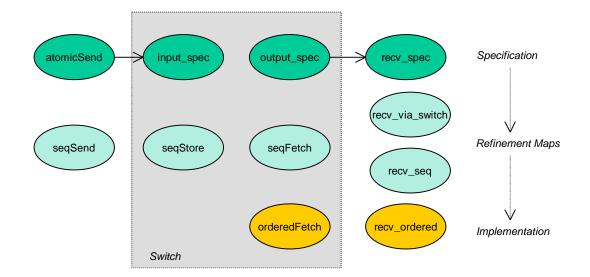

| Figure 5– 11. Organization of Layers                                                                                                                                                    |

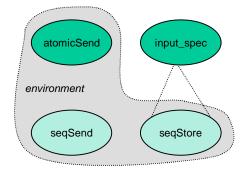

| Figure 5– 12. Verification environment for sequential input                                                                                                                             |

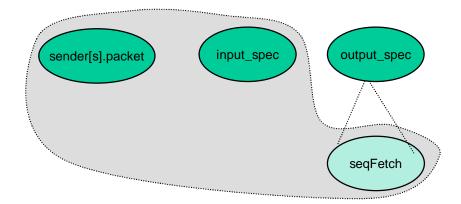

| Figure 5– 13. Verification environment for sequential output                                                                                                                            |

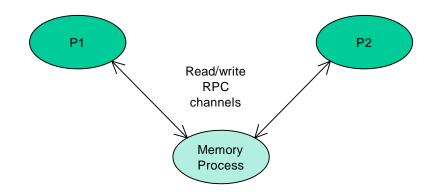

| Figure 6– 1. Modeling a shared memory system using SDL166                                                                                                                               |

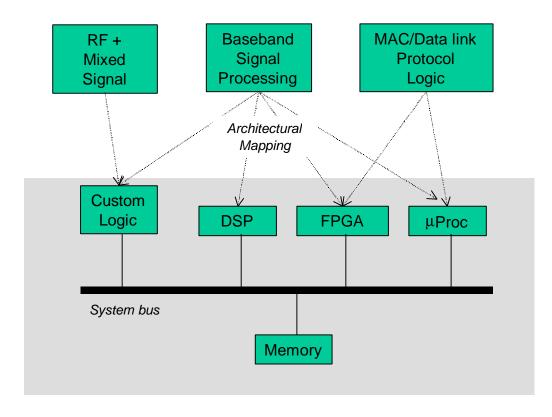

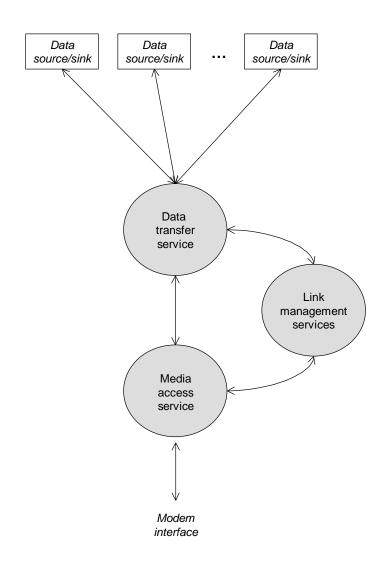

| Figure 6– 2. Typical Embedded System Architecture170                                                                                                                                    |

| Figure 6– 3. Architectural template for embedded system implementation 172                                                                                                              |

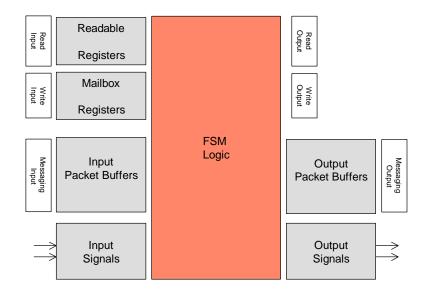

| Figure 6– 4. Hardware process template177                                                                                                                                               |

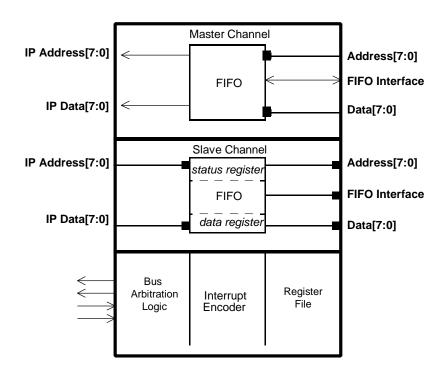

| Figure 6– 5. IPBus interface architecture                                                                                                                                               |

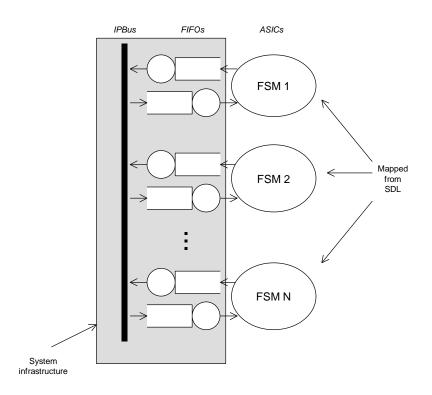

| Figure 6– 6. Logical organization of IPBus packet-transfer interface                                                                                                                    |

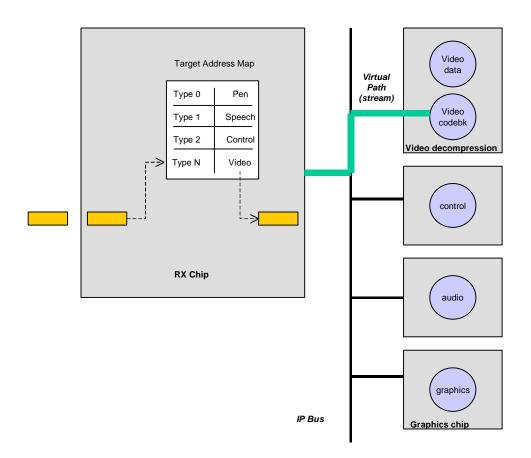

| Figure 6– 7. Hardware-to-hardware stream example: RX chip to Video decompression module                                                                                                 |

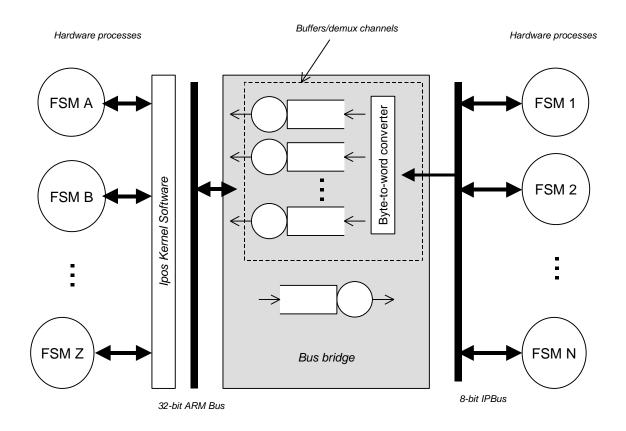

| Figure 6– 8. Bus bridge and <i>IPos</i> kernel                                                                                                                                          |

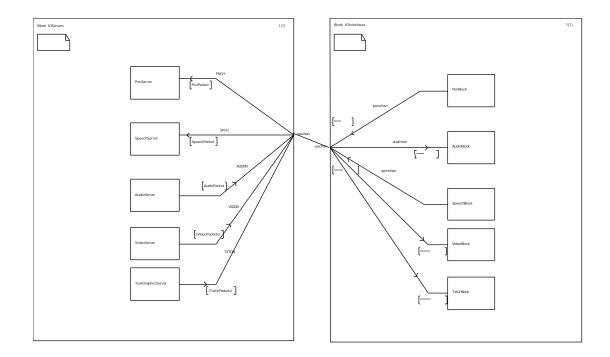

| Figure 7– 1. Top-level system view: I/O servers and clients                                                                                                                             |

| Figure 7– 2. InfoPad data link protocol architecture                                                                                                                                    |

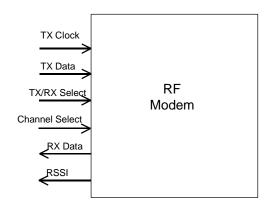

| Figure 7– 3. Signaling interface to generic RF modem                                                                                                                                    |

| Figure 7– 4. Data link frame format                                                                                                                                                     |

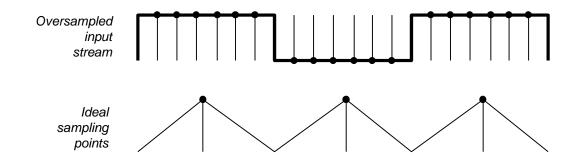

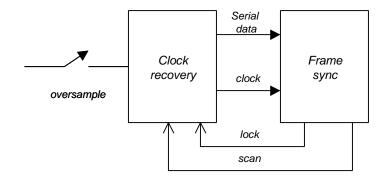

| Figure 7– 5. Clock recovery illustration                                                                                                                                                |

| Figure 7– 6. Interaction of frame and clock synchronization units                                                                                                                       |

| Figure 7– 7. Modified preamble incorporating antenna diversity                                                                                                                          |

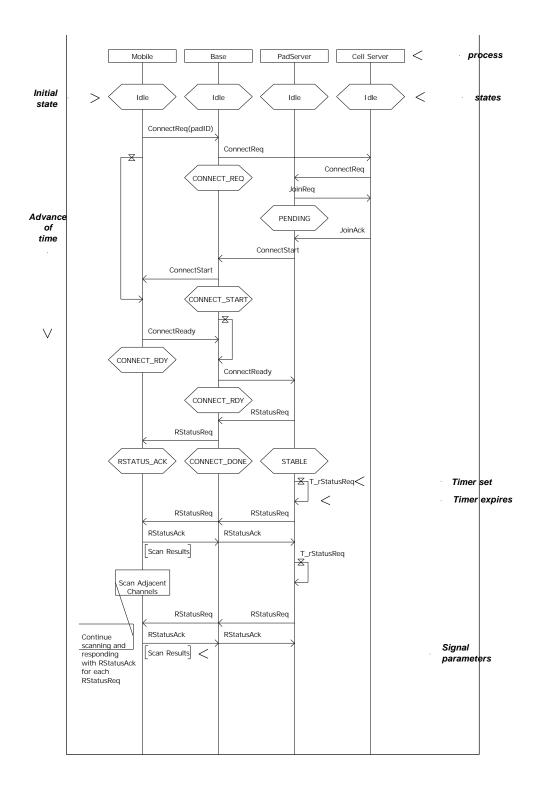

| Figure 7– 8. Link establishment protocol (without bit errors or lost packets) 222                                                                                                       |

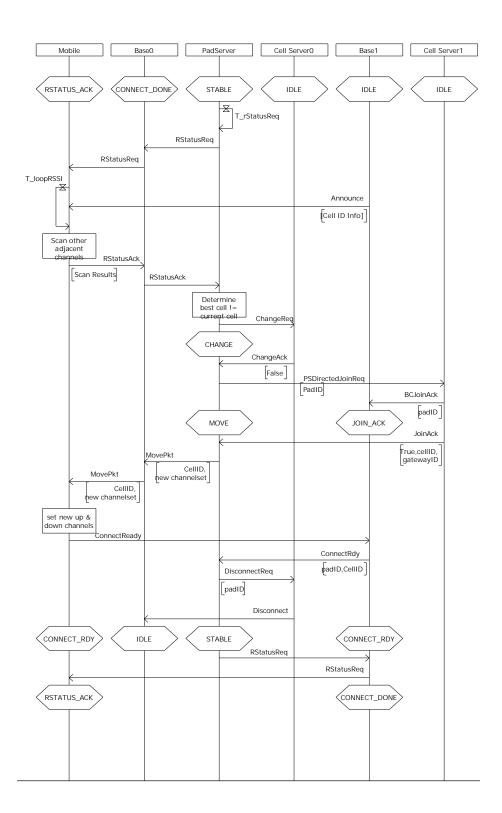

| Figure 7– 9. Message sequence chart for perfectly-executed handoff224                                                                                                                   |

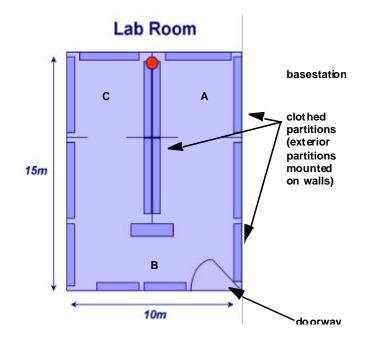

| Fig. A– 1. Measurement Environment – Path of user moves continuously through the points A-B-C                                                                                           |

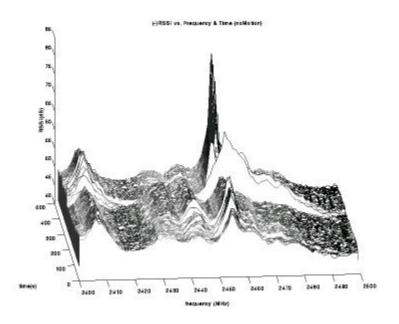

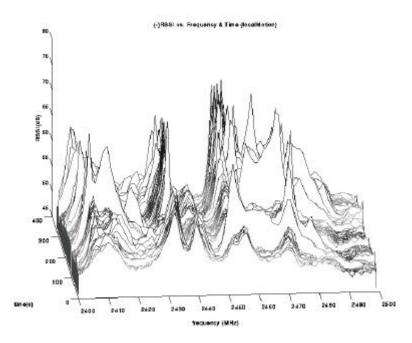

| Figure A– 2. Attenuation (negative of RSSI in dB) over a 5-minute interval (stationary)                                                                                                 |

| Figure A– 3. Attenuation (negative of RSSI in dB) over a 5-minute interval (non-<br>stationary)                                                                                         |

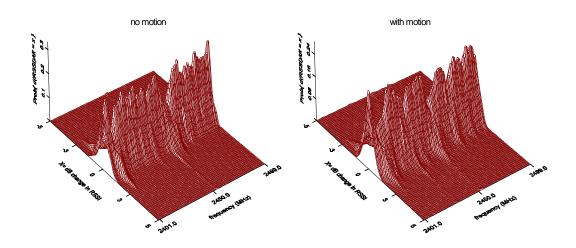

| Figure A– 4. Empirical probability density plot of derivative of signal strength as a function of time, for stationary ( <i>left</i> ) and non-stationary ( <i>right</i> ) environments |

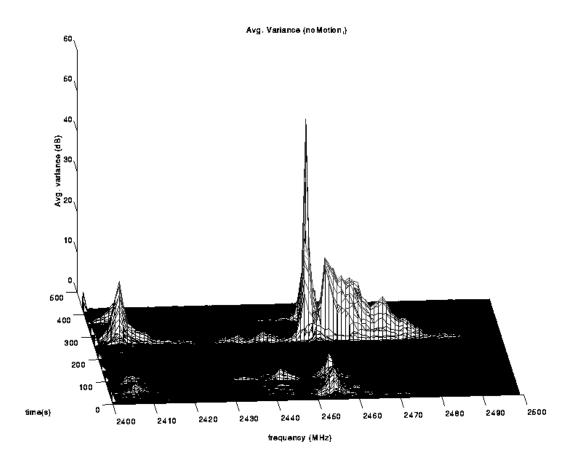

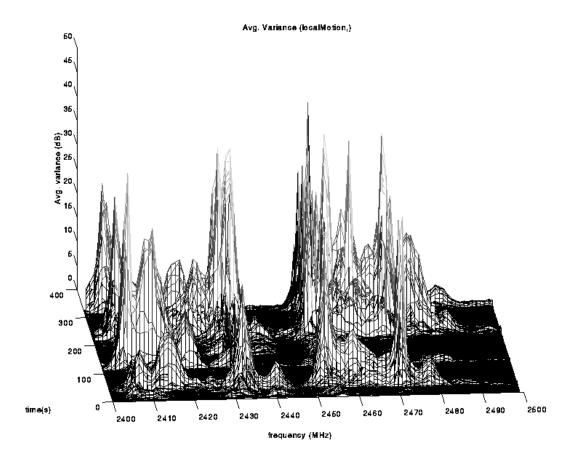

| Figure A– 5. Variance over a 5-second sliding window for stationary-user configuration                                               |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Figure A– 6. Variance over 5-second sliding window for non-stationary user configuration                                             |  |  |  |  |  |

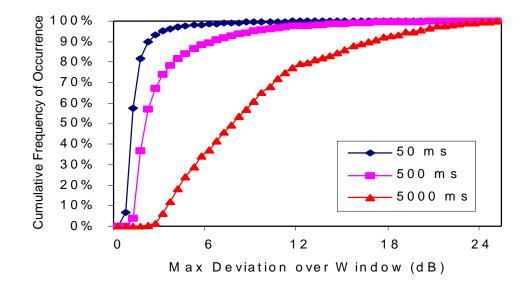

| Figure A– 7. Empirical complimentary distribution for maximum deviation over variable time windows of 50, 500, and 5000 milliseconds |  |  |  |  |  |

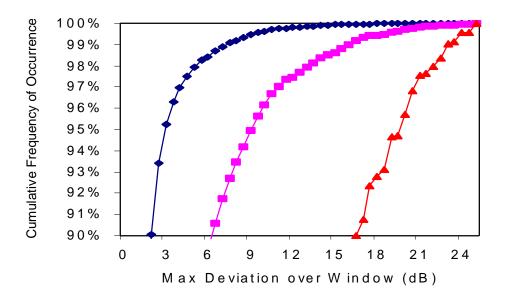

| Figure A– 8. Zoomed view of Figure A– 7256                                                                                           |  |  |  |  |  |

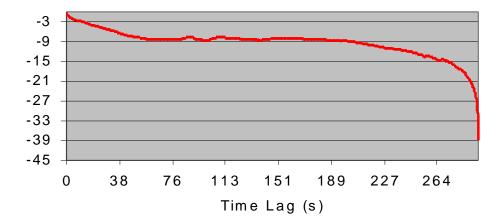

| Figure A– 9. Autocovariance of received signal strength, averaged over frequency band                                                |  |  |  |  |  |

| Fig. B– 1. State-machine view of the Pad Server mobility protocol261                                                                 |  |  |  |  |  |

| Figure B– 2. Basestation Mobility Finite State Machine                                                                               |  |  |  |  |  |

| Figure B– 3. Mobility state machine for mobile client                                                                                |  |  |  |  |  |

| Fig. C– 1. SDL Block interaction diagram                                                                                             |  |  |  |  |  |

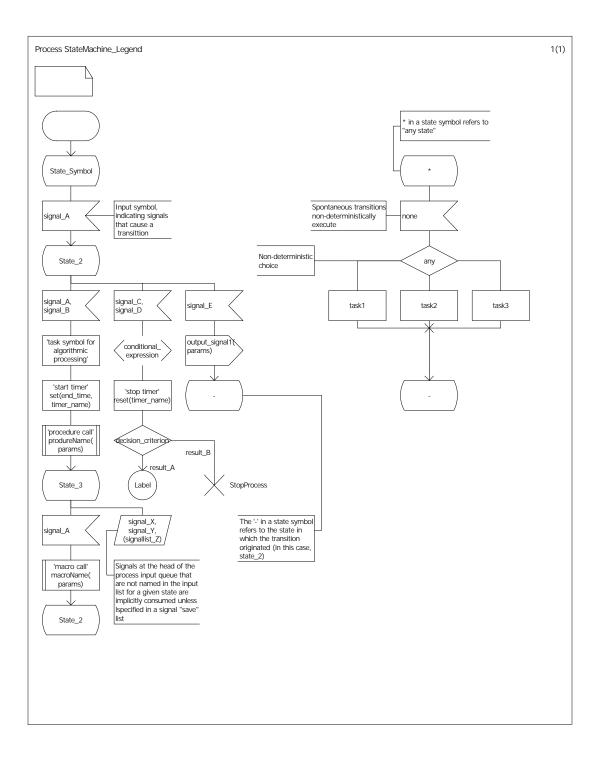

| Fig. C– 2. SDL state machine legend                                                                                                  |  |  |  |  |  |

| Fig. C– 3. Message Sequence Chart graphical legend                                                                                   |  |  |  |  |  |

# Acknowledgments

"It is not the critic who counts; not the man who points out how the strong man stumbles, or where the doer of deeds could have done better. The credit belongs to the man who is actually in the arena, whose face is marred by dust and sweat and blood; who strives valiantly; who errs, and comes short again and again; because there is not effort without error and shortcoming; but who does actually strive to do the deeds; who knows the great enthusiasms, the great devotions; who spends himself in a worthy cause, who at the best knows in the end the triumphs of high achievement and who at the worst, if he fails, at least fails while daring greatly, so that his place shall never be with those cold and timid souls who know neither victory nor defeat." -Theodore Roosevelt.

Perhaps the most difficult aspect of writing this dissertation was trying to place a linear order on concepts: the first chapter must be followed by a second, which is followed by a third, and so on, implicitly leading the reader to believe that one idea is in some way more fundamental than another. I find this way of thinking very unnatural, and as I write this final section I find that once again I am faced with the impossible task of placing an order on the people to which I feel indebted. I have opted for an order that is mostly chronological, or at least the way that I remember arriving at this point in life. In any case, my perspective throughout graduate school is that my education is a process, rather than a product. The relationships with the people around me at Berkeley – both on and off the campus – are by far the most invaluable aspect of the past six years.

My choice of electrical engineering and computer science as a profession is largely the result of my grandfather, who in the midst of a Pascal programming course that he was taking (at age 70!) would frequently ask for help with the problem solving part of his homework assignments. At the time (1987), I was intent on a career in medicine, and was spending far too many hours in the quantitative analysis lab trying to determine the composition of unknown inorganic compounds, and the temptation to distract myself with programming problems was too strong to resist.

With the help and guidance of Dan Morrow, then a professor at a local college, the Pascal I picked up during this time opened the door for a part-time job with Pacific Western Systems. (Dan is now the president of PWS). The next several years with PWS immersed me in a mix of hardware and software projects, and soon I found my interest in problem solving and system building far outweighed my interest in medicine.

In my junior year at Berkeley (1990-1991), I found that my first-choice lecture to introductory course to solid-state devices and low-level circuit design was full with a rather long waiting list. Thus, I decided to go with a different section that was taught by a post-graduate instructor, Bill Barringer.

During the first week of class, Bill described the lab in which he was working as one that "turned algorithms into architectures," and invited students to drop by and see what they did. I took him up on the offer, and after a discussion about my hardware/software background, Bill introduced me to his former advisor, Bob Brodersen (who became my graduate advisor) – they were both looking for someone with experience in embedded systems to work with Bill on a real-time image processing system. In retrospect, I doubt that my path through graduate school and my work with Bob Brodersen would have occurred without the fortuitous influence of the "course crashing" system at Cal.

X٧

My final undergraduate year at Berkeley brought two life-changing events. The first was the death of my younger sister in an auto accident, and the second was my decision to stay at Berkeley for graduate school. As part of my formative history, these events are intertwined because it was during the process of dealing with the loss of my sister that I began to seek resolution to the open questions that I had about life purpose and meaning. This exploration involved an intense grappling with issues of faith and God, and end the end I came to fully embrace a relationship with the Creator.

In September of 1992, I met Jolly Chen in a course on how to do a startup, and he pointed me in the direction of the First Presbyterian church in Berkeley. It was here that I became deeply involved in Crossroads, a community that became my extended family. Peter Akemann, John Warren, Michele Loberg (now Sullivan), and Andrea Hoover (now *Truman*!) invited me, during my first visit, to an afternoon at Great America. They are still among my closest friends: I married Andrea, Peter and Michele were in our wedding, and John and Lori Burrows-Warren are still involved with us on a day-to-day basis. My vision for this dissertation came together during a Presidents Day weekend trip to Santa Barbara to visit Jay and Michele Sullivan, and my vision for my next phase of life has grown fantastically during walks, talks, and weekend retreats with John and Lori.

The list of people who have been an integral part of my life in Berkeley seems endless, and looking back it is clear that I was more involved outside of the Cal campus than within it. Marc and Suzi Coudeyre, Jill Moriarty (Wait), John and Lailina Nadell, Jeannie Lee, Brad Loftin, Dan Lam, Jason Gong, Kim Wells, Todd McIlraith, Martin Donaldson, Ryan Grant, Dave Hoffman and Debbie Mossman-Hoffman, Kelly and Ole Bentz, Liz and Jolly Chen, Nancy McNabb, Alan and Dorene Marco, Timothy and Kate Kam, and Joel and Barbie Kleinbaum are close friends that I share many memories with.

There were several friends whose consistency in hanging out over a long period of time gives me a deep sense of connection and history. Peter Akemann and I had many interesting discussions at Fat Slice about real analysis. Early on, Brad Hall, and later Alan Marco, and I met weekly for lunch for several years – something I already miss. The monthly lunches with John Fanous had a huge impact on my vision of community and life purpose. Jon Schmidt, who taught me everything I know about the architectural history of North Berkeley, continuously amazed me with his willingness to drive across town to meet me on a moment's notice. My walks with Marc Coudeyre around Piedmont, or around Rockridge or North Berkeley with Joel Kleinbaum were times that drove home the fact that I have had an incredible opportunity to live in a place that is truly unique – culturally, architecturally, and in the diversity of people that live in the Berkeley area.

My colleagues at Cal also played a significant here, both in and out of Cory Hall. Roger Doering, Trevor Pering, and I were confined to a tiny office on the 4<sup>th</sup> floor of Cory Hall during the first 3 years; out of that office – and our discussions, arguments, and collaborations – came the core of the InfoPad. Roger is an incredible teacher, generous with his time, and taught me a lot about embedded system design. Trevor is one of the few other graduate students that had a life outside of Cory: his stories about Cal Band, acapella chorus, jazz band, and orienteering were always fun to hear. When I moved to the 5<sup>th</sup> floor, Tony Stratakos kept me in stitches with his stories of trying to acquire a cup of coffee at Peets or Starbucks ("coffee boy"). Rick Han, who traveled in Italy with Andrea and me, is a deep thinker with profound insight, and as I look to joining him on the East Coast during my next phase of life, I anticipate many more camping, backpacking, and traveling experiences with him. Finally, Craig Teuscher has become a close friend that I deeply respect for his technical depth, life balance, and integrity; our discussions about everything from communications theory to fatherhood to faith have enriched my view on how the pieces of life can be integrated.

The encouragement from my family was an essential ingredient. From the earliest time I can remember, my mother built in me the confidence that I could achieve whatever I set out to do, along with the tenacity and perseverance to endure difficulties and challenges. My grandparents, who provided both moral and financial support throughout my formative years, reinforced these character qualities. My brother has been a patient listener during difficult times and has been a constant source of encouragement. And, since I have been married, Tom and Marge Hoover have been second parents to me; their support, affirmation, and encouragement have been invaluable.

I cannot say enough about the role that Andrea, my wife, has played during the past six years. During the first three years, before we were married, she was an incredibly fun antidote to the discipline that coursework demands. The ski trips, barbecues on the deck of the Thornhill house, trips to the Berkeley Bowl, road trips to Ashland or Santa Barbara or Redding, hosteling through the Canadian Rockies, or hanging out at the Montell house with Lori are what I remember most about my bachelor days at Berkeley. Since we have been married, her perseverance at Chevron has enabled us to do things that a graduate student stipend simply will not allow. From managing the Recovery One project, to driving a car without air conditioning in the 100-plus degree afternoons coming from Concord, to dealing with irate customers on the Chevron Travel Club's customer service line, the

sacrifices that she made greatly eased the growing pains that I was experiencing as I finished grad school and wrote my dissertation. As we look forward to the next phase in life, my hope is to repay the debt of gratitude by enabling her to pursue her vision and dreams for her "life after Chevron."

Finally, I owe Bob Brodersen, my advisor, an enormous thank-you for investing time, energy, and an incredible amount of money in my ideas. Through the 8 years I have known him, he has seen me mature into adulthood, and guided my transformation into an independent researcher. The many days he spends on the road marketing ideas, raising support, and gathering feedback have provided an exciting, wonderful environment in which to explore new ideas. His advice has helped steer me onto a path that I am confident will provide an endless supply of interesting, relevant problems to work on throughout my career.

## Chapter 1

# Introduction

### 1.1 Overview

Data communications protocols govern the way in which electronic systems exchange information by specifying a set of rules that, when followed, provide a consistent, repeatable, and well-understood data transfer service. In designing communication protocols and the systems that implement them, one would like to ensure that the protocol is correct and efficient. *Correctness* means that the rules of exchange are internally consistent and unambiguously handle all possible events. Informally, we wish to know that the protocol is free from unwanted behavior, such as deadlock, and that it can indefinitely provide data transfer service under any input sequence. These correctness properties are only part of the design problem: it is equally important to guarantee that the protocol is efficient.

Efficiency, used here to indicate how well a given protocol performs relative to an implementation with unconstrained complexity, is a much more difficult property to quantify. The measures of efficiency are largely dependent upon the context in which the protocol is to be used and upon the services that the protocol is supposed to provide. Throughput, delay, channel utilization, spectral efficiency, and end-to-end distortion are but a few of the measures commonly used to compare alternatives in protocol design. The underlying question is "all constraints considered, is there a better approach that provides the same service?"

In practice, most new protocol designs are approached in an ad-hoc fashion that relies heavily on simulation to answer both the question of correctness and efficiency. Formal approaches such as formal specification and formal verification are usually relegated to the domain of theorists. This thesis, in contrast, addresses the problem of integrating formal methods within a comprehensive design flow.

The context for the protocol design methodology is link-level communication protocols for wireless networks that provide multimedia services to mobile users, such as the one described in example system of Chapter 2. (In particular, infrastructure-based networks that support mobile clients are considered; challenges specific to peer-to-peer communication between mobile hosts are not addressed). Portable devices, in this context, have severe constraints on the size, the power consumption, and the communications bandwidth available, and are required to handle many classes of data transfer service over a limited-bandwidth wireless connection, including delay sensitive, real-time traffic such as speech and video. This combination of limited bandwidth, high error rates, and delay-sensitive data requires tight integration of all subsystems in the device, including aggressive optimization of the communication protocols to suit the intended application. The protocols must be robust in the presence of errors; they must be able to differentiate between classes of data, giving each class the exact service it requires;

2

and they must have an implementation suitable for low-power portable electronic devices.

There are at least four aspects of this protocol design problem that make it both challenging and interesting. The first is common to all protocol designs: because designing a protocol involves reasoning about a distributed system, the designer must be able to conceptualize and model the interaction between independent actors. Within the context of infrastructure-based mobile networking the problems are particularly challenging because despite the best intentions of the actors, it cannot be assumed that the physical link even exists! Obviously, design language and modeling tools must handle concurrency, asynchrony, and interprocess communication, yet the breadth of ongoing work on concurrent systems attests to the challenges that remain to be solved to find the "right" language for protocol design.

The second aspect is the particular class of protocols: *data link* protocols. Data link protocols are usually divided into two main functional components, the *logical link control* (LLC) and the *media access control* (MAC), that are responsible for providing (1) a point-to-point packet transfer service to the network, and (2) a means by which multiple users can share the same physical transmission medium. Since it must interact both with network-level services and the physical transmission medium, the data link protocol spans several levels of service abstraction and several orders of magnitude in time granularity. This complicates modeling, simulation, and formal analysis because no single design language is capable of time. Synchronous languages, such as Esterel and SMV, are appropriate for designing and verifying implementation-level state machines, but are not able to

model distributed systems that exchange messages asynchronously. Formal description languages like SDL solve the problem of distributed, asynchronous systems, but are inadequate for use in describing detailed behavior of synchronous circuits that are typical in modem interface hardware.

The third design challenge is the difficulty of obtaining performance estimates for media access and physical layer protocols for wireless networks. Because the users are mobile and the communications channel is highly time-varying, estimates of error rates and coding performance are largely dependent upon the traffic patterns of other users, the modulation scheme used, and the extent to which the channel changes with time. Developing realistic statistical models for traffic patterns, channel noise and interference, and for the time-varying wireless channel are essential to the design of good protocols. Obtaining experimental data that gives the designer insight about the time-varying statistics of the wireless channel is still a subject of active research. One approach to using experimental data to characterize the time statistics of an indoor wireless link is presented in Appendix A.

The fourth aspect is the design context itself: the combination of wireless communications and portable devices. Taken in isolation, each of these presents a rich basis for new approaches to solving mature problems. Taken together, they offer the chance to completely rethink classical approaches to communication, networking, computing, and system design. It is this aspect which provides the greatest opportunity for technical contributions because designs must be approached with a holistic view, rather than by composition of individually optimized subsystems.

4

Data communications networks have historically been limited to fixed-wire networks: wireless media was utilized in very specialized applications, such as military tactical networks or communication with satellites, with few real-time applications. Most protocol design methodologies implicitly assume an environment that is static, and thus radically different than wireless. It is only in the last decade that wireless communications has completely pervaded modern life, and in doing so has made relevant the question of a design methodology that considers the particular problems and opportunities that are present in this context.

The primary goal of this thesis is to identify how the demanding requirements for high-bandwidth, low-latency wireless communication for portable devices requires a complete rethinking of the methodology for designing these systems; the methodology presents one approach to integrating specification, formal verification, performance simulations, and a path to implementation.

## 1.2 Dimensions of the Problem Space: Specification, Verification, Performance Estimation, and Implementation

As described above, the focus of this dissertation is on simplifying the protocol design problem, which has four key elements: specification, verification, performance estimation, and finally, implementation. Historically, these dimensions have largely been separated. To give the reader a view of what lies ahead, the approach taken here begins with the assumption that performance estimation and protocol verification are equally important problems that must be addressed at some point before implementation. Thus, what is needed is

- A language that is formal, yet has the capability to both abstract and to refine, as needed, throughout the design process. The language must provide a means of expressing performance constraints.

- A set of tools that facilitate design exploration and evaluating performance

- Clear understanding of the relationships of key parameters in the protocol design, and the relationships to the network layer and physical layer characteristics

- A means of separating simulation models while still capturing essential interdependencies for example, simulating both the backbone network (packet-level abstraction) and the signal-space modulation details is prohibitively expensive and provides little intuition about the way the system should be designed. Instead, one would like to abstract where possible without losing essential performance information.

Thus, what is needed is a methodology that addresses the exploration phase, the "standardization" phase<sup>1</sup>, and the implementation phase.

### 1.2.1 The specification problem

As a starting point, we take the well-known fact that protocols of any significance are notoriously difficult to design. First, there is the problem of saying what the protocol does and, without constraining the implementation, detailing the services that it provides. The services, legal sequences of message exchanges, and the behavior under all exceptional conditions must be defined in such a way that there can be no semantic ambiguity. This is the *specification* problem.

To have any hope of applying automated methods of formal verification to the problem, the protocol must itself be described in a language that has well-defined semantics and an underlying mathematical model of the system being represented. Chapter 3 explores the existing formal languages used to describe protocols and compares their models of computation, concurrency, communication, and other features that either aid or hinder the integration of performance metrics.

#### **1.2.2 The verification problem**

The *verification* problem deals with the issue of proving correctness properties about a system. These properties usually fall into two broad classes: *safety*, or "invariance", properties and *liveness*, or "eventually", properties [OL82, Pnu85, Eme90]. Intuitively, a safety property asserts that "nothing bad happens," while liveness properties state that "something good eventually happens." Though it will be explored in detail in later sections, it is introduced here with the observation that formal verification is perhaps the most challenging and least-understood technologies available to system designers.

The challenge for a designer lies in the fact that formally proving anything about a system requires a precise mathematical model of the system. Further, for practical systems, proving the safety and liveness properties is computationally intractable without abstracting away all but the most relevant detail needed to prove that the properties hold, and in practice is more an art than a science. The art of abstraction requires a deep understanding of the protocol as well as knowledge of how the representation of a system impacts the capability to prove properties about it.

$<sup>^{\</sup>rm 1}$  By standardization, we mean the protocol must be described in an implementation-independent, unambiguous way.

Fortunately protocol systems can be modeled as finite automata, giving us a starting point for the mathematical model. But reducing the size of the model to a point where an automated formal verification system becomes useful requires a deep understanding of operation of the system and the subtle relationships between each subsystem. This step is still the limiting factor that impedes the application of formal verification.

### 1.2.3 "Correctness" and performance

Two other critical points about formal verification techniques are that 1) they are capable of working with the *possible* states that a system might be in rather than the *probability* of being in a given state, and 2) time is abstracted to the point that it is only possible to distinguish between orderings of events. Thus, proving correctness is limited to proving properties that are concerned with the ordering of two events, rather than the absolute interval that separates them. Thus it is possible to say that the event *b* follows the event *a* or occurs simultaneously with event *a*. This is a critical point because the third dimension of interest, *performance modeling*, is particularly interested in the times and probabilities. The "correctness" of a protocol, for many applications, cannot be expressed solely in terms of safety and liveness properties. Determining that a given protocol system meets a throughput requirement can be as important as answering the question of formal correctness.

For example, formal verification can determine that it is possible for a buffer to overflow, but provides no information about how likely that event is. In practice one would like to optimize for the common case – sizing buffers to handle typical occupancies without overflow – while being able to recover from the corner cases (buffer overflow). As another example, throughput and delay estimates are typically based on statistical models of the communications channels, the number of users, and the traffic patterns for each user. The most natural simulation domain for modeling these phenomena is using discrete event simulation systems that provide essentially unrestricted input specifications (e.g., Ptolemy, VHDL, and Bones). Discrete event systems are in general not finite-state [ELLS97] and hence are incompatible with formal verification. Thus, although answering the questions is a crucial part of showing that a protocol is "correct," the design is approached from two fundamentally different paradigms. Both seek to answer the question that must precede implementation efforts – namely, "does the protocol provide, in a fundamental way, the desired behavior?"

#### **1.2.4 Relating abstract models to implementa tion**

Finally, the *implementation* domain of the protocol also has a significant ability to impede an integrated design approach, especially when the implementation contains a mix of hardware and software. The media access control layer, in particular, is closely tied to the underlying physical layer and control logic must respond to events at the microsecond level; for power efficiency, it is most efficient to implement this control logic in hardware. Product differentiation, firmware upgrades, and the flexibility of a software-based approach, on the other hand, pull towards implementing as much as possible in software. In practice, the final implementation is a mix of hardware and software.

The problem of designing these hybrid systems and obtaining meaningful performance estimates is an area of active research known as "co-design" (see [ELLS97] and the references cited therein). At the heart of the issue is that

hardware and software naturally have two very different types of concurrency – interleaved and true parallel – and so design styles, representations, and simulation semantics are extremely domain-specific. We will explore these issues further in Chapter 3.

Summarizing, we are presented with conflicting objectives in our specification languages, in our ways of checking "correctness", and it becomes difficult to relate these various conceptual models to the domain of our implementation. For a pure specification, such as a standards body might produce, all detail must be included in the model. For performance modeling, we would like the capability to model many users, to quantify throughput, delay, and buffer occupancy, etc. – we need to have a higher-level statistical model of the system with both time and probabilistic metrics. For verification, we would like to compact, abstract, and remove as much detail as possible without changing the protocol. It is not surprising that the languages used to describe a particular model are strongly influenced by whether the model is to be used for specification, for formal verification, for performance modeling, or for the actual implementation.

Before proceeding, it is beneficial to take a brief look at the history of protocol design, protocol specification, and the various technical tools that have been used to verify correctness and estimate performance.

### 1.3 Abstract Services and the OSI Protocol "Stack"

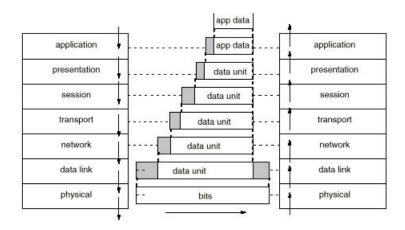

Because it is the most common decomposition of protocol services, a good starting point for discussing communication protocols is the Open Systems Interconnection (OSI) "protocol stack" [DZ83]. In the OSI model, protocols are conceptually organized as a series of layers, each one built upon its predecessor. Each layer offers a set of services to the higher layers, hiding the details of how the services are implemented. The goal is to present the illusion to layer n on host A that the message exchange takes place atomically via layer n-1 to a layer n peer on host B, as shown in Figure 1– 1. In reality, each layer passes data and control information the layer immediately below it, until the lowest (physical) layer is reached. The function of each layer is outlined in Table 1– 1.

Figure 1—1. OSI Protocol Layers

Two dimensions of abstraction are present in this model: *service* abstraction and *inter-layer communication* abstraction. Between each pair of adjacent layers there is an interface that defines the primitive operations and services provided by the lower layer. Usually, a foremost objective is to specify the set of services that each layer offers, while abstracting the details of how these services are provided. Implicitly with this objective is the desire to limit dependencies between each layer to a set of interface primitives known as *service access points* (SAPs).

The rationale behind this objective is that it makes it possible, in principle, to replace the implementation of a particular layer with another implementation, requiring only that each implementation provide a consistent interface that offers the same services and service access points to the upper layer. Thus, the goal of service abstraction is modularity and freedom to choose the implementation that is best suited for a particular environment. Detail about inter-layer communication, on the other hand, is usually considered to be a concern that is orthogonal to the design of the protocol.

| Layer<br>Number | Layer Name   |                                               | Layer Function                                                                                                                                                                                                                                                      |

|-----------------|--------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | Application  |                                               | User functions. For example, file transfer, database query.                                                                                                                                                                                                         |

| 6               | Presentation |                                               | Data representation and translation.                                                                                                                                                                                                                                |

| 5               | Sessio       | on                                            | Conversation initiation, coordination, and<br>breakdown. A session protocol controls which peer<br>can transmit, provides services to synchronize the<br>queue between peers, and defines how Protocol<br>Data Units (PDUs) are related for error recovery.         |

| 4               | Transport    |                                               | Reliable end-to-end data delivery between peers.<br>Depending on the quality of service offered by the<br>network layer, transport usually performs error<br>correction and flow control.                                                                           |

| 3               | Network      |                                               | Handles routing between peers, global naming and addressing, fragmentation and re-assembly.                                                                                                                                                                         |

| 2               | Data<br>Link | Logical<br>link<br>control<br>(LLC)<br>Medium | For point-to-point connections, handles framing,<br>station addressing, error control and flow control.<br>For networks where transmitting stations share a<br>common medium, the protocol governing access to<br>the medium is separated into a sub-layer referred |

|                 |              | Access<br>Control<br>(MAC)                    | to in the IEEE standards as the media access<br>control (MAC) layer.                                                                                                                                                                                                |

| 1               | Physical     |                                               | Electrical and mechanical attributes governing connection to the communication medium.                                                                                                                                                                              |

While this model provides an excellent starting point for conceptually partitioning a set of protocol services, it must be used with care. This model has two implicit assumptions that fail to hold in many practical contexts. First, there is the assumption that cost of abstraction and separation is negligible compared to advantage of being able to interchange layers. Second, there is an assumption that interchanging layers that provide the same logical services – for example, a wired physical layer and a wireless physical layer – provide equivalent service.

Since in wired networks the point-to-point network topology is essentially static, physical-layer channels can be modeled as time-invariant systems and user-to-user interference can be modeled as a stationary random process. Both of these properties provide simple, understandable statistical models for characterizing the probability of errors, justifying abstractions that allow the services provided to be partitioned into orthogonal concerns. For example, a networked file system provides the abstraction that all files reside on a single logical file system, greatly simplifying the design of an application that read and write files using a standard file I/O interface. In turn, the networked file system is simplified if it can assume a black box, reliable packet delivery service from the lower-level network services.

The difficulty in applying this layering approach lies *not* in defining clean service access points and abstracting lower level functionality; the real difficulty is in separating the *semantics* of the service primitives. This is a subtle point, and one worth further discussion.

The specification for the widely used ARPA Transmission Control Protocol (TCP), for example, contains no explicit reference to a physical media or to any particular style of implementation. Instead, it is assumed that the implementation has a means of providing a best-effort datagram transfer service between endpoints, and the TCP specification focuses solely upon higher level issues such as setting up a connection, maintaining order, and so on. Informally, the SAPs to the lower levels are primitives to send and receive datagrams. TCP maintains its own timer for datagrams that still require an acknowledgement, and since corrupted packets received by lower layers are discarded, TCP has no way of distinguishing between a packet corrupted by bit errors from packets that are lost due to congestion in the network.

TCP has been successfully used with a variety of lower-level media access protocols such as carrier-sense multiple access (CSMA) and token ring, and on a variety of physical media, including wireless, optical fiber, and wired media. Although the TCP specification makes no explicit reference to the characteristics of the lower layers, implicitly in the timeout and retransmission mechanisms there are the assumption that the error rate is low, and that lost packets occur due to network congestion. Accordingly, lost packets trigger a congestion-avoidance mechanism in TCP that reduces the rate at which packets are sent. Thus when TCP is used over a wireless link, a slight change in the packet error rate can mean that the performance drops drastically due to the compounded effect of lost packets and a rate reduction by the sender. An aggregate throughput of 25% of the link capacity is typical of TCP over wireless [BPSK97].

The problem here arises due to misinterpreting the semantics of the event "lost packet." The appropriate behavior for the protocol depends strongly on the semantics of this event, and misinterpretation leads to behavior that, although it does not violate any safety or liveness properties, severely limits the usefulness of the protocol.

# 1.4 An approach to integrating protocol design disciplines

This above example attests to the need to tailor protocols to the environment they operate in, and is the strongest argument for a design methodology that integrates performance metrics with functional correctness. Separating the design of the protocol from the context in which it exists leads to performance penalties that are unacceptable for wireless, portable applications. The remainder of this dissertation explores the relationships between *specification, verification, performance estimation,* and *implementation.* The summary of this exploration is presented here as a guide for the reader.

The formal methods community has long advocated a methodology that begins with an abstract, formal description of the system functionality that is supposed to be the basis for rigorous formal verification and architectural exploration. Conceptually, this provides the designer with an implementation-independent way of evaluating a protocol or an algorithm. Further, this methodology proposes that the designer refine this abstract description by successively adding implementation details, proving at each step that the refinement is consistent with the original specification.

In practice few if any formal methods are employed in the design community. Informal text documents usually specify the system requirements, and the typical design flow starts with simulation models based on these informal descriptions. Simulation is then used to drive the bulk of the algorithmic exploration, and the results of these simulations are used to elaborate and fine-tune the original design. Typically, it is only after a prototype of the system has been built and checked via black-box conformance testing [Hol92] that the system is checked against the standard.

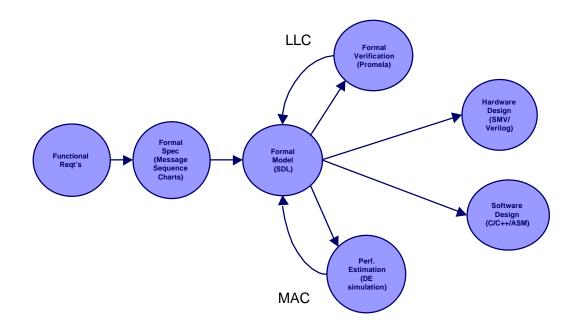

Figure 1—2. Mixed Formal/Informal design flow for data link protocols

The premise of this thesis is that a mix of informal and formal specifications and models are needed in order to facilitate the design of robust protocols that have reasonable performance. However, it is essential to understand where each is most appropriate in the design flow as well as the relationships between formal and informal models. With this in mind, we recommend the following methodology:

Develop a set of functional requirements that specify the services that a protocol is required to provide, along with performance considerations. For example, a data link protocol for mobile applications must support roaming, thus part of the functional requirement is "support for mobility".

- 2) Develop an *informal*, coarse-grained architectural definition of the system that identifies a set of message passing entities (*e.g.*, mobile devices and basestations), along with a (perhaps incomplete) set of message exchange sequences for each protocol function. Performance considerations, along with details about computation, data structures, etc., are omitted. The primary purpose of this phase is to focus on the exchange sequences that comprise the protocol, without regard to implementation, in typical scenarios. Message sequence charts (MSCs) are one semi-formal approach that is provides a means to graphically depict the actors, the state of each actor as time progresses, and their possible interactions. In addition, this specification can be used later during verification to check the trace-equivalence of the implementation at the message passing and state transition level.