# Memory Dependence Prediction

by

Andreas Ioannis Moshovos

A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

# UNIVERSITY OF WISCONSIN—MADISON

1998

# Abstract

As the existing techniques that empower the modern high-performance processors are being refined and as the underlying technology trade-offs change, new bottlenecks are exposed and new challenges are raised. This thesis introduces a new tool, *Memory Dependence Prediction* that can be useful in combating these bottlenecks and meeting the new challenges. Memory dependence prediction is a technique to guess whether a load or a store will experience a dependence. Memory dependence prediction exploits regularity in the memory dependence stream of ordinary programs, a phenomenon which is also identified in this thesis. To demonstrate the utility of memory dependence prediction this thesis also presents the following three novel microarchitectural techniques:

- 1. Dynamic Speculation/Synchronization of Memory Dependences: this thesis demonstrates that to exploit parallelism over larger regions of code waiting to *determine* the dependences a load has is not the best performing option. Higher performance is possible if memory dependence speculation is used especially if memory dependence prediction is used to guide this speculation.

- 2. Speculative Memory Cloaking and Bypassing: this thesis approaches memory as either an *inter-operation communication* or as a *data-sharing* mechanism. In the first case, memory is used to communicate values among instructions. In the second case, memory is used to hold values that are read repeatedly. Memory dependence prediction can be used to explicitly express either action so that loads can obtain a speculative value long before they can even access memory. Moreover, this thesis presents a technique to further reduce memory latency by linking directly the actual producer of a value with the actual consumers, taking loads and stores off the access path.

- 3. *Transient Value Cache (TVC):* Supporting highly-parallel execution requires the ability to perform multiple, simultaneous memory accesses. The TVC uses a small data cache to provide this support for a large fraction of loads while avoiding an increase in the latency of all other loads. This is achieved by using memory dependence prediction to selectively place the small data cache either inseries or in-parallel to the L1 cache.

# Acknowledgments

Vasiliki has been a constant source of support, advice, devotion and above all optimism for as long as we have known each other. I am grateful for her patience and willingness to make sacrifices just so that I can continue working towards my doctorate. I am also grateful to her mother Naysika and her sister Dora for their love, support and forbearance. My parents, Koula and Yannis, and my brother Nikos have always been there for me providing encouragement and unconditional support. They made everything in their power to provide me with the best education, even if that meant we had to be separated. I only wish that my grandparents, Elpida and Andreas, who in many ways made me who I am, were still with us.

I want to express my appreciation to my advisor, Guri Sohi, for taking me as his student and for his support throughout my doctorate studies. He heavily influenced my way of thinking about technical issues and ideas. Above all, I am most grateful for that he forced me to develop my own ideas and learn how to best defend them. It has been a privilege working with him.

Over the past five and a half years I had the privilege of interacting with Jim Goodman, Mark Hill, Jim Smith and David Wood. Most if not all I know about Computer Architecture I learned from them and Guri. I am also grateful to all of them for serving in my committee. Mark Hill and Jim Smith also served in my prelim committee, while David Wood and Jim Smith had the dreadful task of reading this thesis. David's, Guri's and Jim's efforts made this thesis more readable and accurate. Jim Smith made life occasionally more tasteful with his paella. I am also grateful to Manolis Katevenis who introduced me to Computer Architecture and taught me how to make presentations.

My thanks to the members of the Multiscalar and Kestrel research groups, both past and present. Scott Breach and T. N. Vijaykumar have been close collaborators in the dependence speculation and synchronization work, and sounding boards for new ideas. I am grateful to Scott for writing the first simulation model for the memory dependence synchronization mechanism and for suggesting the merged MDST/MDPT organization. Amir Roth has been a collaborator in recent work on prefetching and control flow prediction. It has been a pleasure working with them. My thanks to Sridhar Gopal, Andy Glew, Avinash Sodani, Craig Zilles, Todd Austin, Steve Bennett, Harit Modi, Eric Rotenberg, Yannos Sazeides, Quinn Jacobson, Subramanya Sastry and Timothy Heil for the numerous discussions. My thanks to Doug Burger, Babak Falsafi, Alain Kagi and Subbarao Palacharla for many discussions about technical and not so technical issues. I most grateful to both Babak and Vijay for they were always willing to talk and offer advice. Babak also taught me how to say the most important things in Farsi. I am certainly going to miss the basketball games with Babak, Alain, Tia Newhall and Steve Seitz.

My stay in Madison was made more enjoyable and interesting by new friends: Dionisios Pnevmatikatos and Natalia Francis, Minos Garofalakis, Yannis Ioannidis, Yannis Schoinas and Leah Parks, Yannis Christou, Kyriakos and Sarah Kutulakos, Anastasia Ailamaki, Dimitris Komilis, Stefanos Kaxiras, Aggeliki Baltoyianni, Isidoros Sarinopoulos, Eirini Xagoraraki, Leonidas Galanis and Alkis Polyzotis.

Many thanks to Lorene Webber and to Debra Diewald. They have been always willing to help no matter how hectic their day was.

# Contents

| Abstract                                                            |

|---------------------------------------------------------------------|

| Acknowledgments                                                     |

| Chapter 1. Introduction                                             |

| 1.1 Contributions                                                   |

| 1.1.1 Memory Dependence Locality and Prediction                     |

| 1.1.2 Dynamic Speculation and Synchronization of Memory Dependences |

| 1.1.3 Speculative Memory Cloaking and Bypassing                     |

| 1.1.4    Transient Value Cache    7                                 |

| 1.2 Thesis Organization                                             |

| 1.3 Experimental Framework                                          |

| 1.3.1 Programs and Compiler Infrastructure                          |

| 1.3.2 Simulation Methodology                                        |

| Chapter 2. Memory Dependence Behavior Analysis                      |

| 2.1 Memory Dependence Types                                         |

| 2.2 A Class of History-Based Memory Dependence Predictors           |

| 2.3 Memory Dependence Behavior Analysis                             |

| 2.3.1 Metrics and Justification                                     |

| 2.3.2 Memory Dependence Characterization                            |

| 2.3.2.1 Address Space Distribution of Memory Dependences            |

| 2.3.2.2 Dynamic Instruction Distance Distribution                   |

|     | iv                                             | V |

|-----|------------------------------------------------|---|

|     | 2.3.3 Memory Dependence Shape Characterization | 3 |

|     | 2.3.3.1 Instance Dependence Set Size           | 9 |

|     | 2.3.3.2 Aggregate Dependence Set Size          | 1 |

|     | 2.3.4 Working Set of Memory Dependences        | 1 |

|     | 2.3.5 Capturing Memory Dependence Activity     | 3 |

|     | 2.3.6 Memory Dependence Status Locality        | 5 |

|     | 2.3.7 Memory Dependence Locality               | 7 |

|     | 2.3.7.1 Read-after-Write Dependences           | 9 |

|     | 2.3.7.2 Read-after-Read Dependences 40         | ) |

| 2.4 | Summary                                        | 2 |

| Chapter 3. | Dynamic | Memory | Dependence |

|------------|---------|--------|------------|

|------------|---------|--------|------------|

| Speculati | on and Synchronization                                                 |

|-----------|------------------------------------------------------------------------|

| 3.1       | Using Load/Store Parallelism To Improve Performance                    |

| 3.2       | Memory Dependence Speculation                                          |

| 3.3       | Memory Dependence Speculation Policies                                 |

| 3.4       | Mimicking Ideal Memory Dependence Speculation                          |

| 3.5       | Implementation Aspects                                                 |

| 3         | 3.5.1    Working Example    54                                         |

| 3.6       | Issues                                                                 |

| 3         | 3.6.1    The Multiscalar Execution Model    56                         |

| 3         | 3.6.2 Incorporating Speculation/Synchronization into a Pipeline        |

| 3         | 3.6.3 Incomplete Synchronization    58                                 |

| 3         | 3.6.4 Intelligent Prediction    58                                     |

| 3         | 3.6.5 Control Mispeculations                                           |

| 3         | B.6.6         Multiple Dependences Per Static Load or Store         59 |

|        |        | v                                                                |

|--------|--------|------------------------------------------------------------------|

|        | 3.6.7  | Centralized Versus Distributed Structures                        |

| 3.7    | Relat  | ed Work                                                          |

| 3.8    | Evalu  | action - Distributed, Spit-Window Processor Model                |

|        | 3.8.1  | Performance Potential of Load/Store Parallelism                  |

|        | 3.8.2  | Naive Memory Dependence Speculation                              |

|        | 3.8.3  | Using Store Address Information To Improve Speculation Accuracy  |

|        | 3.8.4  | Selective Memory Dependence Speculation                          |

|        | 3.8.5  | Speculation/Synchronization - Centralized Mechanism              |

|        | 3.8.6  | Speculation/Synchronization - Distributed Mechanisms             |

|        | 3.8.7  | Comparison of Speculation/Synchronization Mechanism              |

| 3.9    | Evalu  | uation - Centralized, Continuous -Window Processor Model         |

|        | 3.9.1  | Performance Potential of Load/Store Parallelism                  |

|        | 3.9.2  | Performance with Naive Memory Dependence Speculation             |

|        | 3.9.3  | Using Address-Based Scheduling to Extract Load/Store Parallelism |

|        | 3.9.4  | Speculation/Synchronization                                      |

| 3.10   | ) Cha  | pter Summary                                                     |

|        |        |                                                                  |

| Chapte | r 4. S | peculative Memory Cloaking and Bypassing                         |

| 4.1    | Two    | Common Uses of Memory                                            |

|        | 4.1.1  | Memory as an Inter-operation Communication Agent                 |

|        | 4.1.2  | Memory As A Value Place Holder                                   |

|        | 4.1.3  | Using Memory Dependence Prediction To Streamline Memory Accesses |

| 4.2    | Speci  | ulative Memory Cloaking                                          |

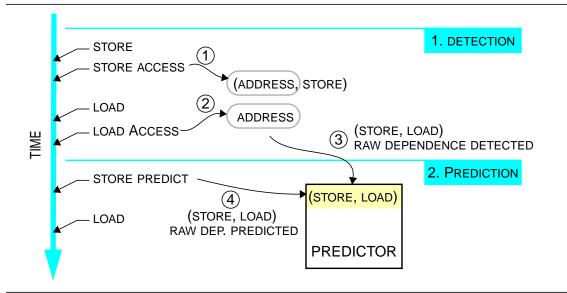

|        | 4.2.1  | Detection and Prediction of Dependences                          |

|        | 4.2.2  | Synonym Generation and Communication                             |

|        | 4.2.3  | Verification                                                     |

|     |       |         | vi                                                            |

|-----|-------|---------|---------------------------------------------------------------|

|     | 4.2.4 | Imple   | ementation Aspects                                            |

| 4.3 | Spec  | ulative | Memory Bypassing 101                                          |

| 4.4 | Exter | nding ( | Cloaking and Bypassing to Support Data-Sharing 103            |

| 4.5 | Relat | ted Wo  | ork                                                           |

|     | 4.5.1 | Regi    | ster Allocation Alternatives                                  |

|     | 4.5.2 | Addr    | ess Prediction Based Techniques 104                           |

|     | 4.5.3 | Valu    | e Prediction                                                  |

|     | 4.5.4 | Tech    | niques Similar to Cloaking or Bypassing 105                   |

| 4.6 | Evalu | uation  |                                                               |

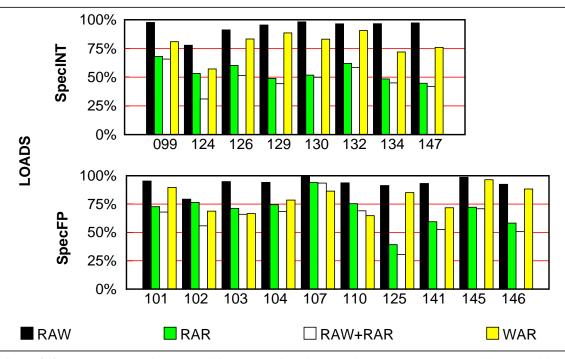

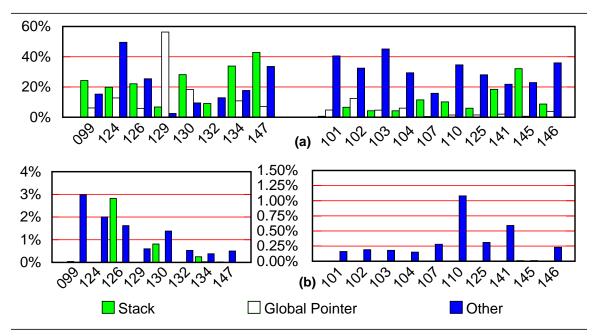

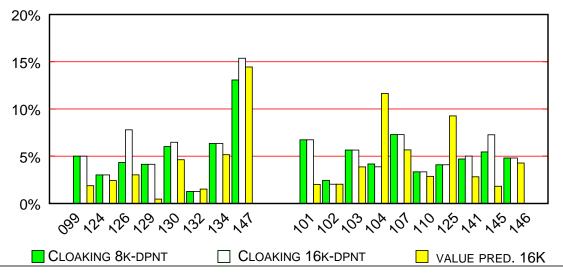

|     | 4.6.1 | Mem     | ory Dependence Detection                                      |

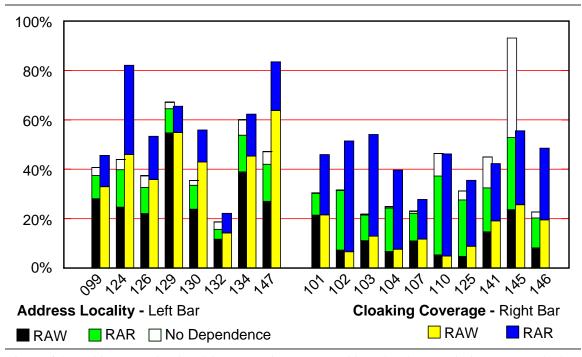

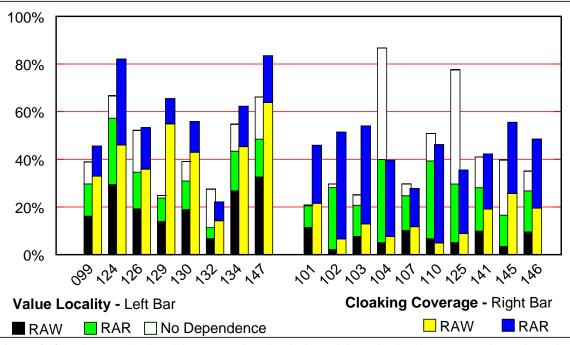

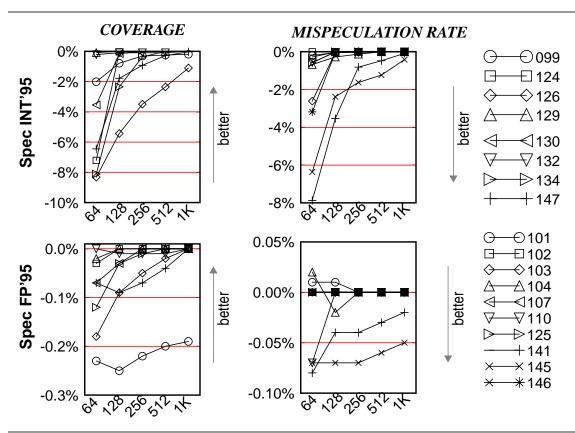

|     | 4.6.2 | Cloal   | king Coverage And Mispeculation Rates 109                     |

|     | 4.6.3 | Using   | g Adaptive Predictors to Improve Cloaking Accuracy            |

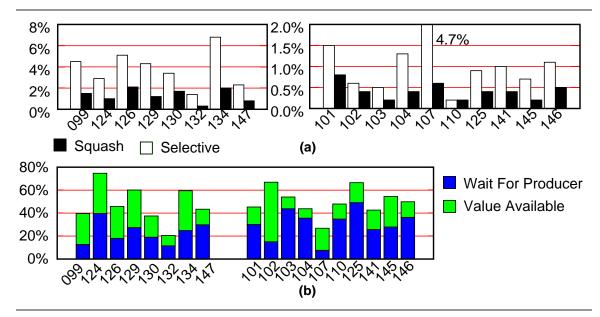

|     | 4.6.4 | Char    | acteristics of the Memory Values that are Handled by Cloaking |

|     | 4.    | .6.4.1  | Address Space Breakdown 117                                   |

|     | 4.    | .6.4.2  | Base Register Breakdown                                       |

|     | 4.    | .6.4.3  | Address Locality Measurements                                 |

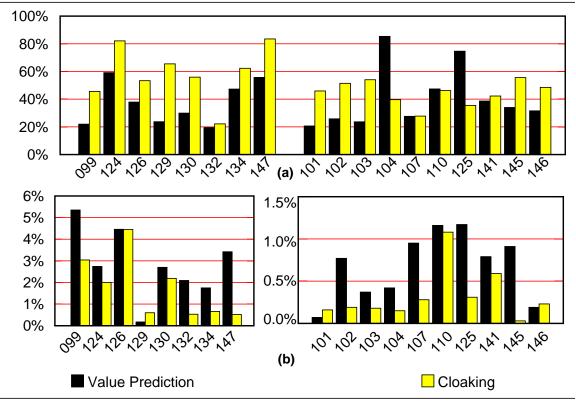

|     | 4.    | .6.4.4  | Value Locality and Value Prediction Measurements              |

|     | 4.    | .6.4.5  | Dynamic Instruction Distance Distribution                     |

|     | 4.    | .6.4.6  | Input Data Set Sensitivity Analysis 123                       |

|     | 4.6.5 | Effec   | ts of Finite Prediction Structures                            |

|     | 4.    | .6.5.1  | Sensitivity to the Number of DPNT Entries                     |

|     | 4.    | .6.5.2  | Sensitivity to the Associativity of the DPNT                  |

|     | 4.    | .6.5.3  | Synonym File Size Sensitivity Analysis 126                    |

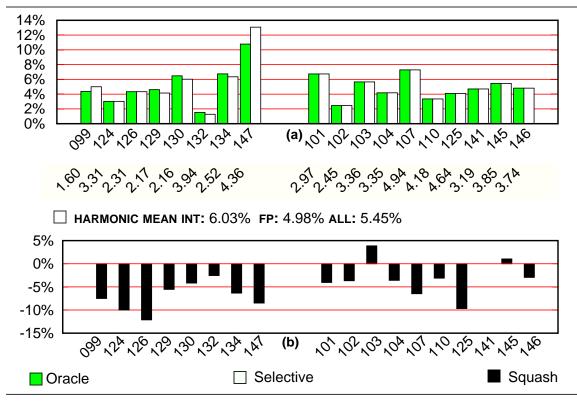

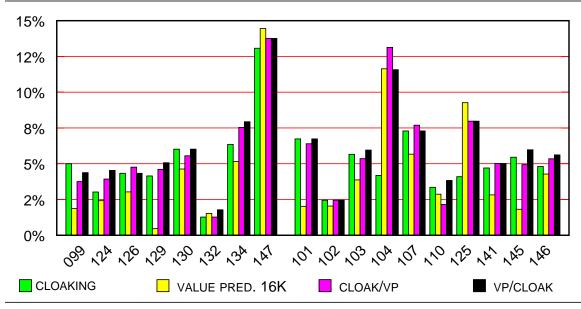

|     | 4.6.6 | Perfo   | ormance Impact                                                |

|     | 4.    | .6.6.1  | Configuration Parameters                                      |

|     | 4.    | .6.6.2  | Performance with a Cloaking/Bypassing Mechanism               |

| vii                                                                     |

|-------------------------------------------------------------------------|

| 4.6.6.3 Comparing Cloaking/Bypassing and Value Prediction               |

| 4.6.6.4 Combining Cloaking/Bypassing and Value Prediction               |

| 4.7 Summary                                                             |

| Chapter 5. Transient Value Cache                                        |

| 5.1 Short-Distance Memory Dependence Measurements                       |

| 5.2 The Transient Value Cache                                           |

| 5.3 Related Work                                                        |

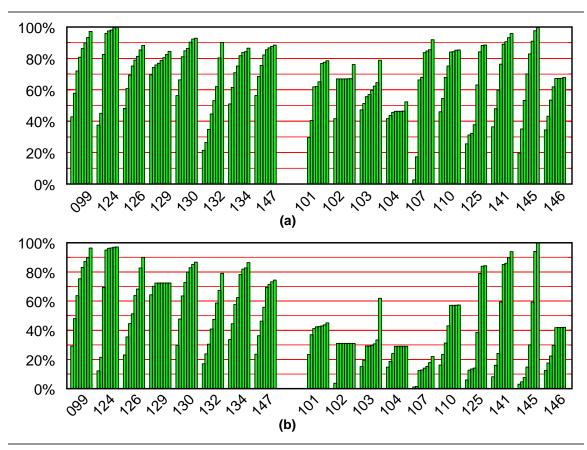

| 5.4 Evaluation                                                          |

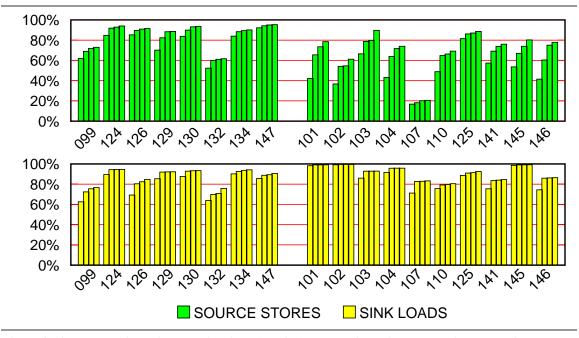

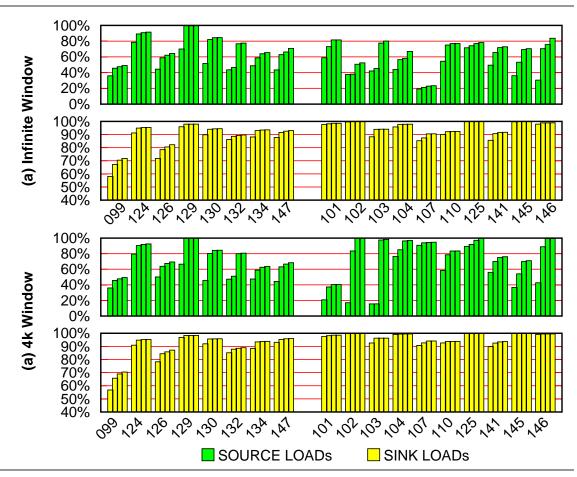

| 5.4.1 Load Dependence Status Prediction Accuracy                        |

| 5.4.1.1 Effects of Associativity on Prediction Accuracy                 |

| 5.4.1.2 Effects of Block Size on Prediction Accuracy                    |

| 5.4.2 Store Dependence Status Prediction Accuracy 149                   |

| 5.5 Summary                                                             |

| Chapter 6. Conclusion                                                   |

| 6.1 Summary 153                                                         |

| 6.1.1 Dynamic Speculation and Synchronization of Memory Dependences 154 |

| 6.1.2 Speculative Memory Cloaking and Bypassing 155                     |

| 6.1.3 Transient Value Cache 156                                         |

| 6.2 Future Directions                                                   |

| 6.2.1 Correlating Memory Dependence Behavior                            |

| with Program Elements and Data Structures 157                           |

| 6.2.2 Interaction with the Compiler 157                                 |

| 6.2.3 Memory Communication and Sharing in Distributed Environments      |

|              | viii                                                               |

|--------------|--------------------------------------------------------------------|

| 6.2.4        | Support for Selective Invalidation and Data Speculation Resolution |

| 6.2.5        | Operation Prediction                                               |

| Bibliography |                                                                    |

# **Chapter 1**

# Introduction

Program execution may initially seem as an inherently sequential process where the following steps are to be performed repeatedly, one after the other: (1) fetch an instruction, (2) read a set of input data, perform a calculation, if necessary (3) store the results for future reference, and finally, (4) decide which instruction to fetch next. From this perspective, it would seem that our only hope for faster processing would be to simply rely on advances in the underlying semiconductor device technologies; faster circuits may make performing each of the steps faster, and as result they reduce the time required to execute a whole program. Modern high-performance computing systems however, employ techniques that allow them to be quite a bit smarter about program execution in effect making better use of what solid-state technology has to offer at any given point of time. A plethora of techniques that empower these computing systems rely on empirical observations about program behavior to be effective. The motivation underlying these techniques is that programs, for the most part, do not behave randomly. Rather, they exhibit several idiosyncrasies, or in other words, they tend to exhibit regularity in how the operate and in what they produce. Which is to say that while in principle it is possible to design a program that would deem any such technique ineffective, such programs rarely have any other practical use. All this is best understood if we consider two prevalently used techniques of this kind: caching and branch prediction. Both techniques are implemented in virtually all modern high-performance processing systems.

Caching aims at better approximating the ideally large and fast memory device which corresponds to the data storage model typical programming languages present to their users. It has been long known that programs have a tendency to either access the same memory location repeatedly (temporal locality) or to access neighboring memory locations (spatial locality), both phenomena appearing close in time. Caches exploit this empirical observation by placing a set of recently accessed memory locations in a small and fast storage structure, a *cache*. As a result, many if not most of the memory accesses are serviced in the cache, benefiting from its low latency (how fast it responds) and high bandwidth (how much data it can respond with) characteristics. Had programs not exhibited temporal and spatial locality in their memory reference stream, caching would not have been an effective technique; data placed in the cache would rarely get referenced before evicted. Another example of a technique that exploits programs behavior is branch prediction. Branch prediction facilitates fetching and, often, executing instructions without having to wait to determine

whether these instructions should be executed (normally, we would have to wait until the current instruction completes execution to determine which instruction should we execute next). Branch prediction exploits the regularity found in the control flow paths programs tend to follow (this is not intended to be a formal, exhaustive definition of the underlying phenomena branch prediction exploits). Had programs not exhibited regularity in their control flow, branch prediction and the performance benefits it produces, would not have been possible.

As the preceding discussion serves to demonstrate, in our efforts to build even faster or better suited to our purposes computing systems, we may seek to understand how ordinary programs behave and develop techniques that exploit this behavior to better utilize the resources offered by the underlying semiconductor device technologies. In this context, this thesis introduces a form of regularity exhibited by ordinary, sequential programs along with a number of micro-architectural techniques that exploit this regularity to improve performance. Specifically, we have identified that high levels of regularity is there to be found in the relationships formed when loads (memory read instructions) and stores (memory write instructions) access memory. These relationships are commonly referred to as memory dependences, hence the name we use for this phenomenon: *memory dependence locality*. Informally, memory dependence locality suggests that if at some point a particular load or store experiences a memory dependence, chances are that the same memory dependence will be experienced again the next time the same instruction is encountered (a formal definition of memory dependences and of memory dependence locality can be found in chapter 2).

Identifying a particular regularity in program behavior in itself is useful only in indicating a potential for exploiting this regularity. Actual techniques that make use of this opportunity for some practical purpose are required. To this respect, in this thesis we present *memory dependence prediction*, a technique facilitated by memory dependence locality and three micro-architectural techniques that are based on memory dependence prediction. In memory dependence prediction, information about the memory dependences exhibited during program execution is collected on-the-fly (i.e., while the program is running) and is used to make educated guesses on the forthcoming dependence behavior of the program. In our proposal these actions take place in a program and programmer transparent way via the use of architecturally invisible structures.

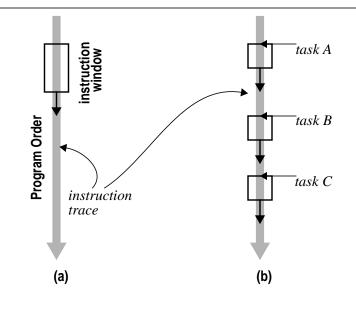

The three micro-architectural techniques we introduce are: (1) *memory dependence speculation and synchronization*, (2) *memory cloaking and bypassing*, and (3) *transient value cache*. A brief introduction of each of the aforementioned techniques and of their goals is given in the next section where we enumerate the contributions of this thesis.

## **1.1 Contributions**

The contributions of this thesis are: (1) we identify that programs exhibit locality in their memory dependence stream, (2) we present memory dependence prediction, a technique that exploits memory dependence locality to guess whether a instruction will experience a dependence and if necessary which this dependence exactly is, and (3) we present three micro-architectural techniques that utilize memory dependence prediction to improve performance. In Section 1.1.1 we discuss memory dependence locality and memory dependence prediction. In sections 1.1.2 through 1.1.3 we discuss the three micro-architectural techniques we propose.

#### **1.1.1 Memory Dependence Locality and Prediction**

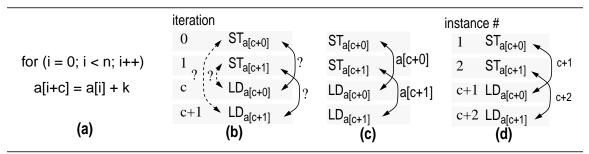

In this thesis we introduce *memory dependence locality*, a characteristic exhibited by ordinary, sequential programs. Memory dependence locality refers to the regularity that exists in the relationships formed when loads and stores access memory (a formal definition of memory dependences is given in chapter 2). We con-

sider two forms of memory dependence locality: (1) *memory dependence status locality* and (2) *memory dependence set locality* or, simply, *memory dependence locality*. Informally, memory dependence status locality suggests that, if at some point during execution a load or a store experiences a memory dependence of a particular type, it is highly probable that when encountered again, the same load or store will experience a memory dependence of the same type. In this case, which are the exact dependences experienced are not important, only whether such dependences exist is. Memory dependence locality is a specialization of memory dependence status locality. Memory dependence locality suggests that if at some point during execution a load or a store experience a particular dependence (or a set of dependences), it is highly probable that when encountered again, the same load or store will experience the same dependence (or dependences). In this case, not only whether dependences of a particular type exist is important, but also which exactly these dependences are.

Either form of memory dependence locality facilitates history-based prediction of the corresponding events. Specifically, in this thesis we present two memory dependence prediction techniques: (1) memory dependence status prediction, and (2) memory dependence set prediction, or simply, memory dependence prediction. *Memory dependence status prediction* is a technique that allows us to guess with high accuracy whether a load or a store has a memory dependence of a given type. *Memory dependence prediction* is a technique that allows us guess not only whether a given load or store has dependence but also which exactly this dependence (or dependences) is. Both techniques operate by (1) observing memory dependences as they occur through memory, (2) associating memory dependence information with the static instructions that are involved (e.g., with the PC of stores or loads), and (3) using the recorded information to make educated guesses on what dependences instructions will experience the next time they are encountered.

To support the efficacy of memory dependence prediction, in chapter 2 we study the memory dependence behavior of programs and demonstrate that: (1) sufficient regularity exist in both the memory dependence status and the memory dependence stream of programs, and (2) the working set of instructions with dependences is relatively small. The first property—as we explain in chapter 2—is a requirement of history-based prediction as it indicates that past dependence behavior is a good indicator of forthcoming memory dependence behavior. The second property suggests that we can collect and record dependence information for prediction purposes using finite structures of reasonable size. This is required if memory dependence prediction is to be of practical use.

In itself, memory dependence prediction serves just to provide highly accurate information about memory dependences. Techniques are required to make use of this information for some practical purpose. We present three such techniques in this thesis: (1) *dynamic speculation and synchronization of memory dependences, (2) speculative memory cloaking and bypassing,* and (3) *transient value cache.* A description of the goals and operation of each technique is given in the following three sections.

#### 1.1.2 Dynamic Speculation and Synchronization of Memory Dependences

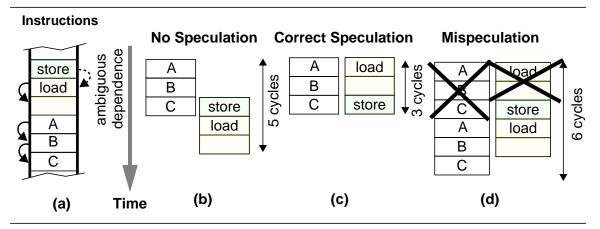

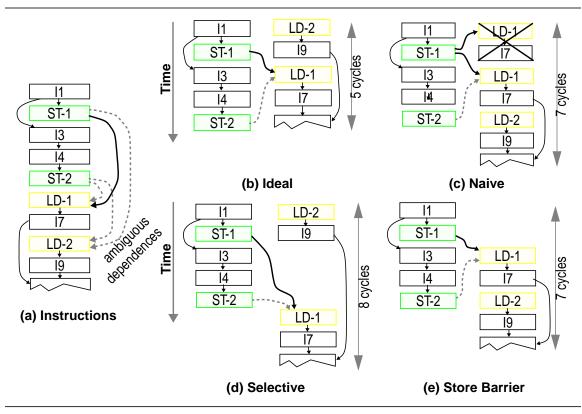

Techniques to exploit instruction-level parallelism (ILP) are an integral part of virtually all modern highperformance processors. With these techniques, instructions do not necessarily execute one after the other and in the order they appear in the program. Rather, instructions are executed in any order convenient provided however, that program semantics are maintained (i.e., the same results are produced). This ability is useful in reducing execution time by executing instructions in-parallel (many at the same time) and by avoiding stalling execution while an instruction takes its time to execute (e.g., it performs a relatively time consuming calculation or accesses a relatively slow storage device for its operands). An arena where ILP techniques are particularly useful is that of tolerating memory latency where these techniques are used to send loads requests as early as possible, overlapping memory processing time with other useful computation. One approach to exploiting ILP is to first make sure that executing an instruction will not violate program semantics *before* the instruction is allowed to execute. In the case of a load, this action amounts to waiting to determine if a preceding, yet unexecuted store writes to the same memory location, that is whether a *true dependence* with a preceding store exists. However, and as we explain in detail in chapter 3, waiting to determine whether a preceding store writes to the same memory location is not the best option. Higher performance is possible if *memory dependence speculation* is used, that is, if a load is allowed to execute speculatively before a preceding store on which it *may* be data dependent. Later on, and after the preceding store has calculated its address, we can check whether program semantics were violated. If no true memory dependence is violated in the resulting execution order, speculation was successful. Otherwise, speculation was erroneous and corrective action is necessary to undo the effects of erroneous execution. A penalty is typically incurred in the latter case.

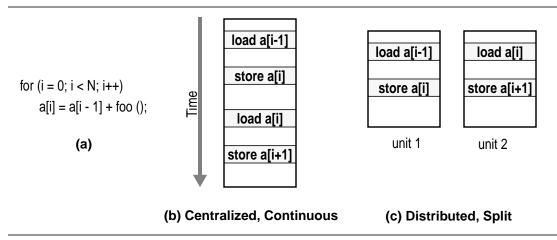

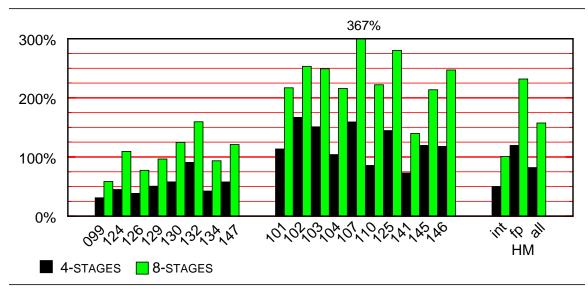

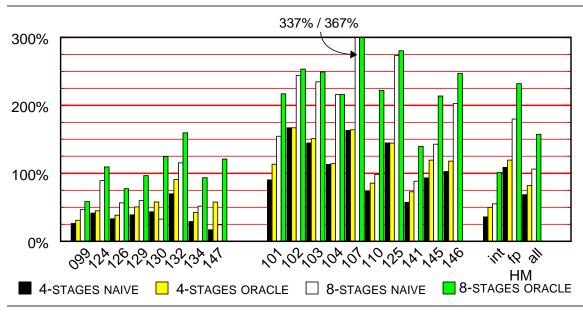

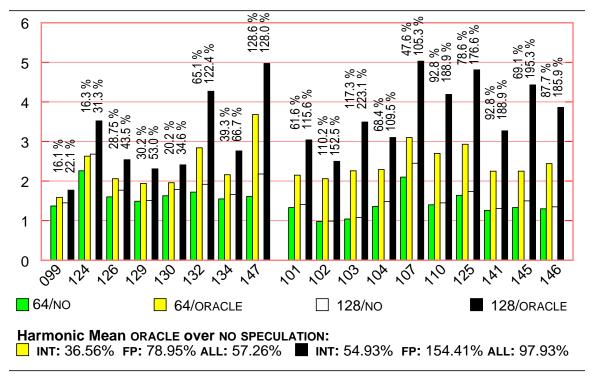

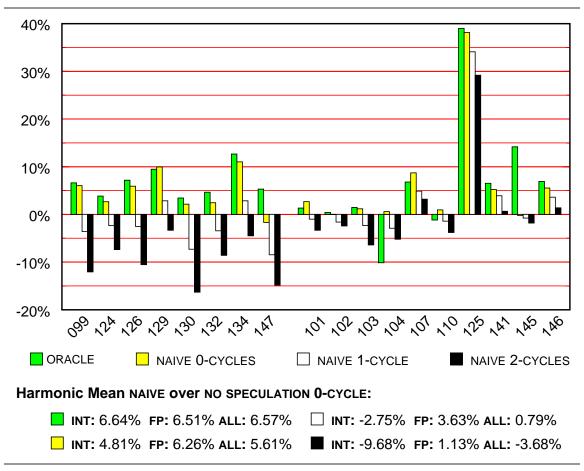

In this work we focus on dynamic memory dependence speculation techniques and study how existing methods of applying memory dependence speculation will scale for future generation processors. Prior to this work, memory dependence speculation was used whenever the opportunity to execute a load existed. We will refer to this technique as naive memory dependence speculation. In this work we demonstrate that as processors attempt to extract higher-levels of ILP by establishing larger instruction windows: (1) memory dependence speculation becomes increasingly important, and (2) the net penalty of memory dependence mispeculation can become significant. The latter observation suggests that further performance improvements are possible if mispeculations could be avoided. Specifically, we demonstrate that further performance improvements are possible under the following two execution models: (1) a centralized, continuous window ILP processor, and (2) in a distributed, split-window ILP processor. In the centralized, continuous window processor, the net penalty of mispeculation becomes significant when loads cannot inspect the addresses of preceding stores either because a mechanism is not provided (to simplify the design) or because of the latency required to inspect store addresses. In the distributed, spit-window processor mispeculations are problematic independently on whether loads can inspect preceding store addresses. Moreover, we demonstrate that the potential benefits increase as the size of the instruction window also increases in either processor environment.

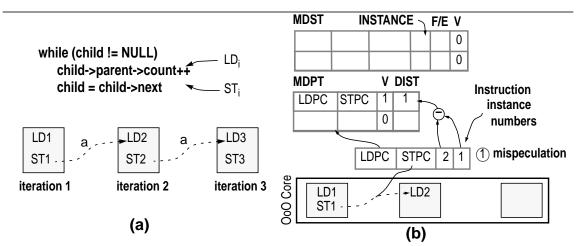

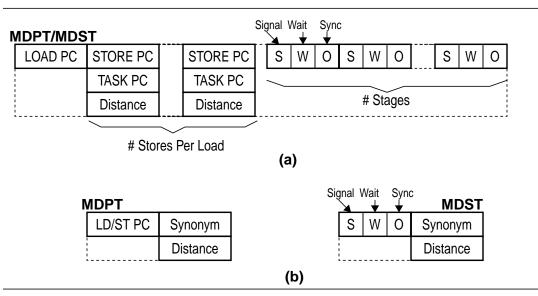

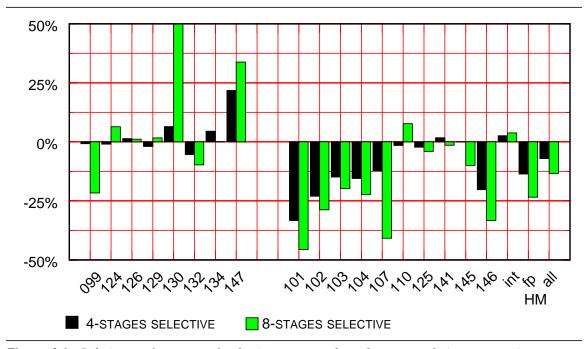

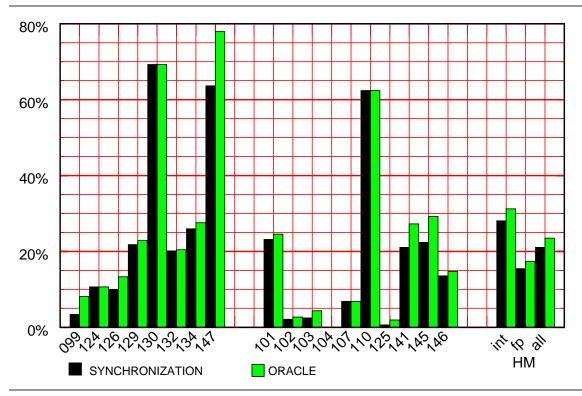

Motivated by the aforementioned observations we study the trade-offs involved in memory dependence speculations and propose techniques to improve the accuracy of memory dependence speculation. Specifically, we propose techniques to: (1) identify via memory dependence prediction those loads and stores that would otherwise be mispeculated, and (2) delay load execution *only as long as it is necessary* to avoid a memory dependence mispeculation. The best performing technique we propose is *memory dependence speculation and synchronization*, or *speculation/synchronization*. With this technique, initially loads are speculated whenever the opportunity exists (as it is common today). However, when mispeculations are encountered, information about the violated dependence is recorded in a memory dependence prediction structure. This information is subsequently used to predict whether the immediate execution of a load will result in a memory dependence violation, and (2) if so, which is the store this load should wait for.

Timing simulations show that for a distributed, split-window processor (i.e., Multiscalar [26,14,82,27,40,92,13]), our technique can improve performance by 28% for integer codes and 15% for floating point codes on the average. More importantly, the performance obtained through the use of our techniques is very close to that possible with perfect, in advance knowledge of all memory dependences (31% and 17% respectively), suggesting that our method is successful in attaining both goals of memory dependence speculation: (1) avoiding mispeculations, and (2) delaying load execution only as long as it is necessary.

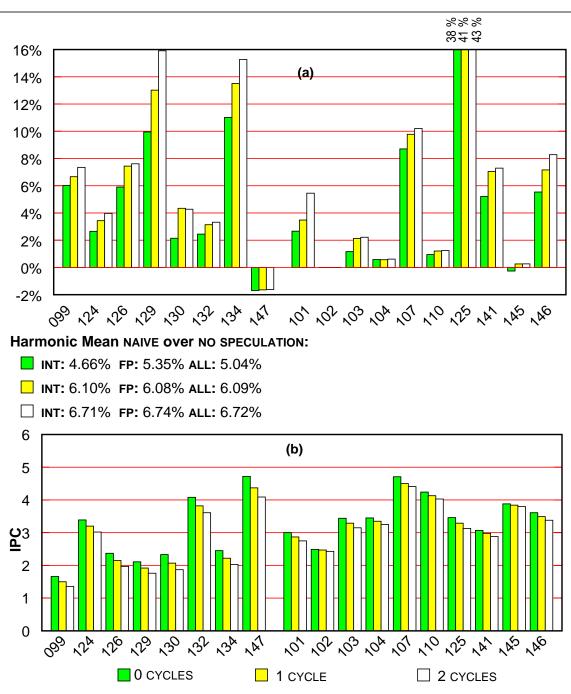

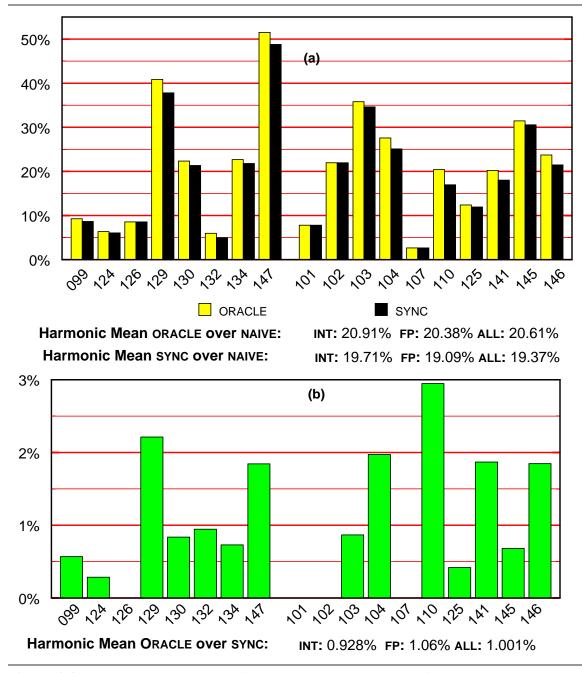

We also study memory dependence speculation under a centralized, continuous window processor (typical current superscalar) that utilizes fetch and execution units of equal bandwidth, and a program order priority scheduler (i.e., when there are many instructions ready to execute, the older ones in program order are given

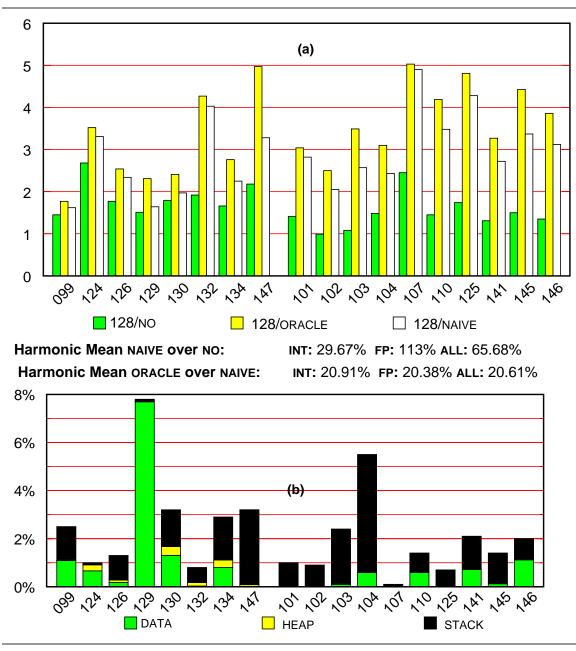

precedence). For this processor model we make two observations. The first is that using an address-based load/store scheduler (i.e., a structure where loads can inspect preceding store addresses to decide whether memory dependences exist) coupled with naive memory dependence speculation offers performance very close to that possible with perfect, in advance knowledge of all memory dependences, provided that going through the address-based scheduler does not increase load latency. The second is that if building an address-based load/store scheduler is not an option (clock cycle) or not a desirable option (complexity), naive memory dependence speculation can still offer most of the performance benefits possible by exploiting load/store parallelism. However, under this set of constraints the net penalty of mispeculation is significant suggesting that our memory dependence speculation and synchronization technique might be useful in improving performance. Specifically, timing simulations show that an implementation of our techniques results in performance improvements of 19.7% (integer) and 19.1% (floating-point) which are very close to those ideally possible: 20.9% (integer) and 20.4% (floating-point).

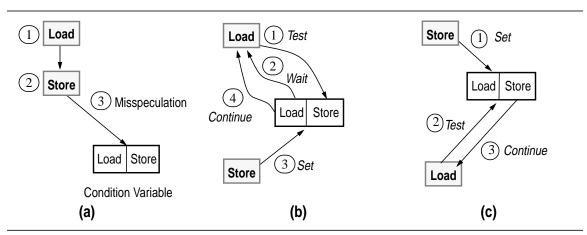

#### 1.1.3 Speculative Memory Cloaking and Bypassing

Faster execution requires faster methods of reading and writing memory values. The memory dependence speculation and synchronization technique we described in the previous section helps in reducing the observed memory latency by allowing loads to access memory earlier. However, even with this technique, the interface used to read and write memory values and the mechanisms implementing memory remain the same: a load or store has to first calculate an address and then use this address to access memory. Yet, memory can be viewed as an interface through which programs synthesize a desired, possibly elaborate action. Which is to say that while from the perspective of a single instruction memory appears as a storage device, from the perspective of the program as a whole, reading or writing a memory value is really a single step in a series of actions which combined produce a desired effect. Just because we have decided to use an address-based memory interface in expressing what the program does, this does not imply that we have to implement this action in that way also. This perspective hints to another direction of improving memory performance, that of: (1) first identifying what purpose memory serves at any given point, (2) then, studying whether the address-based interface introduces any inefficiencies or overheads, and (3) if so, designing mechanisms that can perform the desired action faster.

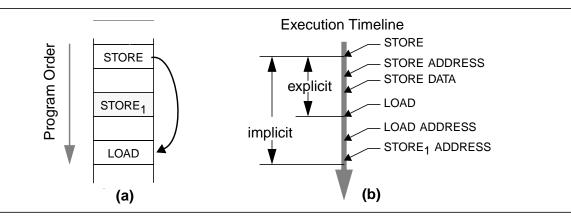

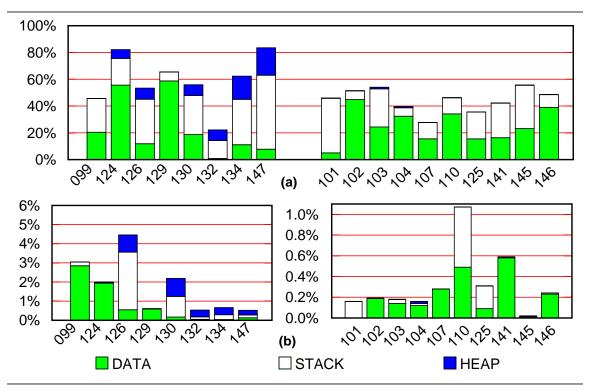

In this thesis we identify two common uses of memory: (1) *inter-operation communication*, and (2) *data-sharing*. In inter-operation communication a store is used to write a memory value so that loads may later read it. In data-sharing, a memory location is used as a place holder for values that are read repeatedly (i.e., by many loads) in the program. As we explain in detail in chapter 4, the address-based memory interface introduces both overheads and inconveniences in performing these actions. For example, for inter-operation communication to take place, both the store and the load have to calculate their address and then locate each other using that address. These actions take time and more importantly the value being communicated may be available long before these actions complete (a detailed discussion of the overheads and inconveniences introduced by the address-based memory interface is delayed until chapter 4).

We also observe that an explicit specification of either action has potential advantages over the current address-based specification. In an explicit specification of inter-operation communication both the store and the load that ought to communicate, not only are given knowledge of the desired action but also can locate each other directly without having to first calculate an address. Similarly, in an explicit specification of data-sharing, a load that will access a previously accessed memory location, is not only given knowledge of this fact, but is also provided with a mechanism to identify the earlier load that accessed the same memory location without having to first calculate an address.

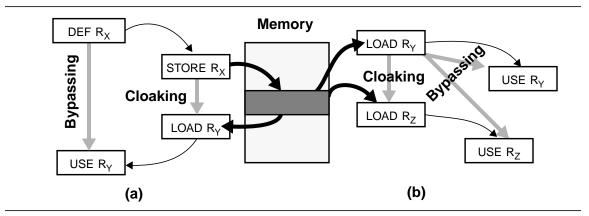

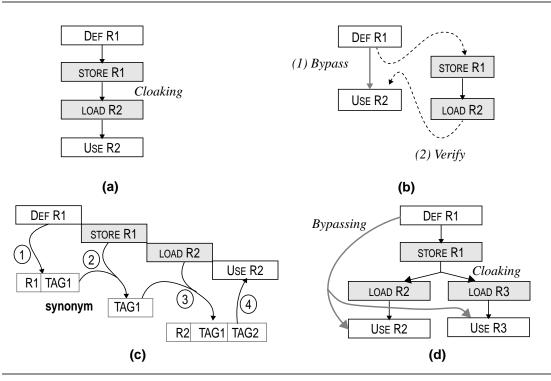

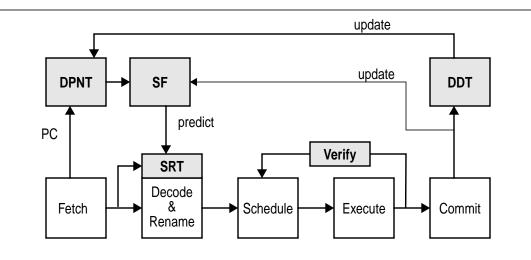

Motivated by the aforementioned observations we present *speculative memory cloaking*, or *cloaking*, a technique that: (1) transparently converts the address-based specification of inter-operation communication

and of data-sharing into an explicit form, and (2) uses this explicit representation to allow loads to obtain their memory value by just naming an earlier store or load that wrote or accessed it. In cloaking, memory dependence prediction is used to identify those loads and stores that communicate and to identify those loads that access a common memory location. This information is used to create direct, albeit speculative links between these instructions so that values can flow directly, as soon as they become available. In particular, the mechanism we present operate by associating memory dependence information with the PC of the static loads and stores. This permits loads and stores to pass values via cloaking using information derived using their PCs.

Aiming at further reducing memory value access latency, we observe that loads and stores typically do not change the data they write or read. These instructions are really used as agents retrieving or placing memory data that other instructions produce or consume; the value written by a store is produced by another instruction, while the value read by a load is passed to other instructions. Motivated by this observation we propose *speculative memory bypassing*, a straightforward extension to cloaking, that speculatively bypasses loads and stores, linking producing and consuming instructions directly. Specifically, when memory is used as an inter-operation mechanism, speculative memory bypassing converts DEF-STORE-LOAD-USE chains into DEF-USE ones. When memory is used to hold data that is read repeatedly, this technique consolidates a series of  $LOAD_1-USE_1...LOAD_N-USE_N$  chains into a single  $LOAD_1-USE_1...USE_N$  producer-consumer graph.

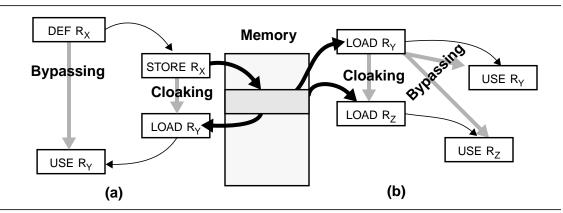

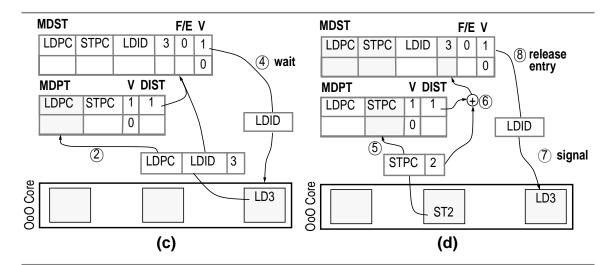

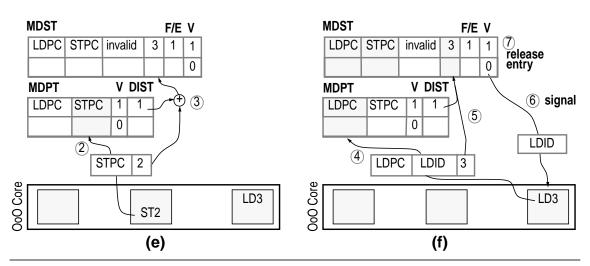

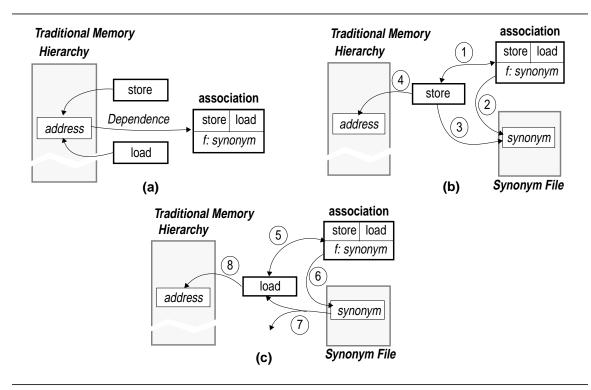

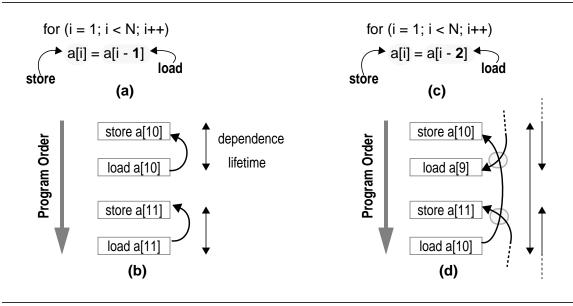

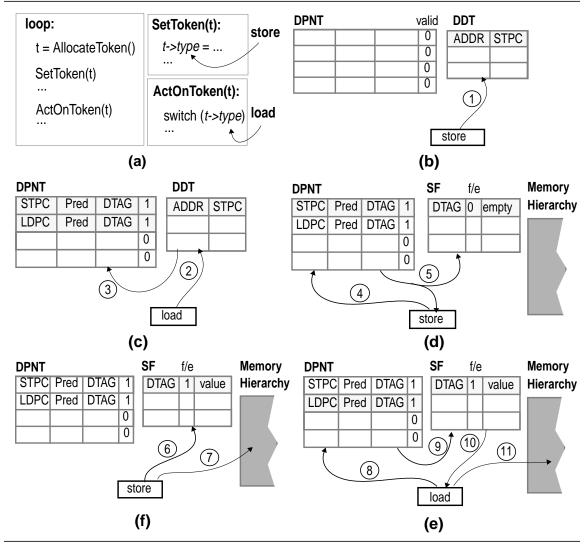

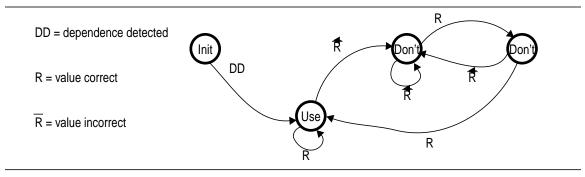

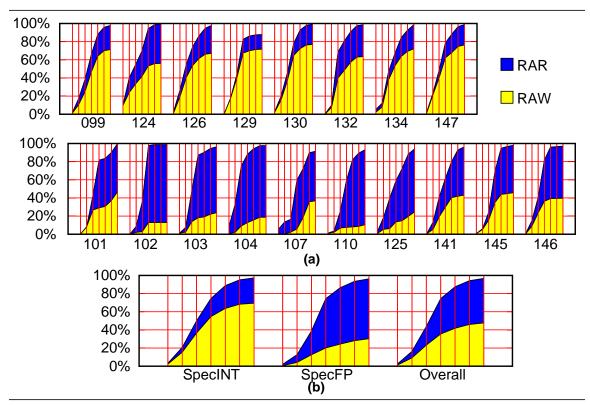

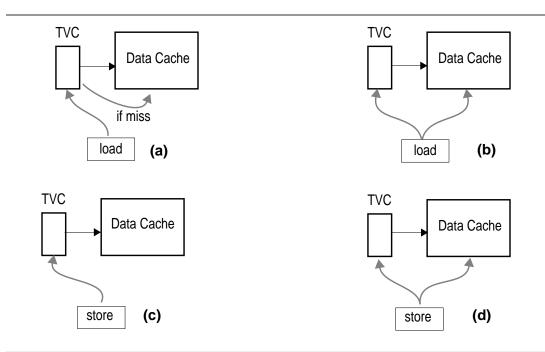

*Figure 1.1:* Speculative Memory Cloaking and Bypassing. (a) Inter-operation communication: exploiting read-after-write dependences. (b) Data sharing: exploiting read-after-read dependences.

The effect achieved via cloaking and bypassing is illustrated in Figure 1.1. Cloaking allows values to flows between loads and stores, while bypassing takes loads and stores off the communication path, allowing values to flow directly from the actual producer to the actual consuming instructions.

Since we make use of memory dependence prediction, the proposed techniques are speculative and so are the values obtained through their use. Accordingly, value verification through the traditional memory name space is necessary. However, this verification can take place while the speculative values are used for further processing. Provided that speculation is successful, the observed memory latency is reduced as instructions that would otherwise wait for the traditional memory hierarchy to provide a value may now execute earlier, possible even before the memory access is initiated.

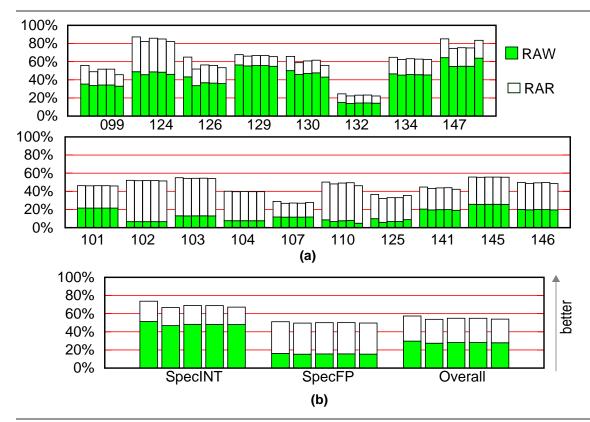

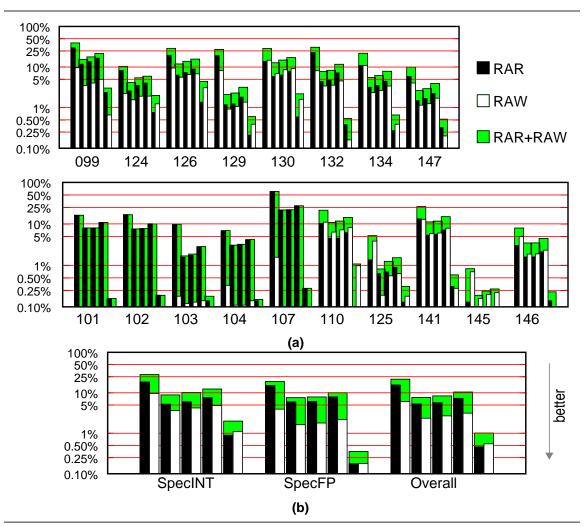

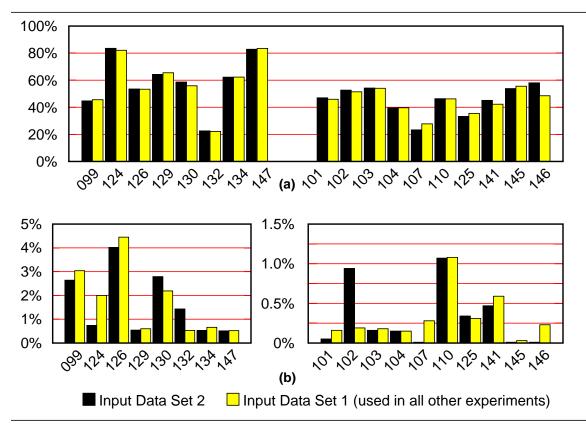

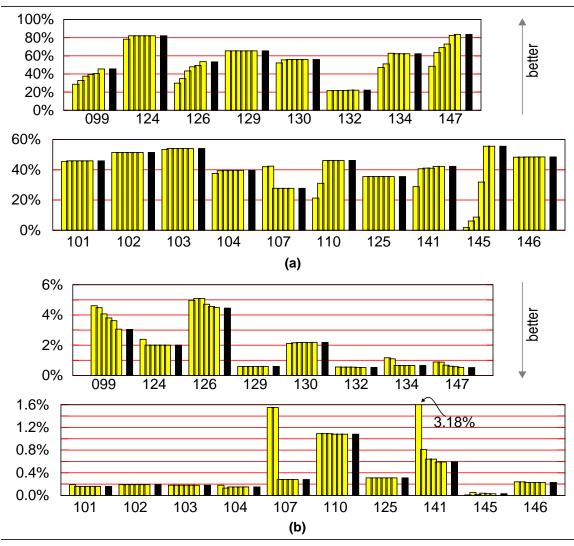

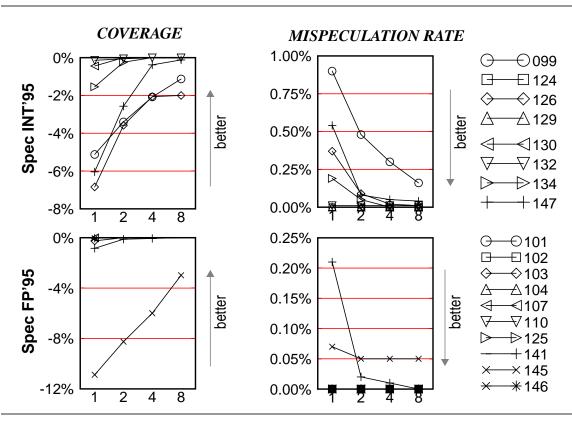

Trace driven simulations show that a straightforward implementation of a combined cloaking/bypassing mechanism can supply correct values for about 60% and 50% of all loads for the integer and the floating point programs respectively. Timing simulations show that for a fairly aggressive and highly optimized 8-way superscalar with an 128-entry window and that uses memory dependence speculation, cloaking/bypassing can improve performance by 4% and 9%.

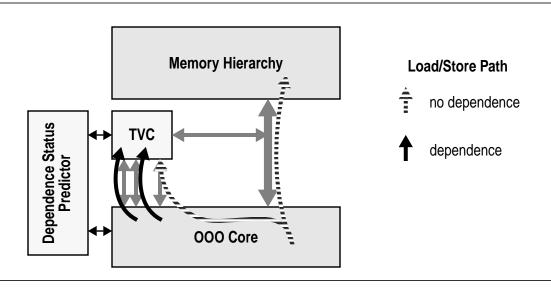

#### **1.1.4 Transient Value Cache**

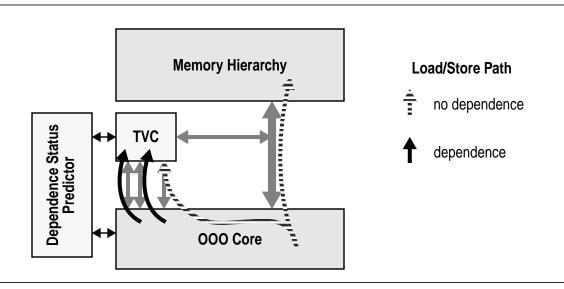

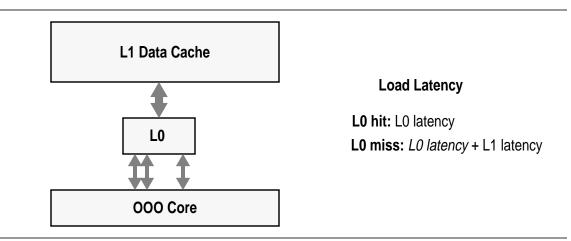

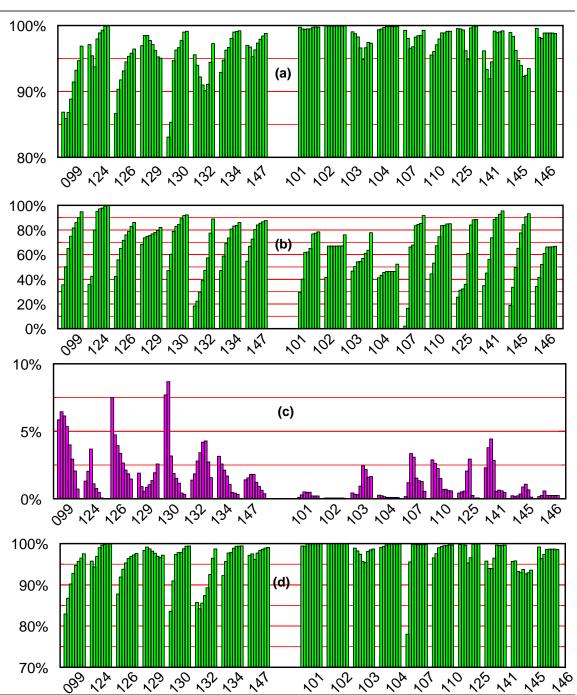

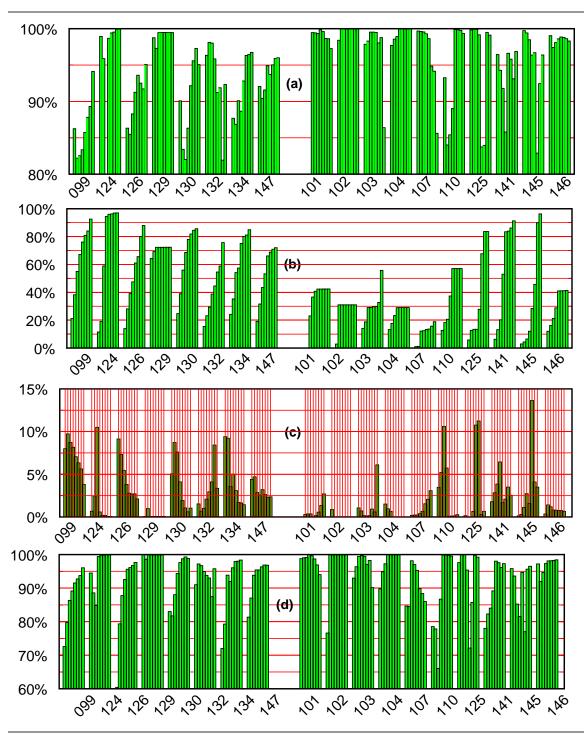

Highly parallel execution can benefit from both low memory latency and from the ability to perform multiple memory accesses in parallel. Both speculation/synchronization and cloaking/bypassing aim at reducing memory latency. The final technique we present in this work aims at supporting multiple memory accesses per cycle. This technique is motivated by the relatively large fraction of loads that read a value that was either recently written by a store or recently read by another load. Specifically, we found that roughly 70% (integer programs) and 43% (floating-point programs) of all loads read a memory location that is within the last 128 memory locations accessed by preceding stores or loads. This result suggests that a relatively small data cache capable of storing just 128 memory locations could potentially service all these loads. Such a small data cache could help in supporting multiple memory requests for the following two reasons: (1) it could be easier to multiport than a reasonably sized L1 data cache, and (2) loads that would get serviced in this small data cache will not have be exposed to the L1, freeing up L1 port resources to be used for other loads. Unfortunately, placing such a data cache in between the processor and the L1 would increase the latency of all dynamic loads that would not hit in it (30% and 57% respectively). Placing it in series with the L1 data would not be of much use either as all loads will have to be exposed to both the L1 and the small data cache. What is needed is a method to place this small data cache in series with the L1 for those loads that will hit in it and in parallel to the L1 for all other loads. This is exactly what the Transient Value Cache (TVC) tries to do. The Transient Value Cache, or TVC is a novel memory hierarchy component that combines a memory dependence status predictor and a relatively small, narrow data cache. The basic approach is illustrated in Figure 1.2. The TVC records in its data cache component the *n*th most recent accessed memory locations as a traditional data cache would. However, contrary to what is done in a traditional memory hierarchy, the data cache component does not always appear in series with the rest of the memory hierarchy. Instead, its placement is decided using a memory dependence prediction as follows: When a load is ready to access memory, a prediction is made on whether the memory location it will access is resident in the TVC, or viewed differently whether the load has a dependence with a recent store or load respectively. If so, the load is send only to the TVC, in which case the TVC appears in *series* with the L1 data cache. Otherwise the load is send to both the TVC and the rest of the memory hierarchy, in which case the TVC appears in parallel with the L1 data cache. Provided that prediction accuracy is high, the potential benefits of the TVC approach are: (1) the loads that hit in the TVC are hidden from the rest of the memory hierarchy, freeing up L1 data cache ports to be used by other loads, (2) the latency of loads that are unlikely to hit in the TVC remains unchanged. High prediction accuracy is essential as the TVC may result into increased load latency when prediction incorrectly indicates that a load will find its data in the TVC. We also present a possible store-to-store dependence (WAW) status prediction extension, were the TVC is also used to hide from the rest of the memory hierarchy those store accesses that are likely to be overwritten quickly precluding potential problems with writeback traffic contention while reducing the L1 port requirements.

Trace driven simulation shows that a TVC comprised of a counter-based memory dependence status predictor and a 128-word (512 bytes) cache component can service 66.8% and 40.4% of all loads on the average and for the integer and floating point codes respectively. More importantly, only 3.3% and 1.1% of all loads would observe a latency increase as the result of erroneous memory dependence status prediction. In contract, a traditional memory organization that would place the 128-word data cache in series with the L1, would result in 70.1% (integer) and 43.1% (floating-point) reduction of loads at the L1 interface while increasing the latency of 29.7% (integer) and 43.7% (floating-point) of all loads. While the aforementioned results provide an indication of the potential of the TVC approach, further investigation is required to determine its performance impact.

Figure 1.2: The Transient Value Cache

## **1.2 Thesis Organization**

The remainder of this thesis is organized as follows: in Section 1.3 we detail the experimental framework used to evaluate the ideas and techniques we propose. In chapter 2, we provide a formal definition of memory dependences, a short introduction to the principles of operation of history-based memory dependence predictors and also present an analysis of the memory dependence behavior of the programs studied. This analysis focuses on those aspects of memory dependence behavior that are interesting from the perspective of history-based memory dependence prediction. It is here that we provide experimental evidence in support of the efficacy of memory dependence prediction. In chapter 3, we study memory dependence speculation and present memory dependence speculation and synchronization. In chapter 4, we present speculative memory cloaking and bypassing. In chapter 5, we present the transient value cache approach. Finally, we summarize our findings in chapter 6 and offer suggestions on how this work can be extended. In the appendix we present additional measurements that relate to memory dependence prediction and to its applications we present in this thesis.

## **1.3 Experimental Framework**

In this section we detail the experimental framework we used for the experiments reported in this thesis. In Section 1.3.1 we provide details on the programs analyzed and on the compiler infrastructure we used. In Section 1.3.2 we discuss our simulation methodology,

## **1.3.1** Programs and Compiler Infrastructure

In all experiments reported in this thesis we used the SPEC95 benchmark suite [86]. We used two input data sets. The exact parameters used per input data set are given in Table . Unless otherwise noted, the first input data set is used. All programs were compiled using a modified version of the GNU *gcc* compiler version 2.7.2. The modifications allow the compiler to also generate binaries for the Multiscalar architecture [26, 82] and only affects binaries compiled for that architecture. The base instruction set architecture is the MIPS-I [42] but with no architectural delay slots of any kind. The modifications done to gcc along with a

description of the additional instructions introduced to support the Multiscalar architecture are detailed in [92]. Fortran sources were compiled by first converting them to C using AT&T's *f2c* compiler. Unfortunately, we have no way of determining how the use of a FORTRAN-TO-C translator impacts the quality of the produced code. However, it is to be expected that an actual FORTRAN compiler would improve the quality of the produced code mainly as the result of better static disambiguation and scheduling. We note that such optimizations may affect the results of the techniques we propose either way. For example, while better disambiguation may help in exposing some of the load/store parallelism in floating point programs, hence reducing the potential of a dynamic approach, it will also reduce the distance between dependent loads and stores increasing the probability of mispeculation, hence increasing the potential of the speculation/synchronization technique presented in chapter 3. All programs were compiled using the -O2 optimization level and with loop unrolling and function inlining enabled.

Two binaries were generated per program: (1) a MIPS-I binary, and (2) a Multiscalar binary. The instruction counts, along with the fraction of loads and stores executed per binary and input data set are given in Table 1.1.

#### **1.3.2 Simulation Methodology**

We employ two simulation techniques: (1) trace-driven simulation and (2) detailed, execution-driven timing simulation. Traces are generated using two functional simulators, one for MIPS-I ISA and one for the Multiscalar architecture. The functional simulators execute *all* user-level instructions. System calls are serviced by the OS of the host machine. The functional simulators we used are derivatives of the Multiscalar functional simulator [13]. In all experiments that utilize functional simulation we included all user-level instructions in our measurements.

We also make use of detailed, execution-driven timing simulation. For this purpose we utilized two simulators, one that simulates a dynamically scheduled superscalar processor and one that simulated a Multiscalar processor. Both simulators are derivatives of the Multiscalar timing simulator [13]. The out-of-order core simulator was rewritten to facilitate simulation of the techniques we examine and to better approximate the processor models we study. Moreover, mechanisms to collect advance memory dependence informations were incorporated. While these modifications were required for our experimentation that also decreased simulation speed considerably. The simulators execute all user-level instructions including those on control speculative paths. Systems calls are redirected to the OS of the host machine.

The default superscalar configuration we used is detailed in Table 1.2. We used a 32K data cache to compensate for the relatively small memory working sets of the SPEC95 programs. For some experiments we use a 64-entry reorder buffer model. That model, has 4 copies of all functional units, a 2-port load/store queue and memory system, and can fetch up to 4 instructions per cycle.

The default Multiscalar configuration we used is detailed in Table 1.3. For some experiments we used models of processing units with 4 copies of all functional units and all 4 load/store ports. For those experiments the number of banks and miss handlers for the I-cache, D-cache and the ARB was partitioned accordingly to provide four times the bandwidth of the configuration shown in Table 1.3.

Finally, to attain reasonable simulation times we utilized sampling for the timing simulations. In this technique which was also employed, for example, in [96,67,13], the simulator switches between functional and timing simulation. The mode of simulation is changed once a predefined number of instructions have been simulated. In all sampling simulations the observation size is 50,000 instructions. We chose sampling ratios that resulted in rougly 100M instructions being simulated in timing mode (i.e., sample size). We did not use sampling for 099.go, 107.mgrid, 132.ijpeg and 141.apsi. We used a 1:1 timing to functional simulation ratio

| Program      | Input Data Set 1                                                                                                                                                                     | Input Data Set 2                                             |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| SPECint'95   |                                                                                                                                                                                      |                                                              |  |  |  |  |  |

| 099.go       | play level = 9, board size = 9                                                                                                                                                       | train input set: play level = 9, board<br>size = 50          |  |  |  |  |  |

| 124.m88ksim  | modified test input: 370 iterations of Dhrystone<br>Benchmark                                                                                                                        | train input set                                              |  |  |  |  |  |

| 126.gcc      | reference input file recog.i                                                                                                                                                         | test input: file cccp.i                                      |  |  |  |  |  |

| 129.compress | modified train input: maximum file size increased to 50,000                                                                                                                          | modified train input: maximum file size increased to 100,000 |  |  |  |  |  |

| 130.li       | modified test input: (queens 7)                                                                                                                                                      | train input set                                              |  |  |  |  |  |

| 132.ijpeg    | test input                                                                                                                                                                           | train input set                                              |  |  |  |  |  |

| 134.perl     | modified train input: jumple.pl with dictionary reduced by retaining every other 15th word                                                                                           | train input set                                              |  |  |  |  |  |

| 147.vortex   | modified train input: persons.250k database,<br>PART_COUNT 250, LOOKUPS 20, DELETES 20,<br>STUFF_PARTS 100, PCT_NEWPARTS 10,<br>PCT_LOOKUPS 10, PCT_DELETES 10,<br>PCT_STUFFPARTS 10 | train input set                                              |  |  |  |  |  |

|              | SPECfp'95                                                                                                                                                                            |                                                              |  |  |  |  |  |

| 101.tomcatv  | modified train input: N = 41                                                                                                                                                         | train input set                                              |  |  |  |  |  |

| 102.swim     | modified train input: X = 256, Y = 256                                                                                                                                               | test input set                                               |  |  |  |  |  |

| 103.su2cor   | modified test input: LSIZE = 4 4 4 8 16                                                                                                                                              | test input set                                               |  |  |  |  |  |

| 104.hydro2d  | modified test input: MPROW = 200                                                                                                                                                     | test input set                                               |  |  |  |  |  |

| 107.mgrid    | modified test input: LMI = 4                                                                                                                                                         | test input set                                               |  |  |  |  |  |

| 110.applu    | modified train input: itmax = 25, nx = 10, ny = 10, nz = 10                                                                                                                          | train input set                                              |  |  |  |  |  |

| 125.turb3d   | modified train input: nsteps = 1, itest = 0                                                                                                                                          | test input set                                               |  |  |  |  |  |

| 141.apsi     | modified train input: grid points x = 32, grid points z=<br>8, time steps = 130                                                                                                      | test input set                                               |  |  |  |  |  |

| 145.fpppp    | modified reference input: natoms = 4                                                                                                                                                 | train input set                                              |  |  |  |  |  |

| 146.wave5    | modified train input: particle distribution 1000 20, grid size 625x20                                                                                                                | train input set                                              |  |  |  |  |  |

Benchmark input parameters.

|              | Non-Multiscalar                   |       |        |                  | Multiscalar |        |         |       |        |

|--------------|-----------------------------------|-------|--------|------------------|-------------|--------|---------|-------|--------|

|              | Input Data Set 1 Input Data Set 2 |       |        | Input Data Set 1 |             |        |         |       |        |

| Program      | IC                                | Loads | Stores | IC               | Loads       | Stores | IC      | Loads | Stores |

|              |                                   |       |        | SPECint'95       |             |        |         |       |        |

| 099.go       | 133.8                             | 20.9% | 7.3%   | 553.7            | 21.3%       | 7.9%   | 141.2   | 22.7% | 7.8%   |

| 124.m88ksim  | 196.3                             | 18.8% | 9.6%   | 141.5            | 18.5%       | 13.3%  | 213.3   | 17.3% | 8.7%   |

| 126.gcc      | 316.9                             | 24.3% | 17.5%  | 1,496.5          | 23.4%       | 19.4%  | 333.9   | 23.9% | 17.3%  |

| 129.compress | 153.8                             | 21.7% | 13.5%  | 296.4            | 21.7%       | 12.9%  | 153.8   | 21.7% | 13.5%  |

| 130.li       | 206.5                             | 29.6% | 17.6%  | 182.9            | 25.4%       | 16.1%  | 229.7   | 26.6% | 15.7%  |

| 132.ijpeg    | 129.6                             | 17.7% | 8.7%   | 1,478.2          | 17.6%       | 8.4%   | 139.2   | 18.6% | 9.0%   |

| 134.perl     | 176.8                             | 25.6% | 16.6%  | > 2,200.0        | 25.5%       | 16.4%  | 176.8   | 25.6% | 16.6%  |

| 147.vortex   | 376.9                             | 26.3% | 27.3%  | > 2,200.0        | 28.6%       | 24.8%  | 390.7   | 21.3% | 30.6%  |

|              |                                   |       |        | SPECfp'95        |             |        |         |       |        |

| 101.tomcatv  | 329.1                             | 31.9% | 8.8%   | > 2,200.0        | 31.5%       | 8.9%   | 333.7   | 30.6% | 8.7%   |

| 102.swim     | 188.8                             | 27.0% | 6.6%   | 753.1            | 27.0%       | 6.6%   | 191.8   | 27.0% | 6.5%   |

| 103.su2cor   | 279.9                             | 33.8% | 10.1%  | 1,099.9          | 34.0%       | 10.0%  | 283.7   | 33.5% | 10.0%  |

| 104.hydro2d  | 1,128.9                           | 29.7% | 8.2%   | 1,130.1          | 29.7%       | 8.2%   | 1,162.6 | 29.4% | 8.0%   |

| 107.mgrid    | 95.0                              | 46.6% | 3.0%   | > 2,200.0        | 49.3%       | 2.1%   | 100.6   | 46.1% | 5.2%   |

| 110.applu    | 168.9                             | 31.4% | 7.9%   | 649.3            | 31.5%       | 7.9%   | 171.8   | 31.9% | 8.0%   |

| 125.turb3d   | 1,666.6                           | 21.3% | 14.6%  | > 2,200.0        | 21.1%       | 14.1%  | 1,701.7 | 20.6% | 14.4%  |

| 141.apsi     | 125.9                             | 31.4% | 13.4%  | >2,200.0         | 30.8%       | 12.2%  | 129.5   | 31.0% | 13.5%  |

| 145.fpppp    | 214.2                             | 48.8% | 17.5%  | 469.6            | 48.9%       | 17.2%  | 202.5   | 49.4% | 11.0%  |

| 146.wave5    | 290.8M                            | 30.2% | 13.0%  | >2,200.0         | 32.0%       | 12.7%  | 299.3   | 30.2% | 12.9%  |

Table 1.1: Benchmark Execution Characteristics. Instruction counts ("IC" columns) are in millions.

(i.e., once 50000 instructions are simulated in timing mode, we switch to functional mode and simulate 50000 instructions before switching back to timing mode, and so on) for: *110.applu, 124.m88ksim, 130.li, 134.perl* and *145.fpppp*. We used a 1:2 timing to functional simulation ratio (i.e, once 50000 instructions are simulated in timing mode, we switch to functional mode and execute 1000000 instructions before switching back to timing mode, and so on) for: *101.tomcatv, 102.swim, 126.gcc, 129.compress, 146.wave5* and *147.vortex.* We used a 1:3 timing to functional simulation ratio for *103.su2cor*. And finally, we used a 1:10 timing to functional simulation ratio for: *104.hydro2d* and *125.turb3d*. During the functional portion of the

| Fetch<br>Interface              | Up to 8 instructions can be fetched per cycle. Up to 4 fetch requests can be active at any time. Combining of up to 4 non-continuous blocks.                                                                                                                                                                                                                                                                                |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch<br>Predictor             | 64K-entry combined predictor [58]. Selector uses 2-bit counters. 1st predictor: 2bit counter<br>based. 2nd predictor: <i>Gselect</i> with 5-bit global history. 4 branches can be resolved per cycle. 64-<br>entry call stack. 2K BTB.<br>Up to 4 predictions per cycle.                                                                                                                                                    |

| Instruction<br>Cache            | 64K, 2-way set associative, 8 banks, block interleaved, 256 sets per bank, 32 bytes per block, 2 cycles hit, 10 cycle miss to unified, 50 cycle miss to main memory.<br>Lockup free, 2 primary misses per bank, 1 secondary miss per primary.<br>LRU replacement.                                                                                                                                                           |

| OOO<br>core                     | <ul> <li>128-entry reorder buffer, up to 8 operations per cycle, 128-entry combined load/store queue, with 4 input and 4 output ports.</li> <li>Loads can execute as soon as their address becomes available.</li> <li>Stores check for memory dependence violations by comparing addresses and data.</li> <li>It takes a combined 4 cycles for an instruction to be fetched and placed into the reorder buffer.</li> </ul> |

| Architected<br>Registers        | 64 integer, 64 floating point, HI, LO and FSR.                                                                                                                                                                                                                                                                                                                                                                              |

| Functional<br>Units             | 8 copies of all functional units. All are fully-pipelined. 4 memory ports.                                                                                                                                                                                                                                                                                                                                                  |

| Functional<br>Unit<br>Latencies | Integer: 1 cycle latency except for: multiplication 4 cycles, division 12 cycles,.<br>Floating point: 2 cycles for addition/subtraction and comparison (single and double precision or<br>SP/DP). 4 cycles SP multiplication, 5 cycles DP multiplication, 12 cycles SP division, 15 cycles<br>DP division.                                                                                                                  |

| Store<br>Buffer                 | 128-entry. Does not combine store requests to memory. Combines store requests for load for-<br>warding.                                                                                                                                                                                                                                                                                                                     |

| Data<br>Cache                   | 32K, 2-way set associative, 4 banks, 256 sets per bank, 32 bytes per block, 2 cycle hit, 10 cycle miss to unified, 50 cycle miss to main memory. Lockup-free, 8 primary miss per bank, 8 second-ary miss per primary. LRU replacement.                                                                                                                                                                                      |

| Unified<br>Cache                | 4M-byte, 2-way set associative, 4 banks, 128-byte block, 8 cycle + # 4 word transfer * 1 cycle hit, 50 cycles miss to main memory. Lockup-free, 4 primary miss per bank, 3 secondary per primary.                                                                                                                                                                                                                           |

| Main<br>Memory                  | Infinite, 34 cycle + #4 word transfer * 2 cycles access.                                                                                                                                                                                                                                                                                                                                                                    |

Table 1.2: Default configuration for superscalar timing simulations

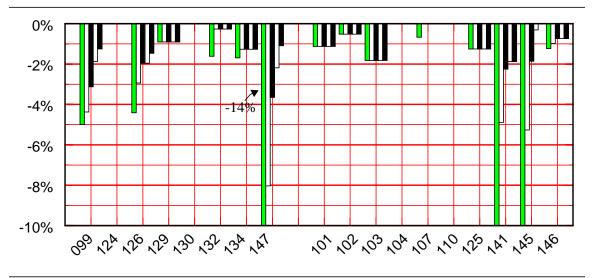

simulation the following structures were simulated: I-cache, D-cache, and branch prediction. Table 1.4 presents data that are useful in quantifying the error that is introduced by the use of sampling. In this experiments we report the relative difference in IPC (instructions per cycle) reported with sampling simulation over full timing simulation of the default superscalar configuration.

| Processing<br>Units             | <ul> <li>4 or 8, single task, 16-entry reorder buffer with 8-entry scheduler.</li> <li>Functional Units: 2 copies of all functional units, except for load/store units that has 1 port. Latencies same as in TableSection 1.2.</li> <li>Load/Store unit: 16 entry load/store queue, 16 entry store buffer non-combining to memory, combining for local load requests. Loads may execute after all preceding local stores have calculated their address.</li> <li>Fetch interface: 2 instructions per cycle, one branch prediction, 16-entry call-stack, 1K BTB.</li> <li>Control Predictor: global-pattern based, 16-bit pattern register, 64K-entry, 2-bit counters, 2 targets.</li> </ul> |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inter-Task<br>Predictor         | Path-based DOLC=7,3,6,8 path register 64K-entry, 2-bit counters, 4 targets [13]. 64-entry call-<br>stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Task<br>Cache                   | <ul><li>1K-entry, 2-way set associative, 64-byte task descriptor, LRU replacement.</li><li>1 cycle hit, 12 cycle miss to unified, 50 cycle miss to main memory.</li><li>1 bank, bus, lockup.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Instruction<br>Cache            | 64K, 2-way set associative, #PU banks, block interleaved, 32 bytes per block, 1 cycle hit, 10 cycle miss to unified, 50 cycle miss to main memory.<br>Lockup free, 8 primary misses per bank, 8 secondary miss per primary.<br>LRU replacement. Crossbar with one port per PU and per bank.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Register<br>File                | 4 registers per cycle, 2 cycle latency between adjacent units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address<br>Resolution<br>Buffer | #PU banks, 32-way set associative, 128 entries per bank, byte disambiguation granularity. 2 cycle hit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data<br>Cache                   | 32K, 2-way set associative, #PU banks, 32 bytes per block, 2 cycle hit, 10 cycle miss to unified, 50 cycle miss to main memory. Lockup-free, 8 primary miss per bank, 2 secondary miss per primary. LRU replacement. Crossbar with one port per PU and per bank. Same block access combining for crossbar.                                                                                                                                                                                                                                                                                                                                                                                  |

| Unified<br>Cache                | 4M-byte, 2-way set associative, 4 banks, 128-byte block, 8 cycle + # 4 word transfer * 1 cycle hit, 50 cycles miss to main memory. Lockup-free, 4 primary miss per bank, 3 secondary per primary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Main<br>Memory                  | Infinite, 34 cycle + #4 word transfer * 2 cycles access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 1.3: Default configuration for Multiscalar timing simulations.

|     | IPC Full | Relative<br>Difference<br>w/ Sampling |     | IPC Full | Relative<br>Difference<br>w/ Sampling |

|-----|----------|---------------------------------------|-----|----------|---------------------------------------|

| 099 | 1.81     | 0.0% (N/A)                            | 101 | 3.06     | +0.653%                               |

| 124 | 3.54     | -1.142%                               | 102 | 2.39     | +3.347%                               |

| 126 | 2.56     | -1.171%                               | 103 | 3.51     | -0.854%                               |

| 129 | 2.32     | 0.0%                                  | 104 | 3.48     | -0.574%                               |

| 130 | 2.38     | 0.0%                                  | 107 | 5.11     | 0.0% (N/A)                            |

| 132 | 4.16     | 0.0% (N/A)                            | 110 | 4.29     | -0.233%                               |

| 134 | 2.77     | -1.818%                               | 125 | 4.63     | 0.0%                                  |

| 147 | 4.66     | -0.858%                               | 141 | 3.25     | 0.0% (N/A)                            |

|     |          |                                       | 145 | 3.89     | -0.514%                               |

|     |          |                                       | 146 | 3.85     | -0.239%                               |

**Table 1.4:** Error introduced by the use of sampling in a timing simulation. "IPC Full" columns report the instructions per cycle execution rate when no sampling is used. Also reported is the relative difference in IPC introduced by the use of sampling.

# Chapter 2

## **Memory Dependence Behavior Analysis**

Before we embark into describing possible applications of memory dependence prediction it is best if we develop an understanding of the memory dependence behavior of programs. Accordingly, in this chapter we present a characterization of memory dependence behavior. This information will aid us during both the motivation and the design process of the applications described in the chapters that follow. Hopefully, this information will also help stimulate other applications of memory dependence behavior than those we consider in this study. Moreover, there might be types of memory dependence information that might be interesting other than those we consider in this work (a description can be found in Section 2.3). Rather than performing an exhaustive analysis, we focus on those attributes that seem most relevant to a specific class of memory dependence predictors<sup>1</sup> (discussed in Section 2.2).