# EFFECTIVE COMPILE-TIME ANALYSIS FOR DATA PREFETCHING IN JAVA

A Dissertation Presented

by

**BRENDON D. CAHOON**

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

September 2002

Department of Computer Science

© Copyright by Brendon D. Cahoon 2002 All Rights Reserved

# EFFECTIVE COMPILE-TIME ANALYSIS FOR DATA PREFETCHING IN JAVA

A Dissertation Presented

by

**BRENDON D. CAHOON**

Approved as to style and content by:

Kathryn S. McKinley, Chair

J. Eliot B. Moss, Member

Charles C. Weems, Member

Russell G. Tessier, Member

W. Bruce Croft, Department Chair Department of Computer Science To my family, especially my wife Laura

## ACKNOWLEDGMENTS

I am deeply indebted to my advisor, Kathryn McKinley, for providing an enjoyable atmosphere for doing challenging research. I took her first class at UMass, and she has been stuck with me ever since. She has been an outstanding advisor and I am fortunate to have worked with her. I hope I am able to pass on her principles.

I thank Eliot Moss and Chip Weems for their leadership of our research group. They are very knowledgeable, and my discussions with them have improved this work significantly. They also served as members of my committee, and I appreciate their helpful comments and suggestions. Thanks also to Russ Tessier, my external committee member, for his careful reading of my dissertation and providing valuable feedback.

A special thanks goes to Fred Green and Arthur Chou, two excellent teachers that introduced me to research and encouraged me to go to graduate school.

I wish to thank all the members of the ALI research group over the years, especially Steve Blackburn, Jim Burrill, Steve Dropsho, Sharad Singhai, and Zhenlin Wang. Thanks also to many other friends in Amherst who made my time there enjoyable including Alan B., Matt K., Alan K., Ron P., Dan R., Matt S., and John W.

I have spent the last three years at the University of Texas. I would like to say thanks to J.C. Browne and Calvin Lin for hosting me while at UT. I have been fortunate to make many friends while at UT, including Emery Berger, Rich Cardone, Sam Guyer, Xianglong Huang, Daniel Jimenez, Ram Mettu, and Phoebe Weidmann. I could always count on them for stimulating discussions, some of which were actually about research.

I am very grateful to my family, especially my parents, for their support over the years. They are the ones that have made this work possible. Finally, I want to thank Laura for her support, patience, and love.

## ABSTRACT

# EFFECTIVE COMPILE-TIME ANALYSIS FOR DATA PREFETCHING IN JAVA

SEPTEMBER 2002

BRENDON D. CAHOON B.A., CLARK UNIVERSITY M.S., UNIVERSITY OF MASSACHUSETTS, AMHERST Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Kathryn S. McKinley

The memory hierarchy in modern architectures continues to be a major performance bottleneck. Many existing techniques for improving memory performance focus on Fortran and C programs, but memory latency is also a barrier to achieving high performance in object-oriented languages. Existing software techniques are inadequate for exposing optimization opportunities in object-oriented programs. One key problem is the use of high-level programming abstractions which make analysis difficult. Another challenge is that programmers use a variety of data structures, including arrays and linked structures, so optimizations must work on a broad range of programs. We develop a new unified data-flow analysis for identifying accesses to arrays and linked structures called recurrence analysis. Prior approaches that identify these access patterns are ad hoc, or treat arrays and linked structures independently. The data-flow analysis is intra- and inter-procedural, which is important in Java programs that use encapsulation to hide implementation details. We show Java programs that traverse arrays and linked structure have poor memory performance. We use compiler-inserted data prefetching to improve memory performance in these types of programs. The goal of prefetching is to hide latency by bringing data into the cache prior to a program's use of the data. We use our recurrence analysis to identify prefetching opportunities in Java programs. We develop a new algorithm for prefetching arrays, and we evaluate several methods for prefetching objects in linked structures. Since garbage collection is an integral part of Java, we evaluate the impact of a copying garbage collector on prefetching. We demonstrate how to improve the memory performance of the collector itself by using prefetching. This dissertation shows that a unified whole-program compiler analysis is effective in discovering prefetching opportunities in Java programs that traverse arrays and linked structures. Compiler-inserted data prefetching improves the memory performance even in the presence of object-oriented features that complicate analysis.

# TABLE OF CONTENTS

| CKNOWLEDGMENTS     |   |

|--------------------|---|

| BSTRACT            |   |

| IST OF TABLES      |   |

| ST OF FIGURES xiii | L |

## CHAPTER

| 1. | INT                      | RODU              | CTION 1                                                                                                                                |

|----|--------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1<br>1.2<br>1.3<br>1.4 | Prefetc<br>Organi | ching Arrays4ching Linked Structures6zation of Dissertation7ary of Contributions8                                                      |

| 2. | BAC                      | KGRO              | UND AND RELATED WORK 11                                                                                                                |

|    | 2.1<br>2.2               |                   | emory Hierarchy11ving Memory Performance13                                                                                             |

|    |                          | 2.2.1             | Tolerating Latency                                                                                                                     |

|    |                          |                   | 2.2.1.1       Prefetching       13         2.2.1.2       Multithreading       15         2.2.1.3       Out-of-order Execution       15 |

|    |                          | 2.2.2             | Program Transformations                                                                                                                |

|    | 2.3                      | Data-F            | low Analysis                                                                                                                           |

|    |                          | 2.3.1<br>2.3.2    | Intraprocedural Data-Flow Analysis18Interprocedural Data-Flow Analysis20                                                               |

|    | 2.4                      | Induct            | ion Variable Analysis                                                                                                                  |

|    | 2.5 |         | -           | iler Infrastructure                   |    |

|----|-----|---------|-------------|---------------------------------------|----|

|    | 2.6 | Prefete | ching: Rela | ated Work                             | 24 |

|    |     | 2.6.1   | •           | efetching in Software                 |    |

|    |     | 2.6.2   | -           | efetching in Hardware                 |    |

|    |     | 2.6.3   | •           | efetching on Multiprocessors          |    |

|    |     | 2.6.4   |             | ing Linked Structures: Luk and Mowry  |    |

|    |     | 2.6.5   | Other Li    | nked-Structure Prefetching Techniques | 31 |

| 3. | DAT | A-FLO   | W ANAL      | YSIS FOR IDENTIFYING RECURRENCES      | 38 |

|    | 3.1 | Loop l  | Induction V | Variables                             | 38 |

|    | 3.2 | Linke   | l Data Stru | ictures                               | 39 |

|    | 3.3 | A Uni   | fied Analy  | sis                                   | 39 |

|    |     | 3.3.1   | Basic int   | raprocedural analysis                 | 40 |

|    |     | 3.3.2   | Intraproc   | cedural Examples                      | 44 |

|    |     | 3.3.3   | Interproc   | cedural Algorithm                     | 48 |

|    |     | 3.3.4   | Interproc   | cedural Example                       | 51 |

|    |     | 3.3.5   | 5           | ields and Arrays                      |    |

|    |     | 3.3.6   | Indirect l  | Recurrent Variables                   | 55 |

|    | 3.4 | Coope   | rating Ana  | llyses                                | 56 |

|    |     | 3.4.1   | Shared C    | Dbject Analysis                       | 56 |

|    |     | 3.4.2   | Array Siz   | ze Analysis                           | 60 |

|    | 3.5 | Chapte  | er Summar   | ry                                    | 64 |

| 4. | PRE | EFETCI  | H TECHN     | NIQUES                                | 66 |

|    | 4.1 | Array   | Prefetchin  | g                                     | 66 |

|    |     | 4.1.1   | Mowry's     | Prefetch Algorithm                    | 67 |

|    |     | 4.1.2   | •           | etch Algorithm                        |    |

|    | 4.2 | Greed   | y Prefetchi | ng                                    | 73 |

|    |     | 4.2.1   | Intraproc   | cedural Greedy Prefetch Scheduling    | 74 |

|    |     | 4.2.2   | -           | cedural Greedy Prefetch Scheduling    |    |

|    | 4.3 | Jump-   | Pointer Pre | efetching                             | 79 |

|    |     | 4.3.1   | Creating    | Jump-Pointers                         | 80 |

|    |     |         | 4.3.1.1     | Object Creation                       | 84 |

|    |     |         | 4.3.1.2     | Traversal                             |    |

|    |     | 4.3.2<br>4.3.3 |             | Jump-Pointers   Collection     |     |

|----|-----|----------------|-------------|--------------------------------|-----|

|    | 4.4 | Stride         | Prefetchin  | ıg                             | 86  |

|    | 4.5 |                |             | in Vortex                      |     |

|    |     | 4.5.1<br>4.5.2 |             | cedural Analysis               |     |

|    |     |                | 4.5.2.1     | High-Level Optimization        | 92  |

|    |     |                | 4.5.2.2     | Low-Level Optimization I       | 94  |

|    |     |                | 4.5.2.3     | Low-Level Optimization II      | 95  |

|    |     |                | 4.5.2.4     | Code Generation                | 95  |

|    |     | 4.5.3          | Impleme     | entation of Prefetching        | 96  |

|    | 4.6 | Chapte         | er Summai   | ry                             | 98  |

| 5. | EXI | PERIM          | ENTAL R     | ESULTS                         | 100 |

|    | 5.1 | Metho          | dology      |                                | 101 |

|    | 5.2 |                |             | g                              |     |

|    |     | 5.2.1          | Prefetch    | Effectiveness                  | 107 |

|    |     | 5.2.2          |             | tatistics                      |     |

|    |     | 5.2.2          |             | Misses                         |     |

|    |     | 5.2.4          |             | the Prefetch Distance          |     |

|    |     | 5.2.5          |             | dy: Matrix Multiplication      |     |

|    |     | 5.2.6          |             | ltidimensional Arrays          |     |

|    |     | 5.2.7          |             | al Prefetch Opportunities      |     |

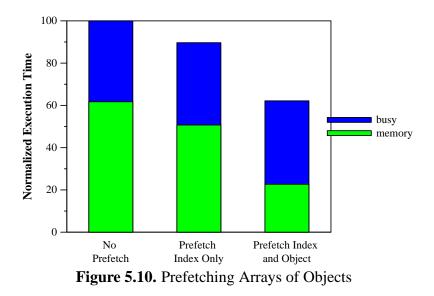

|    |     |                | 5.2.7.1     | Arrays of Objects              | 119 |

|    |     |                | - · · · ·   | Enumeration Class              |     |

|    | 5.3 | Linked         | l-Structure | e Prefetching                  | 121 |

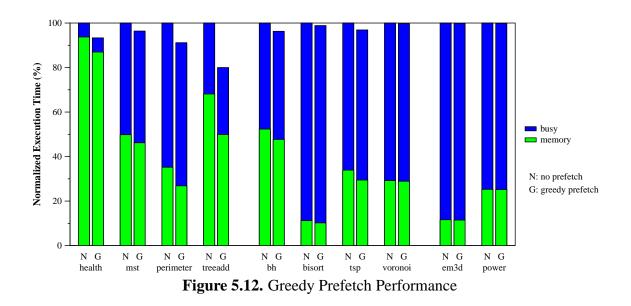

|    |     | 5.3.1          | Greedy I    | Prefetching                    | 122 |

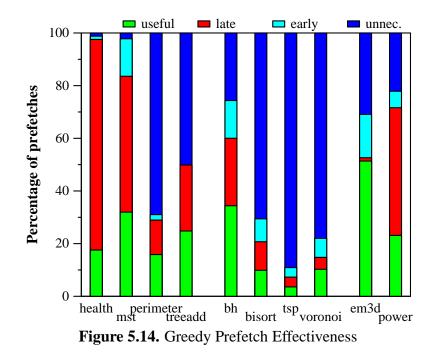

|    |     |                | 5.3.1.1     | Prefetch Effectiveness         | 124 |

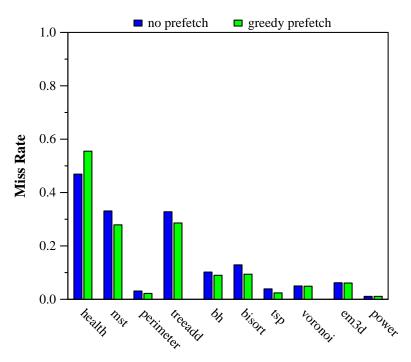

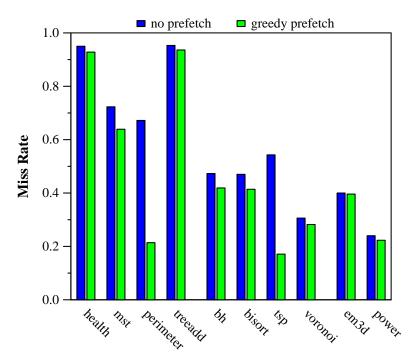

|    |     |                | 5.3.1.2     | Cache Statistics               |     |

|    |     |                | 5.3.1.3     | Analysis Features              | 126 |

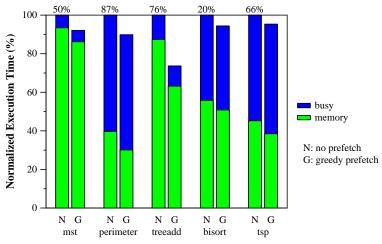

|    |     |                | 5.3.1.4     | Individual Program Performance |     |

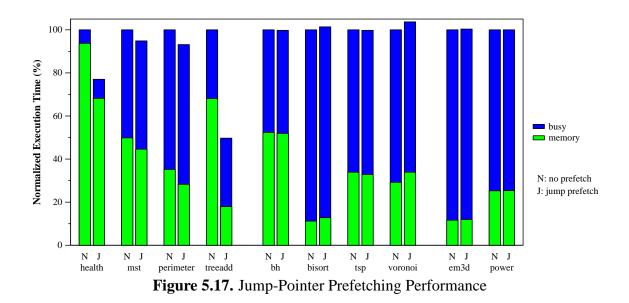

|    |     | 5.3.2          | Jump-Po     | vinter Prefetching             | 132 |

|    |     |                | 5.3.2.1     | Prefetch Effectiveness         | 134 |

|    |     |                | 5.3.2.2     | Cache Statistics               | 135 |

|    |     |                |             |                                |     |

|    |            |                                  | 5.3.2.3                | Individual program performance                                         |  |

|----|------------|----------------------------------|------------------------|------------------------------------------------------------------------|--|

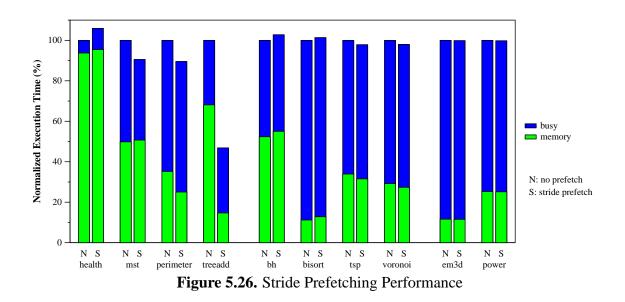

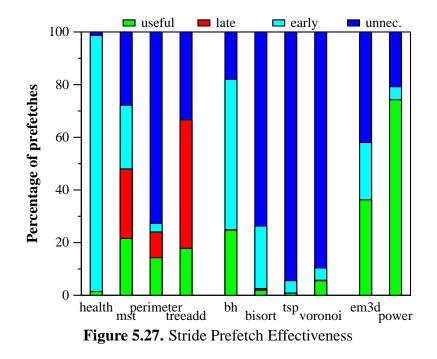

|    |            | 5.3.3                            | Stride Pre             | fetching                                                               |  |

|    |            |                                  | 5.3.3.1                | Individual Program Performance                                         |  |

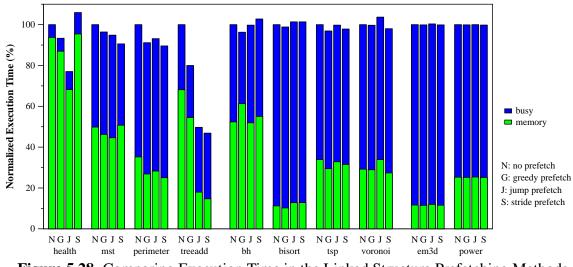

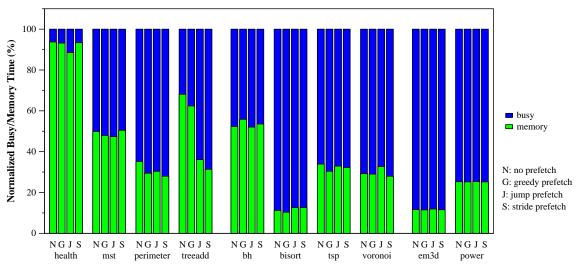

|    |            | 5.3.4                            | Summary                | of Prefetching Linked Structures                                       |  |

|    | 5.4        | Archit                           | ectural Sens           | sitivity                                                               |  |

|    |            | 5.4.1<br>5.4.2<br>5.4.3<br>5.4.4 | Greedy Pr<br>Jump-Poin | fetching<br>refetching<br>nter Prefetching<br>ural Sensitivity Summary |  |

|    | 5.5        | Chapte                           | er Summary             | 7                                                                      |  |

| 6. | GAI        | RBAGE                            | COLLEC                 | TION AND PREFETCHING                                                   |  |

|    | 6.1<br>6.2 |                                  | 0                      | on in Vortex                                                           |  |

|    |            | 6.2.1<br>6.2.2                   | 0                      | Jump-Pointers in the Collector                                         |  |

|    | 6.3<br>6.4 |                                  | -                      | Garbage Collector                                                      |  |

| 7. | COI        | NCLUS                            | IONS                   |                                                                        |  |

|    | 7.1<br>7.2 |                                  |                        |                                                                        |  |

|    |            |                                  |                        |                                                                        |  |

# LIST OF TABLES

| Table | e Page                                                                                    |

|-------|-------------------------------------------------------------------------------------------|

| 5.1   | Simulation Parameters                                                                     |

| 5.2   | Array-based Benchmark Programs                                                            |

| 5.3   | Array Static and Dynamic Prefetch Statistics                                              |

| 5.4   | Effect of Prefetch Distance on Prefetching (Execution Times Normalized to No Prefetching) |

| 5.5   | Linked-Structure Benchmark Suite                                                          |

| 5.6   | Benchmark Program Statistics                                                              |

| 5.7   | Greedy Static and Dynamic Prefetch Statistics                                             |

| 5.8   | Static Greedy Prefetch Statistics                                                         |

| 5.9   | Jump-Pointer Prefetch Statistics                                                          |

| 5.10  | Different Simulation Configurations                                                       |

| 5.11  | Overall Results for Array Prefetching                                                     |

| 5.12  | Overall Results for Greedy Prefetching                                                    |

| 5.13  | Overall Results for Jump-Pointer Prefetching                                              |

# **LIST OF FIGURES**

| Figu | re Page                                                      |

|------|--------------------------------------------------------------|

| 1.1  | Memory Penalty in Array-based Java Programs                  |

| 1.2  | Memory Penalty in Java Programs Containing Linked Structures |

| 3.1  | Similarities Between Array and Linked-Structure Traversals   |

| 3.2  | Recurrence Analysis Example: Traversing a List               |

| 3.3  | Recurrence Analysis Example: Traversing an Array             |

| 3.4  | Recurrence Analysis Example: Kill Data-Flow Information      |

| 3.5  | Recurrence Analysis Example: Traversing a List Conditionally |

| 3.6  | Recurrence Analysis Example: Complex Induction Variable      |

| 3.7  | Examples Showing Need for IP analysis                        |

| 3.8  | Using Calling Context Information                            |

| 3.9  | IP Recurrence Analysis Example: Recursion                    |

| 3.10 | Assigning Recurrence Information to a Field                  |

| 3.11 | Example of Indirect Recurrent Variable                       |

| 3.12 | Object Sharing                                               |

| 3.13 | Using an Array to Represent an Oct-tree                      |

| 4.1  | Simple Index Expression                                      |

| 4.2  | Original Loop                                                |

| 4.3  | Unrolled Loop                                        | 69 |

|------|------------------------------------------------------|----|

| 4.4  | Loop After Transformations                           | 69 |

| 4.5  | Complex Index Expression                             | 70 |

| 4.6  | Array of Objects                                     | 70 |

| 4.7  | Array Scheduling Algorithm                           | 71 |

| 4.8  | Redundant Prefetch Example                           | 72 |

| 4.9  | Prefetching a Singly Linked List                     | 73 |

| 4.10 | Prefetching a Binary Tree                            | 73 |

| 4.11 | Redundant Greedy Prefetch Example                    | 75 |

| 4.12 | Intraprocedural Greedy Prefetch Scheduling Algorithm | 76 |

| 4.13 | Greedy Prefetching on an Oct-tree                    | 77 |

| 4.14 | Naive Interprocedural Prefetch Scheduling            | 78 |

| 4.15 | Jump-Pointer Prefetching: Binary Tree Traversal      | 80 |

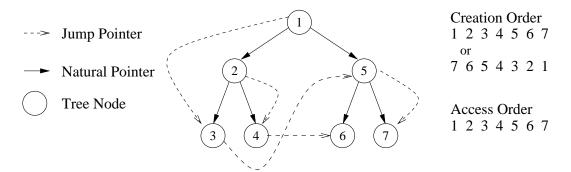

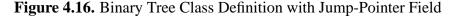

| 4.16 | Binary Tree Class Definition with Jump-Pointer Field | 81 |

| 4.17 | Inserting Jump-Pointers for a Binary Tree            | 81 |

| 4.18 | Sparc Assembly for Creating Jump-Pointers            | 83 |

| 4.19 | Creating Jump-Pointers                               | 84 |

| 4.20 | Example: Indirect Jump-Pointer                       | 85 |

| 4.21 | Example of Stride Prefetching                        | 87 |

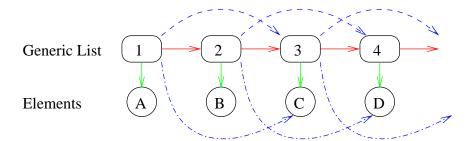

| 4.22 | Overview of the Vortex Compiler: With Our Extensions | 89 |

| 4.23 | Example of Prefetch Optimization in Vortex           | 96 |

| 4.24 | Class Hierarchy for Prefetching                      | 97 |

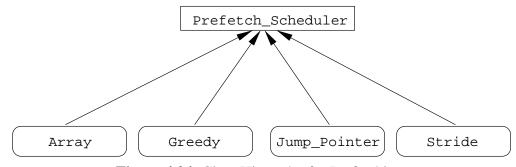

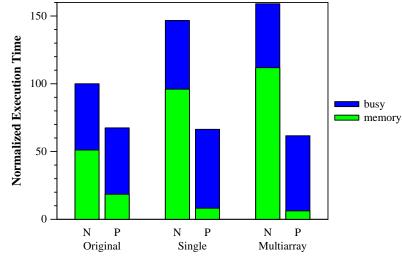

| 5.1  | Array Prefetching Performance                                        |

|------|----------------------------------------------------------------------|

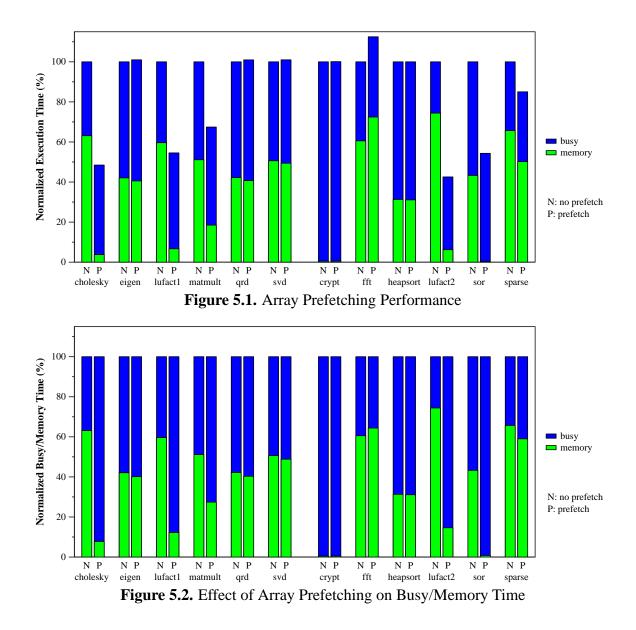

| 5.2  | Effect of Array Prefetching on Busy/Memory Time 105                  |

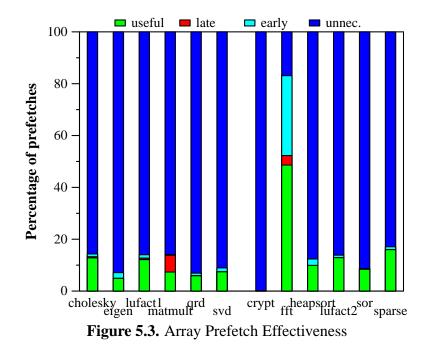

| 5.3  | Array Prefetch Effectiveness                                         |

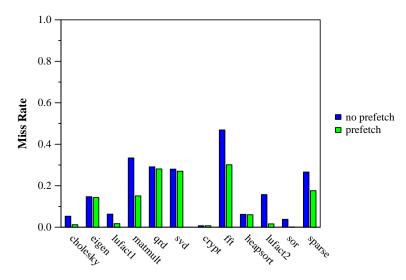

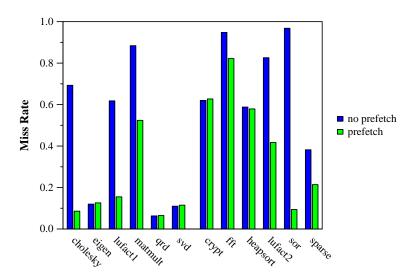

| 5.4  | L1 Cache Miss Rate (Array Prefetching) 110                           |

| 5.5  | L2 Cache Miss Rate (Array Prefetching) 110                           |

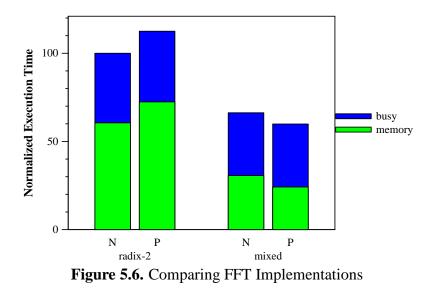

| 5.6  | Comparing FFT Implementations                                        |

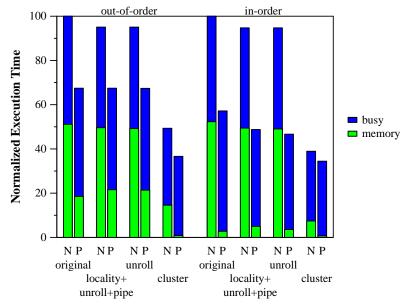

| 5.7  | Applying Different Loop Transformations to Matrix Multiplication 115 |

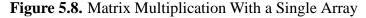

| 5.8  | Matrix Multiplication With a Single Array 118                        |

| 5.9  | Performance of Prefetching on True Multidimensional Arrays 118       |

| 5.10 | Prefetching Arrays of Objects                                        |

| 5.11 | Using the Enumeration Class                                          |

| 5.12 | Greedy Prefetch Performance                                          |

| 5.13 | Traversal Phase Performance (Greedy Prefetching)                     |

| 5.14 | Greedy Prefetch Effectiveness                                        |

| 5.15 | L1 Miss Rate (Greedy Prefetching)                                    |

| 5.16 | L2 Miss Rate (Greedy Prefetching)                                    |

| 5.17 | Jump-Pointer Prefetching Performance                                 |

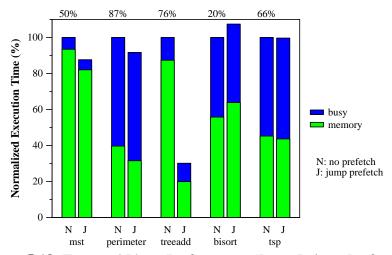

| 5.18 | Traversal Phase Performance (Jump-Pointer Prefetching) 134           |

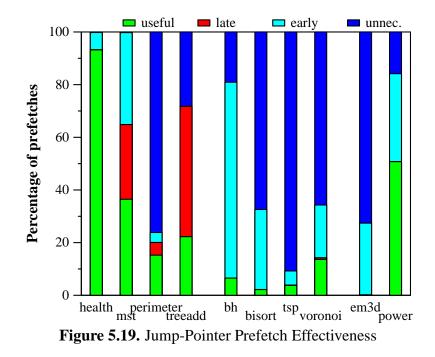

| 5.19 | Jump-Pointer Prefetch Effectiveness                                  |

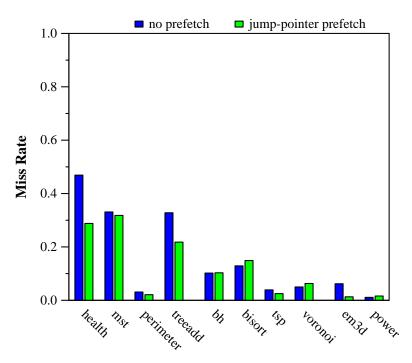

| 5.20 | L1 Miss Rate (Jump-Pointer Prefetching)                              |

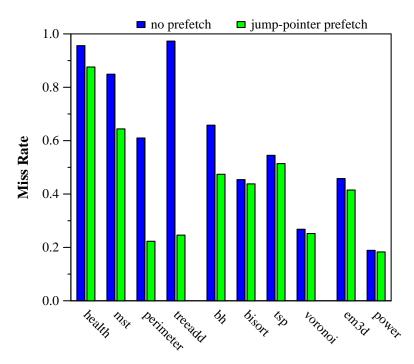

| 5.21 | L2 Miss Rate (Jump-Pointer Prefetching)                              |

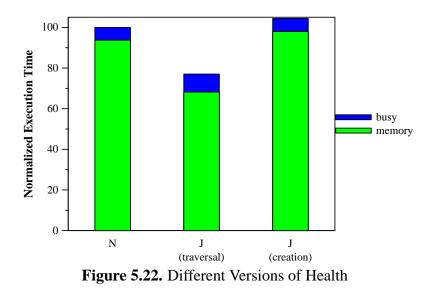

| 5.22 | Different Versions of Health                                         |

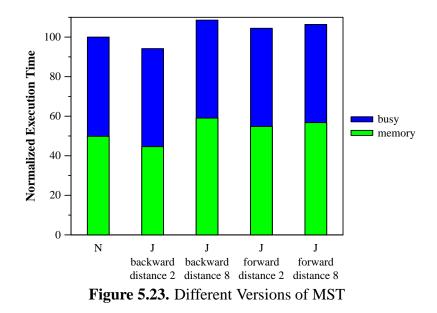

| 5.23 | Different Versions of MST                                            |

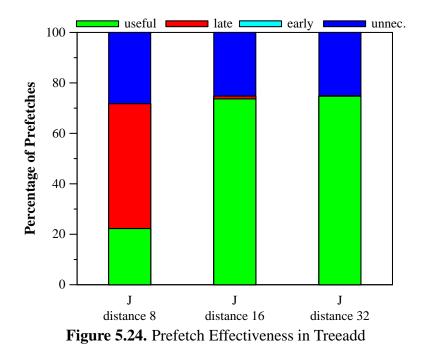

| 5.24 | Prefetch Effectiveness in Treeadd                                              |

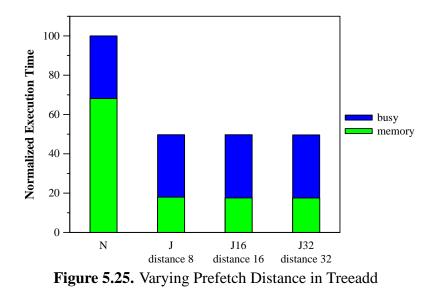

|------|--------------------------------------------------------------------------------|

| 5.25 | Varying Prefetch Distance in Treeadd                                           |

| 5.26 | Stride Prefetching Performance                                                 |

| 5.27 | Stride Prefetch Effectiveness                                                  |

| 5.28 | Comparing Execution Time in the Linked Structure Prefetching Methods 147       |

| 5.29 | Comparing Busy/Memory Time in the Linked Structure Prefetching<br>Methods      |

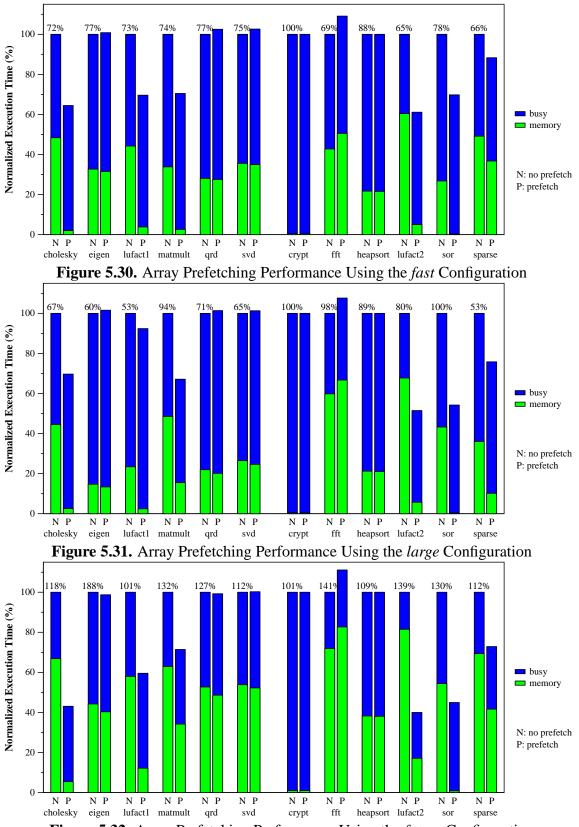

| 5.30 | Array Prefetching Performance Using the <i>fast</i> Configuration              |

| 5.31 | Array Prefetching Performance Using the <i>large</i> Configuration             |

| 5.32 | Array Prefetching Performance Using the <i>future</i> Configuration            |

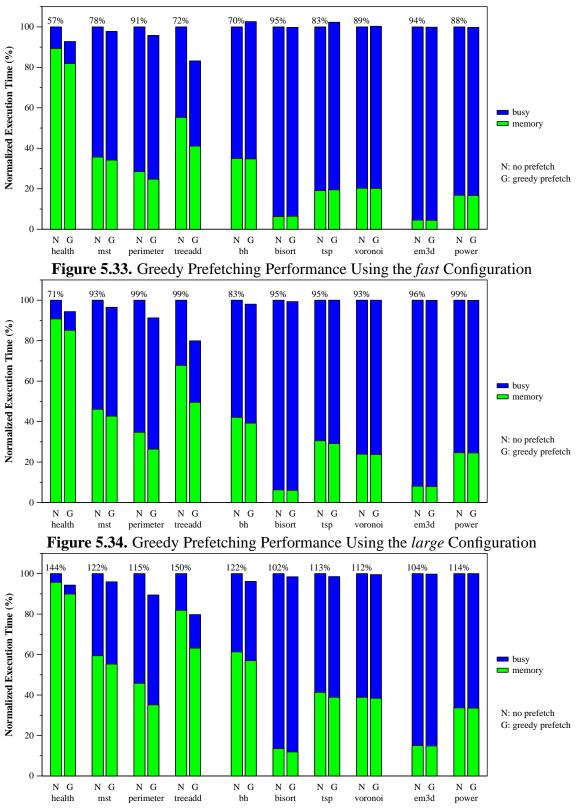

| 5.33 | Greedy Prefetching Performance Using the <i>fast</i> Configuration             |

| 5.34 | Greedy Prefetching Performance Using the <i>large</i> Configuration            |

| 5.35 | Greedy Prefetching Performance Using the <i>future</i> Configuration           |

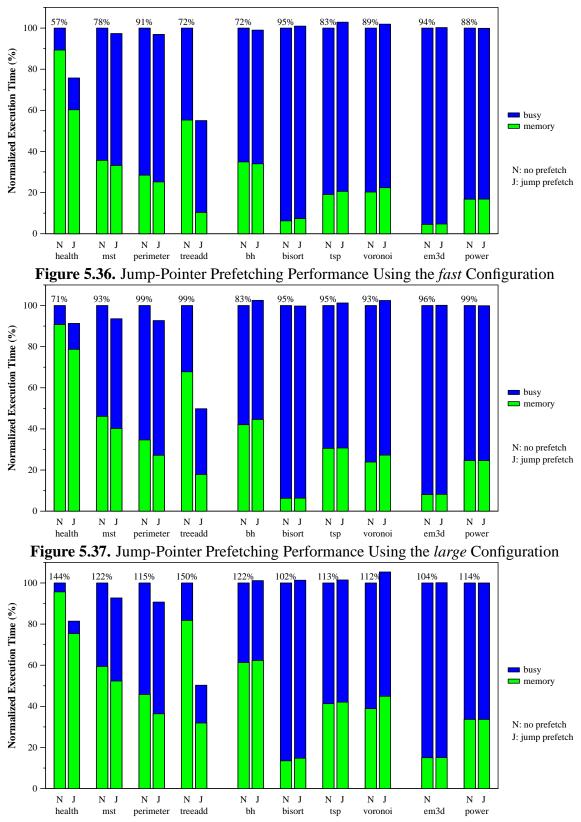

| 5.36 | Jump-Pointer Prefetching Performance Using the <i>fast</i> Configuration 154   |

| 5.37 | Jump-Pointer Prefetching Performance Using the <i>large</i> Configuration 154  |

| 5.38 | Jump-Pointer Prefetching Performance Using the <i>future</i> Configuration 154 |

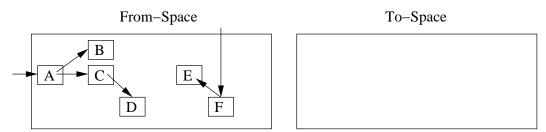

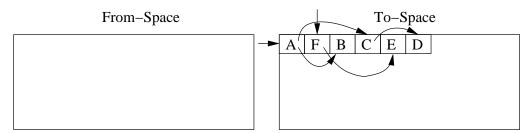

| 6.1  | The Heap at the Start of a Collection                                          |

| 6.2  | The Heap at the End of a Collection                                            |

| 6.3  | Cheney's Algorithm (from Jones and Lin [52]) 158                               |

| 6.4  | Snapshot of Cheney's Copying Algorithm                                         |

| 6.5  | Extended to Cheney's Algorithm to Handle Jump-Pointers                         |

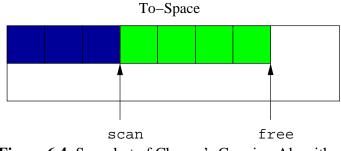

| 6.6  | Performance with Garbage Collection                             |

|------|-----------------------------------------------------------------|

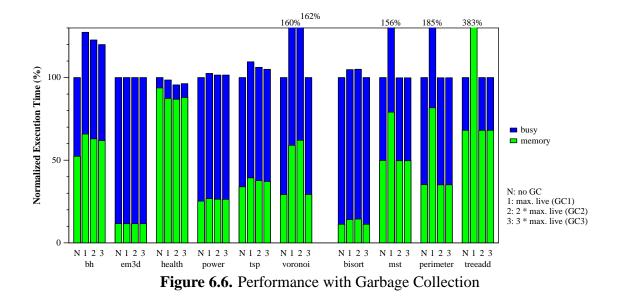

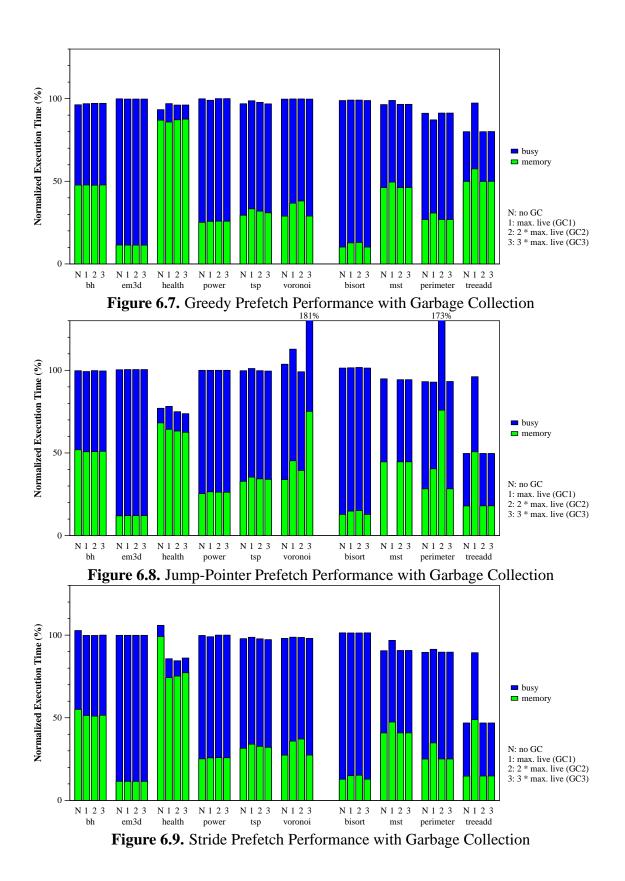

| 6.7  | Greedy Prefetch Performance with Garbage Collection             |

| 6.8  | Jump-Pointer Prefetch Performance with Garbage Collection       |

| 6.9  | Stride Prefetch Performance with Garbage Collection             |

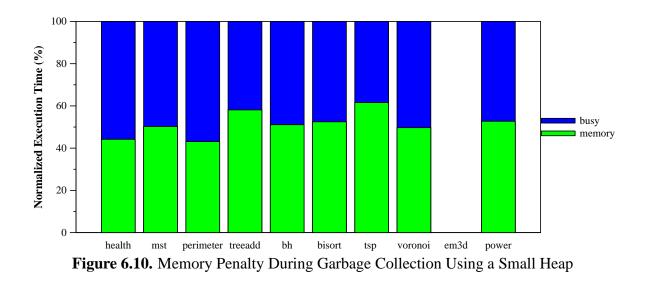

| 6.10 | Memory Penalty During Garbage Collection Using a Small Heap 167 |

| 6.11 | Prefetching in To-Space                                         |

| 6.12 | Prefetching in From-Space                                       |

| 6.13 | Prefetching Fields During the Object Scan                       |

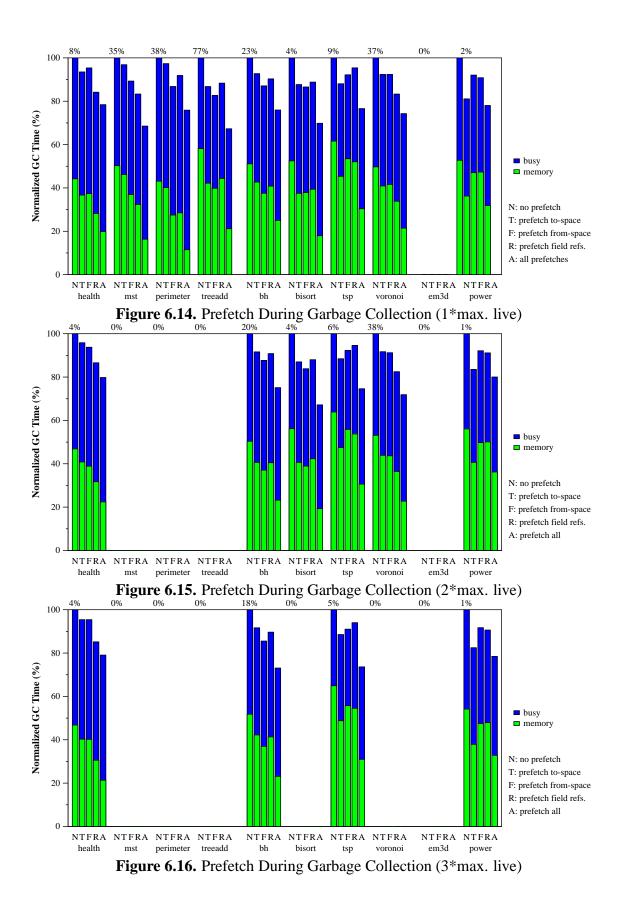

| 6.14 | Prefetch During Garbage Collection (1*max. live)                |

| 6.15 | Prefetch During Garbage Collection (2*max. live)                |

| 6.16 | Prefetch During Garbage Collection (3*max. live)                |

# CHAPTER 1 INTRODUCTION

We develop an effective compile-time analysis that discovers and exploits data prefetch opportunities to improve memory performance in Java programs that use arrays and linked structures.

Increases in modern processor speed continue to outpace advances in memory speed resulting in an underutilization of hardware resources due to memory bottlenecks. Schemes for reducing or tolerating memory latency are necessary to achieve high performance in modern computer systems. Most commercial architectures use multiple level cache hierarchies to alleviate memory bottlenecks. Caches improve memory performance by allowing quick access to a small amount of frequently used data. Caches work because programs exhibit locality of reference. Unfortunately, increases in data set sizes and the increasing disparity between the processor and memory speeds limit the performance of many workloads.

Researchers have performed a significant amount of work investigating techniques, including compiler support, to improve the *effectiveness* of caches. These include data and code transformations to improve the data reuse in the cache. Compile-time program transformations require complex static analysis in order to determine when transformations are profitable and legal. Compilers must be conservative when making optimization decisions and will not transform a program if sufficient information is either unavailable or not computable.

Another technique for improving memory performance is data prefetching which attempts to *tolerate* cache latency. The goal of prefetching is to bring data into the cache prior to the use of that data. The key to effective prefetching is to determine *what* to prefetch and *when* to issue a prefetch. Determining prefetching opportunities may be done by hardware or software techniques. Hardware prefetching detects run-time access patterns using additional hardware resources to determine appropriate data to prefetch. Software methods require compiler support to generate additional instructions for prefetching data. Software data prefetching has several advantages over hardware-only schemes. The hardware complexity of implementing a prefetch instruction is much less than the complexity of a complete hardware prefetching implementation. A software prefetch instruction is more flexible. Programs can choose exactly when to issue prefetches and what to prefetch. For example, a hardware mechanism may prefetch floating point data only, whereas software methods can prefetch data of any type. Compilers provide a method to generate software prefetches automatically. Hardware methods typically ignore program structure, which results in an increase in memory traffic by issuing superfluous prefetches.

Most existing techniques for improving memory performance using prefetching focus on Fortran and C programs. Memory latency is a barrier to achieving high performance in Java programs as well. The software engineering benefits of object-oriented languages encourage programmers to use Java to implement a wide variety of programs, including those that require high performance. Traditional techniques for improving memory performance are difficult to apply to object-oriented languages. Software engineering practices make compile-time analysis of object-oriented programs difficult. For example, objectoriented programming encourages the use of encapsulation and small methods, both of which complicate compile-time analysis. Overcoming the challenges that software engineering practices introduce requires whole program analysis.

Programmers frequently use arrays and linked structures in Java programs. For example, the underlying data structure for several Java core library classes, such as java-.util.Stack, is an array. New versions of Java include library support for container classes that use linked structures, such as java.util.LinkedList. We believe that it is important for compilers to analyze and optimize both arrays and linked structures. Prior techniques focus on optimizing one or the other, but not both.

To improve the memory performance of object-oriented programs, we investigate software controlled data prefetching to improve memory performance by tolerating cache miss latency. We develop and implement a new data-flow analysis to identify traversal patterns in arrays and linked structures. The analysis is unique because it presents a single framework for identifying prefetching opportunities in array-based and pointer-based codes. We believe the data-flow analysis will be useful in other domains, such as data layout optimization. We describe and evaluate a compiler implementation of a new compiler technique for prefetching arrays, and three methods for prefetching linked structures in Java. Our unified framework is able to identify array and linked structure traversals that occur across method boundaries. We demonstrate that our new array prefetching technique is able to improve memory performance significantly. Prefetching linked structures in Java programs is effective also, but there is still room for improvement.

Java uses garbage collection to manage dynamic memory allocation automatically. Since Java requires garbage collection, we examine the impact of garbage collection on prefetching. We investigate generational copying garbage collectors specifically. Since a copying collector reorganizes data, there is synergy between prefetching and the collector. We investigate the potential for using the collector to improve prefetching. We also show that our copying collector has poor memory performance, so we evaluate the effectiveness of adding prefetch instructions to improve the performance of the collector itself.

We organize the rest of this section as follows. Section 1.1 introduces array prefetching. Section 1.2 introduces linked-structure prefetching. We summarize our unified dataflow analysis that detects prefetch opportunities for both arrays and linked structures. Section 1.3 describes the organization of the dissertation. Finally, we summarize our contributions in Section 1.4.

## **1.1 Prefetching Arrays**

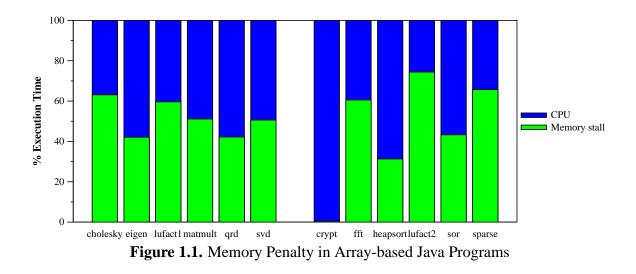

Programmers are using Java increasingly to solve programming problems that require high performance, including those involving matrix computations. Poor memory efficiency limits the performance of Java programs just as it does for C and Fortran. Over half the programs in Figure 1.1 spend more than 50% of time waiting for memory on a simulated out-of-order superscalar processor. We obtain these measurements by compiling the programs using Vortex [34], an ahead-of-time compiler, and running them on RSIM [84], an execution driven simulator. Figure 1.1 illustrates that there is significant room for improvement in these Java programs.

Traditional approaches for improving memory performance in array-based applications use loop transformations, such as tiling and unrolling [64, 73]. Implementing loop transformations in Java compilers is challenging due to the semantics of Java arrays and exceptions [9]. Java multidimensional arrays present challenges because the language specifies them as arrays-of-arrays. As a result, it is not possible to compute the address of any element directly. In a true multidimensional array, such as in Fortran, it is possible to compute the address of any element relative to the start of the array. The Java language specification requires precise exceptions, which means that all statements appearing before an exception must complete, and that the result of any statement appearing after an exception cannot appear to have completed [43]. Optimizations must be careful not to violate this property so compilers often do not transform code that occurs in exception handlers.

We develop a simple, yet effective method for prefetching array references that contain induction variables in the index expression. An induction variable is incremented or decremented by the same value during each loop iteration. We detect the induction variables using an analysis that is able to detect general recurrences, including those involving linked structures. We formalize the recurrence analysis as a data-flow problem. Prior approaches are ad hoc, or focus on either arrays or linked structures, but cannot detect both.

We evaluate array prefetching using benchmark programs from the Jama library [46] and the Java Grande benchmark suite [14]. Our results show that our simple prefetching implementation is very effective on array-based Java programs on an aggressive out-of-order processor. Prefetching reduces the execution time by a geometric mean<sup>1</sup> of 23%, and the largest reduction is 58%. We see large improvements on several kernels, include matrix multiplication, LU factorization, SOR, and Cholesky factorization. In SOR, prefetching eliminates all memory stalls and reduces execution time by 46%. Performance degrades in one program, FFT, because of a large number of conflict misses caused by a power of 2 data layout and access of a large 1-D array that make prefetching counterproductive.

We augment these results with a case study of matrix multiplication to explore the utility of additional loop transformations to schedule prefetches more carefully in the spirit of the previous work by Mowry et al. [79]. We find that prefetching on modern architectures is less sensitive to precise scheduling via loop transformations, but loop transformations may provide further improvements in some cases. The additional functional units and outof-order execution in modern processors are able to hide the cost of superfluous prefetch instructions.

<sup>&</sup>lt;sup>1</sup>We use the geometric mean because we compute the mean of normalized execution times.

Our technique is much simpler and faster than existing array software prefetching techniques because it does not require array dependence testing or loop transformations. These characteristics make it suitable for a just-in-time (JIT) compiler, but we leave that evaluation for future work.

## 1.2 Prefetching Linked Structures

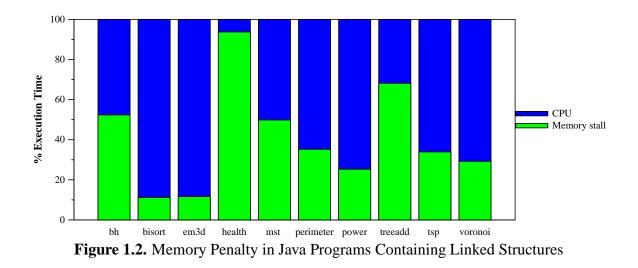

The memory penalty can also be high for object-oriented programs that frequently traverse linked data structures. Figure 1.2 illustrates the percentage of time spent servicing memory requests in an object-oriented Java implementation of the Olden benchmark suite [17]. We compile the programs using Vortex, an ahead-of-time compiler. Memory stalls account for 15% to 95% of the execution time running on RSIM.

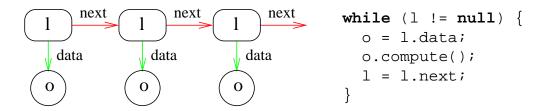

Prefetching linked structures is difficult because distinct dynamically allocated objects are not necessarily contiguous in memory, and the access patterns in memory may be unpredictable or erratic. Given an object o, we know the address of objects that o references, and we cannot prefetch other objects without following pointer chains. Recent pointer prefetching work considers C programs only [66, 70, 90, 56, 101]. Object-oriented Java programs pose additional analysis challenges because they mostly allocate data dynamically, contain frequent method invocations, and often implement loops with recursion. Linked structure traversals are similar to induction variables. A statement in each loop iteration updates an object by the same field expression, e.g., o = o.next. A simple extension to the data-flow analysis for discovering induction variables enables the recurrence analysis to recognize linked structures also. Thus we can use the same unified analysis to discover prefetch opportunities in linked structures and arrays.

Our results show that compile-time prefetching is effective on object-oriented programs that contain linked structures. We find that object-oriented programs often cross procedure boundaries during linked structure traversals. The recurrence analysis is successful in detecting most traversal patterns in the presence of encapsulation and recursion. Our compiler generates prefetch instructions wherever the program traverses a linked structure. We implement three prefetch techniques: greedy, jump-pointer, and stride prefetching, which reduce run time by a geometric mean of 5%, 10%, and 9%, respectively. Greedy prefetching inserts prefetches for directly connected objects. Jump-pointer prefetching uses a compiler-added field to prefetch objects further away in a linked structure. Stride prefetching, memory latency is still a problem, so future work should combine other techniques with prefetching.

#### **1.3** Organization of Dissertation

We organize the remainder of this dissertation as follows. In Chapter 2, we describe background material and discuss the related work. We present a basic overview of the memory hierarchy, and several methods for improving memory performance. We also present the foundations for the static analysis techniques that we use in our compiler. At the end of the chapter, we discuss the related work in data prefetching separately.

Chapter 3 describes our recurrence analysis. The analysis discovers loop induction variables and linked structure traversals. We first define our intraprocedural analysis and

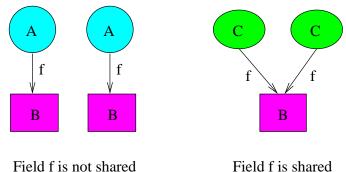

then our interprocedural analysis. We present extensions to the basic analysis to handle assignment of data-flow information to object fields and arrays. We also describe two other data-flow analyses that improve our prefetching techniques. These analyses compute array sizes and determine which object fields are shared or unshared.

Chapter 4 presents the prefetch algorithms. We first describe our array prefetching implementation. Our prefetch algorithm does not require loop transformations, or expensive data dependence analysis. Then, we describe greedy, jump-pointer, and stride prefetching for linked structures. We show how we use the recurrence analysis to determine *what* to prefetch, and show how the different prefetch algorithms determine *when* to generate prefetch instructions. Chapter 4 also describes the details of our compiler implementation.

In Chapter 5, we evaluate the prefetch algorithms. We compile Java programs using Vortex [34], an ahead of time compiler that produces SPARC assembly, with and without prefetching, to compare the performance benefits directly. We run the programs on RSIM [84], a simulator for an aggressive out-of-order superscalar processor, to obtain detailed performance statistics. We evaluate Java programs from the Olden [17], Jama [46], and Java Grande [14] benchmark suites.

In Chapter 6, we turn on garbage collection and evaluate the effect of garbage collection on prefetching. We run experiments using different heap sizes, and discuss the effect of garbage collection on prefetching. We show that memory performance during the garbage collection phase is very poor. To improve the performance of the collector, we add prefetch instructions at different steps during the collection algorithm. We show that prefetching can help improve the memory performance of garbage collection as well.

Finally, Chapter 7 provides a summary of the contributions in this dissertation. We also discuss directions for future work.

## **1.4 Summary of Contributions**

We make the following contributions in this dissertation:

- We develop a new method for detecting recurrences in programs. We detect recurrences in linked structures and indices of array references. Our approach uses interprocedural and intraprocedural data-flow analysis. We do not require explicit definition-use chains or for the program to be in static single assignment (SSA) form. Our analysis unifies the discovery of recurrences in linked structures and arrays. We apply the analysis to compiler-generated data prefetching, but we believe that compilers can use the analysis in other domains, such as data layout optimization.

- 2. We develop a new technique for prefetching arrays. We prefetch arrays that use induction variables. We do not require array dependence analysis or loop transformations. We evaluate prefetching on a set of scientific Java programs. Our array prefetching technique reduces the execution time by more than 15% in 6 of the 12 programs from the Jama library and Java Grande benchmark suite.

- 3. We implement a new compiler technique for linked-structure prefetching in Java programs. We implement three prefetching algorithms: greedy prefetching, jump-pointer prefetching, and stride prefetching. We find that interprocedural analysis is necessary to discover many of the important linked structure accesses. Our results show that jump-pointer prefetching is able to achieve the largest performance improvements, but may degrade performance if the compiler is not careful when creating the jump-pointers. Stride prefetching produces results similar to jump-pointer prefetching, but the results depend on the layout of the linked structures. Greedy prefetching produces the smallest improvements, but does not increase the execution time in any of the programs.

- 4. We evaluate the effect of prefetching on garbage collection. The Vortex run-time system uses a generational copying garbage collector. The data reorganization that the collector performs potentially affects the performance of the linked-structure pre-fetching methods. We quantify the effect using the Olden benchmarks. We also show

that memory performance during garbage collection is consistently poor. We add prefetch instructions to the collection algorithm, and show that prefetching can reduce the execution time of the collector.

We believe that it is important for compilers to analyze and optimize both arrays and linked structures in Java programs. We develop a unified whole-program data-flow analysis for identifying recurrences and inserting prefetches in Java programs. We show that our data prefetching algorithm is effective in improving the memory performance of Java programs.

## **CHAPTER 2**

## **BACKGROUND AND RELATED WORK**

In this chapter, we provide background material and discuss related work. We organize the chapter as follows. In Section 2.1, we describe the memory subsystem of many modern computer architectures. A main focus of this dissertation is to improve performance by reducing the memory penalty in programs. Section 2.2 discusses existing techniques for improving memory performance. We describe methods for tolerating latency and program transformations to utilize the cache more effectively. Our approach uses static analysis to reason about programs and obtain information to optimize programs. The specific type of static analysis is data-flow analysis. Section 2.3 describes the foundations of interprocedural and intraprocedural data-flow analysis. We develop a data-flow analysis that generalizes the detection of induction variables. We present related work for induction variable analysis in Section 2.4. Section 2.5 summarizes the compiler infrastructure that we use to implement and evaluate our optimization techniques. The specific technique we use to improve memory performance is data prefetching. We discuss the related work for prefetching in Section 2.6.

#### 2.1 The Memory Hierarchy

Over the last few decades, a substantial amount of research has focused on cache design and improving their effectiveness [97]. There are several reasons that researchers continue to investigate new techniques to improve cache effectiveness. The gap between processor and memory speed continues to grow, so it is increasingly important to develop methods to reduce the impact of the growing gap. We continue to see programs that spend a large fraction of time waiting for memory.

Modern computer architectures contain deep memory hierarchies to achieve high performance. The memory hierarchies contain multiple levels of cache that maintain recently accessed data. The ability to keep data in a cache is crucial to achieving high performance. There is a delicate balance between the cache size and access time. The access time to the cache at level l is faster than the cache at level l + 1, but the cache size of level l is smaller than the cache size of level l + 1. As processor speed continues to increase, first level caches must remain small in order to achieve one or two cycle access times.

Caches improve performance by taking advantage of data locality, which is the property that programs tend to access the same memory location or nearby locations frequently within a short time period. The two general classifications of data locality are *temporal* and *spatial* locality. Temporal locality occurs when one or more statements reference the same data at different times, and spatial locality occurs when one or more statements reference nearby memory locations.

A cache is divided into fixed sized blocks, called *cache lines*. The cache lines are grouped into sets. The number of cache lines in a set specifies the *associativity* of the cache. A cache divided into sets of size *n* is *n*-way set associative, and when *n* is 1, the cache is *direct-mapped*. A cache line is associated with a specific set, but it may be located anywhere in the set. Most caches use a least recently used (LRU) policy to determine which cache line to evict when the set is full.

Hill and Smith categorize a cache miss as compulsory, conflict, or capacity [47]. A *compulsory* miss is the first access to a cache line. A *capacity* miss occurs when the cache size is too small to hold all the cache lines referenced by a program. With sufficient capacity, a *conflict* miss occurs when multiple cache lines are mapped to the same set in the cache, and the program subsequently references an evicted line.

## 2.2 Improving Memory Performance

There are many techniques for improving memory performance. These techniques can be categorized as techniques for tolerating cache latency or improving cache utilization.

#### 2.2.1 Tolerating Latency

One method to improve memory performance is to tolerate cache miss latencies. The goal of latency tolerating techniques is to perform useful work between the time when a program requests data and the time when the program uses the data. In a very simple inorder processor, the request and use occur at the same time, and the processor stalls until the memory subsystem transfers the data from memory to a register. Modern processors are able to separate the tasks of requesting and using data. The difficulty is finding enough work to perform between the request and use.

We discuss three techniques for tolerating cache latency. These include *prefetching*, the focus of this dissertation, *multithreading*, and *out-of-order* execution.

#### 2.2.1.1 Prefetching

Most high performance architectures contain several simple hardware mechanisms for hiding memory hierarchy access costs. Early cache designs allowed only a single outstanding memory access to occur. Thus, all memory accesses stalled the processor until completed. Kroft introduced lockup-free caches [62] to enable multiple concurrent memory accesses. Lockup-free caches permit *non-blocking* loads that do not stall the processor until a future instruction references the data. Lockup-free caches require a mechanism, such as miss status handling registers (MSHRs), to maintain information about pending loads. A processor limits the number of allowable pending loads, and stalls when the maximum number of loads are outstanding.

Prefetching is a hardware or software technique for tolerating cache latency by providing a mechanism to separate the request and use of data explicitly. A software approach explicitly inserts prefetch instructions into the instruction stream to perform data prefetching. In a hardware approach, the processor contains a mechanism to automatically prefetch data without the use of extra instructions.

A prefetch initiates a transfer of data in the memory hierarchy prior to the demand request. A prefetch instruction is similar to a non-blocking load. The main difference is that a prefetch instruction typically does not cause an exception if the address is invalid. Another difference is that a prefetch instruction does not load the data into a register. Instead, the prefetch moves data closer to the processor in the memory hierarchy.

A simple form of hardware prefetching is long cache lines. If an object is smaller than a cache line, then adjacent objects are also brought into the cache when a miss occurs. Long cache lines often improve the performance of programs that have spatial locality. Long cache lines are not always effective because not all programs exhibit spatial locality. The main disadvantage of long cache lines is the increase demand for available bandwidth to memory. In a multiprocessor, long cache lines increase false sharing, which occurs when two processors require separate objects that reside on the same cache line. We discuss more complex prefetch methods in Section 2.6.

An effective prefetch method must determine what to prefetch and when to issue the prefetch. We evaluate prefetching effectiveness by categorizing dynamic prefetches as follows:

- The data in a *useful* prefetch arrives on time and is accessed by the program.

- The latency of a *late* prefetch is only partially hidden because a request for the cache line occurs while the memory system is still retrieving the cache line.

- The cache replaces an *early* prefetch before the cache line is used. If the cache line is never accessed, the prefetch is early.

- An *unnecessary* prefetch hits in the L1 cache, or is coalesced into an MSHR.

#### 2.2.1.2 Multithreading

Multithreading is a technique for tolerating latency by switching contexts to a pending thread when the processor stalls [98, 2, 107]. To improve memory performance, a processor switches to a thread that can execute instructions when a memory stall occurs in the current thread. One advantage of multithreading over prefetching is that it is not necessary to determine what to prefetch and when to issue the request. A multithreaded architecture simply switches to another context whenever a cache miss occurs. The main disadvantage is that the program must contain enough parallelism so that when a cache miss occurs, another context is able to execute. Another disadvantage is that hardware implementations require complex architectural changes to support multiple contexts, which places additional pressure on hardware resources.

Recently, several researchers have investigated methods to use additional threads in a multithreaded system to prefetch data [36, 91, 28, 69, 99]. These methods implement new hardware, and some also use software support, to create separate threads that speculatively run ahead of the main thread and prefetch data. The existing methods use different techniques for deciding when to create and how to manage the speculative threads.

#### 2.2.1.3 Out-of-order Execution

Out-of-order (OOO) execution is a hardware technique for tolerating a small amount of memory latency. A processor with out-of-order execution is able to execute instructions when the operands become available rather than in the order that the program specifies. Out-of-order processors exploit instruction level parallelism by allowing other instructions to execute when an instruction stalls in the processor waiting for a resource. Out-of-order processors use a fixed-size instruction window from which instructions may be executed. In order to preserve program semantics, the processor retires the instructions in-order. The amount of latency that an out-of-order processor is able to tolerate depends upon the amount of instruction level parallelism (ILP) and the size of the instruction window. Most high performance commercial processors support out-of-order execution including the Alpha 21264 [57], MIPS R10000 [121], and Intel Pentium [48].

#### 2.2.2 **Program Transformations**

Developing code and data transformations to improve cache utilization is a very active area of research. Code transformations attempt to reorder the program instructions to utilize the data in the caches more effectively. Data transformations reorganize data layouts to increase reuse. These techniques attempt to improve the cache effectiveness by reusing data that is in the cache already. In contrast, data prefetching attempts to tolerate cache latency by moving data into the cache speculatively. The techniques we describe below often complement data prefetching.

A typical code transformation restructures the computation in a loop to improve the spatial or temporal locality of the program, moving reuse of the same or adjacent locations closer together in time [1, 64, 73]. Loop tiling is a classic locality optimization that works by transforming a loop nest so that array accesses reuse smaller blocks of data that fit into the cache. Compilers typically employ advanced static analysis techniques to determine when and how to perform a transformation. The static techniques perform data dependence analysis to determine the access patterns in programs [63]. The static analysis needs to determine the transformation is legal. If the compiler is unable to determine the legality then it cannot perform the optimization. An advantage of data prefetching is that compilers can be more aggressive in determining opportunities because legality is not a requirement.

Data transformations attempt to co-locate data to improve spatial locality. Data transformations are often performed at run time or require profiling information to reorganize data. Calder, Krintz, John, and Austin present and evaluate an approach for cache conscious data placement [15]. They reduce cache conflicts by using profiling information to relocate objects. Chilimbi and Larus rearrange data at garbage collection time to improve data locality in object-oriented programs [27]. Chilimbi, Hill, and Larus perform object reordering at allocation time to improve cache locality in C programs [25]. Chilimbi, Davidson, and Larus evaluate structure splitting and field reorganization to improve cache performance [24]. Truong, Bodin, and Seznec use program profiling to evaluate two data layout techniques, field reorganization and instance interleaving, to improve the cache behavior of dynamically allocated data in C programs [105]. Since they apply these transformations by hand, Truong also describes plans for automating the data layout techniques based upon profile information [104]. Kistler and Franz evaluate a profile-based optimization that reorders members in objects to improve spatial locality [59]. Franz and Kistler also propose physically splitting frequently and infrequently accessed members of objects to improve cache performance [38].

Other data transformations apply specifically to heap allocated data in a garbage collected environment. Moon describes a mostly depth-first copying garbage collection algorithm to improve the page locality of Lisp programs [75]. Stamos evaluates five static grouping garbage collection algorithms to improve the locality of objects [100]. Courts proposes a dynamic garbage collection algorithm for improving locality [30]. Wilson, Lam, and Moher propose and evaluate different static copying algorithms to improve locality in garbage collected systems [111]. They introduce hierarchical decomposition that combines breadth-first and depth-first traversals in a copying algorithm. The algorithm is similar to Moon's, but does not rescan any locations. Wilson, Lam, and Moher also empirically examine the cache performance of generational garbage collection [112]. Their results show that miss rates in garbage collected systems are not very high. Reinhold empirically examines the cache performance of garbage collected programs, and looks at both the mutator and the collector [88]. Boehm experiments with adding prefetching to a non-moving, marksweep garbage collector [12]. Boehm prefetches objects during the mark phase. Boehm shows that prefetching improves performance on a set of microbenchmarks running on a Pentium II and HP PA-RISC machine.

In this section, we describe many methods for improving memory performance. In this dissertation, we focus on software data prefetching to tolerate memory latency. Our approach is applicable to a wide range of programming styles, and does not require complex hardware mechanisms. We also do not require advanced code or data transformations. Compilers must be conservative when applying code or data transformations to ensure program correctness. Although software prefetching does require compiler support, the prefetch instructions do not affect the correctness of programs. We use data-flow analysis to discover prefetch opportunities. In the following section, we describe the foundations of data-flow analysis.

#### **2.3 Data-Flow Analysis**

A data-flow framework provides a generic mechanism for specifying a program analysis [58, 55]. Data-flow analysis is a pervasive program analysis technique in many compilers. In this section, we discuss the fundamentals behind data-flow analysis. We separately define data-flow analysis for use within a procedure and for a whole program. Nielson et al. present an excellent discussion of intraprocedural and interprocedural analysis [80].

#### 2.3.1 Intraprocedural Data-Flow Analysis

In this section, we describe the basics behind intraprocedural data-flow analysis. An *intraprocedural* data-flow analysis operates on a single procedure and makes conservative assumptions about procedure calls and returns.

A monotone data-flow analysis framework consists of the following:

A complete lattice, (L, ⊑, ⊔, ⊓, ⊥, ⊤). L is a set that defines the elements in the lattice. The ⊑ function defines a partial ordering of the elements in L. Thus ⊑ is reflexive, transitive, and anti-symmetric. For any X ⊆ L, ⊔X denotes the least upper bound of X. Formally, ∀l ∈ L, ⊔X ⊑ l if and only if X ⊑ l. The greatest lower bound, ⊓X, is defined by replacing ⊑ with ⊒. The ⊔ and ⊓ functions are known as the *join* and *meet* operations, respectively. The join and meet functions are idempotent, commutative, and associative. The elements  $\perp$  and  $\top$  are known as *bottom* and *top*, respectively. Thus  $\perp = \sqcup \emptyset = \sqcap L$ , and  $\top = \sqcap \emptyset = \sqcup L$ .

A set *F* of monotone transfer functions over *L*. A function *f* : *L* → *L'* is monotonic if x ⊆ y implies *f*(x) ⊆ *f*(y). *F* is closed under composition, and contains the identity function. There is a function *f* for each statement in a procedure. Intuitively, *f* computes the data-flow information that captures the semantics from executing part of a program.

Solving an analysis problem using a data-flow framework requires a flow graph and a function that maps each node in the flow graph to a function in F. A flow graph is a representation of the control flow of a procedure. Formally,  $G = (N, E, n_0)$  is a flow graph where N is the set of nodes that represent the statements in a procedure, E is the set of edges that represent possible control flow, and  $n_0$  is the start node of the procedure. The set of edges is a subset of  $N \times N$ . An edge  $(n_i, n_j)$  indicates that control flow may leave node  $n_i$  and enter  $n_j$ .

We denote the function in *F* associated with node  $n \in N$  by  $f_n$ . The data-flow instance yields the following equations for an analysis:

Analysis<sub>*in*</sub>(*n<sub>j</sub>*) =

$$\bigsqcup_{(n_i,n_j)\in E}$$

Analysis<sub>*out*</sub>(*n<sub>i</sub>*) (2.1)

Analysis<sub>out</sub>

$$(n_j) = f_{n_j}(\text{Analysis}_{in}(n_j))$$

(2.2)

Equations 2.1 and 2.2 define a *forward* analysis. Equation 2.1 represents the data-flow information upon entering a statement in the procedure, and Equation 2.2 represents the data-flow information when exiting a statement. A *backward* analysis begins with the exit node and processes the statements in reverse order. To define a backward analysis, we

change Equation 2.1 so that  $(n_j, n_i) \in E$ . We also need to swap the meaning of *out* and *in* so that Equation 2.2 represents the data-flow information upon entering a statement, and Equation 2.2 represents the data-flow information when exiting.

An analysis may be *flow-sensitive* or *flow-insensitive*. In a flow-sensitive analysis, the order of statements in the procedure matter. A flow-insensitive analysis ignores control flow within a procedure. In general, a flow-sensitive analysis is more accurate, but usually takes longer to perform.

### 2.3.2 Interprocedural Data-Flow Analysis

An *interprocedural* data-flow analysis takes procedure calls and returns into account during the analysis. The interprocedural analysis extends the definition of an intraprocedural flow graph *G* to include procedure calls and returns. The interprocedural flow graph contains a node for each procedure in a program. An edge connects two nodes if there is a calling relationship between the procedures. Formally,  $IPG = (N', S, E', m_0)$  where N' is the set of procedures in a program, *S* is the set of call site labels, E' is a set of labeled edges representing procedure calls, and  $m_0$  is the main procedure. The set of edges is a subset of  $N' \times S \times N'$ . The call site label is necessary to distinguish between multiple calls from one procedure to the same target procedure.

An interprocedural analysis operates on the *IPG* and uses Equations 2.1 and 2.2. In addition, the interprocedural analysis contains two transfer functions for each call. One transfer function is for the call,  $f_c$ , and the other is for the return,  $f_r$ . The callee also contains two transfer functions: one for the start of the procedure,  $f_s$ , and one for the end of the procedure,  $f_e$ .

At a procedure call, the transfer function  $f_c$  creates a new context and the initial dataflow information for analyzing the callee. Upon return, the transfer function  $f_r$  restores the caller's data-flow information and adds new information from the callee for the return. An interprocedural analysis may be *context-sensitive* or *context-insensitive*. In a context-insensitive analysis, the data-flow information for a procedure is a combination of the information from all call sites. The framework analyzes each procedure only once using the combined information. In a context-sensitive analysis, the framework analyzes target procedures in each distinct calling context.

At a call site with multiple potential callees, *e.g.*, due to a virtual method call, the interprocedural framework applies the join operator to the results of the analysis for each possible callee.

## 2.4 Induction Variable Analysis

In this section, we describe induction variable analysis, and we survey the related work. We develop a general recurrence detection analysis in this dissertation that subsumes induction variable analysis.

An induction variable is incremented or decremented by the same value during each loop iteration. An example of an induction variable is the expression i = i + c occurring in a loop. During each iteration of the loop, the variable i is incremented by a loop invariant value, c. Traditional algorithms for finding induction variables are either loop-based [4] or use static single assignment (SSA) form [31].

The original use for induction variable detection was operator strength reduction [67, 4]. The initial algorithms typically require the compiler to compute reaching definitions and loop invariant expressions. The algorithms are conservative and find simple linear induction variables. The PTRAN compiler uses an optimistic approach, and assumes variables in loops are induction variables until proven otherwise [6]. Gerlek, Stoltz, and Wolfe present a demand driven SSA approach for detecting general induction variables by identifying strongly connected components in the SSA graph [40]. Gerlek et al. present a lattice for classifying different types of induction variables. They detect a wide range of induction variables including linear, polynomial, exponential, periodic, and wrap-around. Haghighat

and Polychronopoulos also categorize different types of induction variables for use in parallelizing compilers [44]. Ammarguellat and Harrison describe an abstract interpretation technique for detecting general recurrence relations, which includes induction variables [8]. The approach requires a set of patterns, which they call templates, that describe the recurrences.

Wu, Cohen, and Padua describe a data-flow analysis for discovering loop induction variables [114, 115]. The analysis computes whether a variable increases or decreases along a given execution path, and the minimum and maximum change in value. The authors compute closed form expressions from the distance intervals to perform array dependence testing. Wu et al.'s induction analysis does not compute information about linked structures. We present a different data-flow analysis for identifying induction variables, and we use the analysis to discover both induction variables and linked structure traversals. We also use the analysis for prefetching rather than array dependence testing.

# 2.5 Vortex: A Compiler Infrastructure

This dissertation describes several new compiler analyses and optimizations, and presents empirical results. We implement and evaluate these new techniques in Vortex, an existing compiler infrastructure. Vortex is an optimizing compiler for object-oriented languages developed at the University of Washington [34]. We briefly describe Vortex in this section. In Section 4.5, we describe Vortex in more detail, and we discuss our extensions to support prefetching.

Vortex supports several object-oriented languages including Cecil, Java, C++, Modula-3, and Smalltalk. The compiler itself is written in Cecil. The implementation work in this dissertation uses the Java front-end. At a high level, Vortex performs the following steps:

1. Convert object-oriented program to an intermediate representation.

22

- 2. Perform interprocedural optimization on the complete program. This step is optional and performed only when the user specifies an interprocedural optimization.

- 3. Perform intraprocedural optimization. The backbone of the Vortex compiler is a flexible data-flow analysis framework.

- 4. Generate SPARC assembly code.

Vortex does not operate directly on Java source files. Instead, Vortex converts Java class files (byte codes) to a high-level internal representation. The intermediate language represents high-level object-oriented features. Vortex performs all analysis and optimization on the intermediate representation of the program. Vortex represents the control flow and individual statements as a graph. The nodes in the graph represent operations, and the arcs between the nodes indicate either data or control flow. During the compilation process, Vortex performs several conversions on the intermediate language to convert high-level operations to low-level operations. After each conversion, Vortex applies different analyses and optimizations. The output of the compiler is either C or assembly language.

The high-level form closely matches the original program structure. For example, Vortex contains high-level operators for object creation and method calls. The low-level form more closely matches the machine level. The low level no longer represents the objectoriented features. Instead, the graph nodes in the low-level representation are almost a one-to-one match with the assembly instructions.

A central part of the Vortex optimization infrastructure is a general iterative data-flow analysis framework [18, 65]. The framework is parameterized by the properties that we describe in Section 2.3. An important feature of the analysis framework is the ability to compose, or combine, several analyses so that they run together. Each analysis is able to query the results of another analysis when running. Running multiple analyses at the same time potentially improves precision by eliminating phase ordering problems. This feature also improves code reuse by making it easy to incorporate the results of other analyses into a new analysis, and reduces compilation time.

# 2.6 Prefetching: Related Work

In this section, we survey existing data prefetching research with a focus on compiler support. We also refer the reader to a thorough survey of data prefetching techniques for scientific programs by VanderWiel and Lilja [110]. The article presents an overview of existing techniques for software data prefetching, hardware data prefetching, combinations of software and hardware prefetching, and prefetching for multiprocessors.

Sections 2.6.1 and 2.6.2 present related work for array-based software and hardware prefetching, respectively. For completeness, we briefly describe prefetching in multiprocessors in Section 2.6.3, although we do not investigate prefetching for multiprocessors.

In Section 2.6.4, we describe Luk and Mowry's prefetching algorithms for linked data structures. Since this work most closely relates to ours, we describe it separately. We discuss other software and hardware approaches for prefetching linked structures in Section 2.6.5.

### 2.6.1 Array Prefetching in Software

In this section, we describe previous research that uses software approaches for prefetching arrays. Much of the research in data prefetching has focused on data prefetching for array-based scientific programs. The array prefetching techniques generate prefetch instructions for array references that will likely occur in future loop iterations.

Callahan, Kennedy, and Porterfield present one of the first descriptions and evaluations of software prefetching [16]. They use a very simple algorithm to add non-blocking prefetch instructions to twelve array-based Fortran programs. The algorithm prefetches array references one loop iteration before they are needed. The results show that prefetching improves miss rates, but the overhead of the prefetch instructions may be too large to improve execution times. The authors suggest a few changes to reduce the overheads to make prefetching profitable.

Klaiber and Levy describe an algorithm for software controlled data prefetching that holds the prefetched data in a separate fully-associative buffer instead of the cache [60]. The algorithm works by inserting a prefetch for an array element one or more iterations before the actual load of the datum. Results show that prefetching improves performance on the Livermore Loops benchmarks using average time per memory reference as the metric. The algorithm is most effective on array-based scientific codes, but it also slightly improves performance on two non-numeric programs. Klaiber and Levy also indicate that their algorithm causes little or no increase in bandwidth utilization.

Chen, Mahlke, Chang, and Hwu compare the performance of software prefetching into the cache verses a special prefetch buffer [22]. They do not specifically target either regular or irregular access patterns. Instead their algorithm adds prefetches for as many data loads as possible when they are able to completely hide the memory latency. Their simulation results on a superscalar processor suggests that a prefetch buffer is more effective than a larger cache. One drawback of the research is that Chen et al. use very small (1K or 2K) caches in their evaluation.

Yamada, Gyllenhaal, Haab, and Hwu combine data relocation and block prefetching to improve data cache performance [118]. The hardware support consists of five special instructions to perform data relocation and prefetching. They use a compiler to transform loop nests in scientific programs and add the special instructions. The non-blocking instructions compress and preload arrays into sequential cache locations. The compiler also uses standard cache improvement techniques such as loop unrolling and tiling. Simulation results show improvements in cache utilization and execution speed.

Mowry, Lam, and Gupta describe and evaluate compiler techniques for adding prefetching to array-based codes [79, 78]. This paper is one of the first that reports execution times for compiler inserted prefetching. The algorithm works on affine array accesses within scientific codes. The algorithm significantly improves performance by as much as a factor of 2. They also show that their algorithm is better than indiscriminate prefetching. The algorithm involves two steps. First the algorithm performs locality analysis to determine array accesses that are likely to miss in the cache. Then, the algorithm uses loop splitting to isolate predicated cache misses, and uses software pipelining to schedule prefetch instructions.

In his dissertation, Selvidge presents profile-guided software data prefetching as a scheduling algorithm [94]. A compiler, called c-flat (Compiler For LAtency Tolerance), uses profile information to identify regular and irregular data reference streams. In Section 2.6.5, we discuss Selvidge's work in the context of prefetching linked data structures. C-flat also works on array-based codes, including indirection arrays. Most of the benefits that Selvidge reports are due to prefetching array elements.

McIntosh extends Mowry's work by focusing on the compiler support necessary for software prefetching [72]. He develops several new compiler techniques to eliminate useless prefetches and to improve prefetch scheduling for array-based codes. McIntosh develops a new technique for detecting cross-loop reuse that provides useful information for improving software prefetching. Cross-loop reuse summarizes data accesses that occur between loop nests as opposed to within a single loop nest, *i.e.*, intra-loop reuse.

Two reports evaluate software prefetching on commercial processors using the HP PA-8000 and the PowerPC. Santhanam, Gornish, and Hsu evaluate software prefetching on the HP PA-8000, a 4-way superscalar processor [93]. The prefetch algorithm concentrates on array references occurring within the innermost loops. Santhanam et al. discuss implementation details and present results showing a 26% speedup on the SPECfp95 benchmark suite. Bernstein, Cohen, Freund, and Maydan describe a compiler implementation for data prefetching on the PowerPC architecture [11]. Bernstein et al. follow Mowry's approach but the only transformation they apply is loop unrolling. Bernstein et al. provide actual

execution times for the SPECfp92 benchmarks and Nasa7 kernels. Improvements occur on only three of the fourteen SPECfp92 programs and six of the seven Nasa7 kernels.

We propose an array prefetch algorithm that is easy to implement and is effective on array-based Java programs. Our algorithm does not require array locality analysis or loop transformations, which prior techniques use. None of the prior methods focus on Java, which implements multidimensional arrays as arrays-of-arrays.

### 2.6.2 Array Prefetching in Hardware

Hardware prefetching schemes add prefetching functionality without explicit programmer or compiler assistance. The main benefit of hardware schemes is the ability to run existing program binaries, which enables prefetching without recompiling the program. Most hardware mechanisms prefetch only array reference streams. Several of the techniques we describe below require some software support to attain performance improvements.

Smith investigates a simple cache prefetching algorithm called one block lookahead[96, 97]. When a program references cache line *i*, the one block lookahead scheme fetches the next cache line, i + 1. Smith shows that one block lookahead is successful in lowering miss rates.

Jouppi proposes and evaluates stream buffers as a mechanism to prefetch data into a separate area from the cache [54]. When a reference misses in the cache, the processor first checks the stream buffer. The stream buffer is a simple FIFO queue; when the processor removes an item from the head of the queue, the stream buffer fetches a new successive address. Palacharla and Kessler extend stream buffers and present a more detailed evaluation [85]. The extensions include a filter to reduce the bandwidth requirements and the ability to prefetch non-unit strides. They conclude that stream buffers work well on regular, scientific codes but not as well on irregular codes.

Baer and Chen propose a purely hardware prefetching scheme for scientific programs[10, 19]. The scheme predicts the execution stream and preloads references with arbitrary con-

stant strides. The hardware mechanism includes a reference prediction table (RPT) and a look-ahead program counter (LA-PC). The RPT maintains state about load and store instructions such as the previous address encountered and the stride value. If an entry appears in the RPT when the LA-PC encounters a load or store, then the hardware predicts the next address to be loaded based upon the previous address and stride value. The mechanism works only for loads and stores with regular accesses. Experiments show reductions in the number of cycles per instruction (CPI) for scientific programs.