### OVER-PROVISIONED MULTICORE SYSTEMS

by

Koushik Chakraborty

# A dissertation submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

2008

## Abstract

Technology scaling has provided system designers with an exploding transistor budget, far more than what was available when the core principles behind many existing commodity microprocessors were envisioned. With this tremendous growth, however, comes a whole new set of engineering challenges involving power density, thermal efficiency, and so on. In particular, the power constraint is rapidly becoming one of the first order design considerations in microprocessor designs. In the landscape of general purpose processors, such power limited designs designate a significant paradigm shift from the area limited designs of the past several decades.

This dissertation proposes a model to capture the first order impact of the power constraint in the architectural design. Denoted as the Simultaneously Active Fraction (SAF), this metric represents the fraction of the entire chip resources that can be active simultaneously, given a target power envelope. As the improvement in the energy efficiency of individual transistor devices lags behind the growth in their integration capacity, the dissertation finds that the SAF is monotonically decreasing in each successive technology generation.

In the context of such a fundamental technology trend where integrating processing cores on a single chip comes at a marginal cost compared to the cost of powering them up simultaneously, this dissertation investigates a novel multicore design paradigm: Over-provisioned Multicore System (OPMS). An OPMS is a class of multicores that *by design* provision more processing core resources than that can be kept active for their target Thermal Design Power (TDP). Since only a subset of the on-chip cores can be active at any given time, this design paradigm affords tremendous flexibility in assigning computation on processing cores, facilitating many novel techniques in this broad framework.

To demonstrate a concrete application of this framework, the dissertation proposes Computation Spreading (CSP): a new model for distributing the collective work from multithreaded applications. CSP aims to collocate similar computation fragments from different threads on the same core, while distributing dissimilar computation fragments from the same thread across multiple cores. Under CSP, on-chip cores in an OPMS are dynamically specialized via retaining mutually exclusive predictive states, and function like *hardware accelerators* for appropriately assigned computation on them, without requiring any structural modifications in the core micro-architecture. The dissertation demonstrates the effectiveness of CSP in an OPMS through rigorous evaluation of performance, energy efficiency, and several design trade-offs that are critical to understand the impact of the OPMS design paradigm in future microprocessor designs.

## Acknowledgments

First and foremost, I thank my wife Sanghamitra for her immense love and support. I would not have come this far, without her unwavering zeal to inspire and motivate me. Being a graduate student herself, she has put her needs aside in numerous occasions, and guided me through the most difficult times in my graduate student career. Words cannot express my gratitude for her, and I dedicate this work to her.

I owe a great deal of what I am today to my late mother, and my father. They have instilled a sense of responsibility and dedication in my life, and this work would not have been possible without them. Even though far apart, my brother has supported me tremendously through out my life, and took care of my parents so that I can have peace of mind while pursuing my PhD. I am greatly indebted to all of them

My advisor Guri Sohi has been instrumental in the development of my research career. Guri gave me the freedom to choose problems on my own, while at the same time guiding me to make this choice. He has changed my engineering mindset of looking for specific solutions that are relevant today, to focus on a larger context, and realize the importance of intriguing research directions that can have broader impact in the future. His unique mentoring style has made a lasting impact on me, including my vision in pursuing research, and writing.

I thank several members of Guri's research group, both current and past: Sai, Jichuan, Matthew Allen, Philip Wells, Allison, and Vikas. I learned a great deal from their feedbacks on my research, writing and presentations. Sai was instrumental in the early phase of our infrastructure develop-

ment that many of us used as a starting point for our own developments. Special thanks to Philip, who not only withstood my presence in our shared office for long, but also collaborated with me in several research projects and stimulating discussions. I also thank other members of the Wisconsin Architecture group in general for providing a tremendous atmosphere for pursuing my PhD.

I thank members of my committee: Mark Hill, David Wood, Mike Swift, Mikko Lipasti and Remzi Arpaci-Dusseau. Through out my stay in Madison, I have learned a great deal from all of them. I have also enjoyed several discussions with Karu Sankaralingam, and his feedback on my presentations was invaluable.

I have had the good fortune of having many good friends in and outside of Madison. All of them have contributed in some way or other in my life, and I thank them all!

# **Table of Contents**

| Abstract                                                         | i   |

|------------------------------------------------------------------|-----|

| Acknowledgments                                                  | iii |

| List of Tables                                                   | ix  |

| List of Figures                                                  | X   |

| 1 Introduction                                                   | 1   |

| 1.1 Motivation                                                   | 3   |

| 1.1.1 Challenges and Opportunities in Multicore Systems          | 3   |

| 1.1.2 Energy Efficiency                                          | 4   |

| 1.2 Thesis Contributions                                         | 6   |

| 1.2.1 Simultaneously Active Fraction                             | 6   |

| 1.2.2 Over-provisioned Multicore System                          | 7   |

| 1.2.3 Computation Spreading                                      | 7   |

| 1.3 Dissertation Outline                                         | 8   |

| 2 Simultaneously Active Fraction                                 | 9   |

| 2.1 Area and Power Constraint                                    | 10  |

| 2.1.1 Area Constraint                                            | 11  |

| 2.1.2 Power Constraint                                           | 12  |

| 2.1.3 Satisfying Area and Power Constraints                      | 12  |

| 2.2 SAF: First Order Model                                       | 14  |

| 2.2.1 Analytic Model                                             | 14  |

| 2.2.1.1 Trends in Dynamic Power                                  | 14  |

| 2.2.1.2 Static Power Trends                                      | 16  |

| 2.2.1.3 SAF                                                      | 17  |

| 2.2.2 SAF Trends: A Quantitative Analysis                        | 18  |

| 2.2.3 Limitations                                                | 21  |

| 2.3 Targeting SAF for Power Reduction                            | 21  |

| 2.3.1 Targeting Per-Device Power is Insufficient                 | 21  |

| 2.3.2 Existing SAF Reduction Techniques                          | 24  |

|                                                                  | 25  |

| 2.4.1 Background                                                 | 26  |

| 2.4.1.1 Cost Model                                               | 26  |

| 2.4.1.2 Performance Model                                        | 26  |

| 2.4.2 Hill-Marty Model Extension: Incorporating Power Constraint | 27  |

|        | An Application of CSP: Separating User and OS |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

|--------|-----------------------------------------------|-----|-----|-----|-----|-----|-----|---|---|-----|---|-----|---|---|---|-----|

| 4.4.1  | Why Target User and OS?                       |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

|        | CSP Implementation                            |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

| 4.5.1  | CSP Policies                                  |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 79  |

| 4.5.2  | 1                                             |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 81  |

| 4.5.2. | 6                                             |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 82  |

|        | Related Work                                  |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 84  |

| 4.7    | Summary                                       | ••• | • • | •   | •   | • • | • • | • | • | ••• | • | ••• | • | • | • | 86  |

| 5 M    | lethodology                                   |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 88  |

| 5.1    | Workloads                                     | ••• |     | •   | •   | ••• | • • | • | • | ••• | • | ••• | • | • | • | 89  |

| 5.1.1  | Comparing Different System Configurations .   | ••• |     | •   | •   | ••• | • • | • | • | ••• | • | ••• | • | • | • | 90  |

|        | Simulation Infrastructure                     |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 91  |

|        | Multicore Systems                             | ••• |     | •   | •   | ••• | • • | • | • |     | • | ••• | • | • | • | 93  |

| 5.3.1  | In-order Core                                 |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 94  |

|        | Energy Estimation                             |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 95  |

| 5.4.1  | Calibrating Wattch                            |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 95  |

|        | OPMS Methodology                              |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 98  |

| 5.5.1  | Core-Provisioning                             |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 98  |

| 5.5.2  | Leakage in an OPMS                            | ••• |     | •   | •   | ••• | • • | • | • | ••• | • | ••• | • | • | • | 98  |

| 6 E    | valuation                                     |     |     |     |     |     |     |   |   |     |   |     |   |   |   | 100 |

| 6.1    | Workload Characterization                     |     |     | ••• | •   |     |     | • | • |     |   |     |   |   |   | 102 |

| 6.1.1  | IPC                                           |     |     | •   | •   |     |     | • | • |     |   |     |   |   |   | 102 |

| 6.1.2  | Memory Latency                                |     |     | •   | •   |     |     | • | • |     |   |     |   |   |   | 104 |

| 6.1.3  | Cache Miss Rates                              | ••• |     | •   | • • | ••• |     | • | • |     |   |     |   | • | • | 106 |

| 6.2    | Locality Impact                               | ••• |     | •   | • • | ••• |     | • | • |     |   |     |   | • | • | 109 |

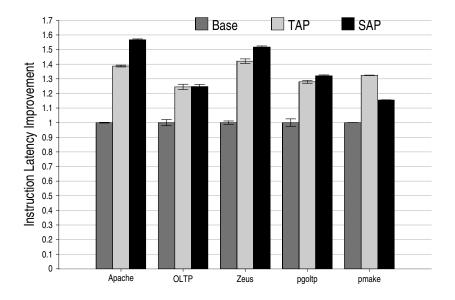

| 6.2.1  | Instruction Locality                          | ••• |     | •   | •   | ••• |     | • | • |     |   | ••• |   | • |   | 109 |

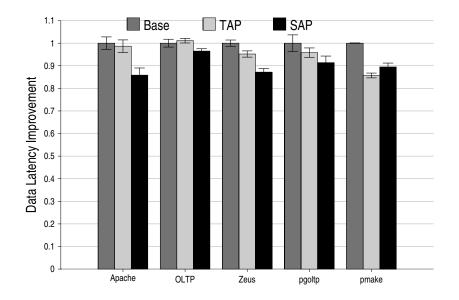

| 6.2.2  | Data Locality                                 | ••• |     | •   | •   | ••• |     | • | • |     |   | ••• |   | • |   | 114 |

| 6.2.2. | .1 Load                                       | ••• |     | •   | •   | ••• |     | • | • | ••• | • | ••• | • | • | • | 114 |

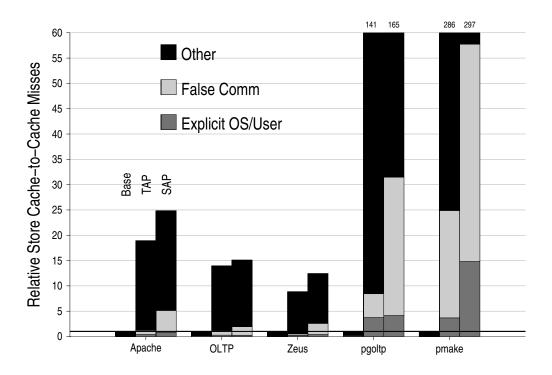

| 6.2.2. | 2 Store                                       | ••• |     | •   | •   | ••• |     | • | • | ••• | • | ••• | • | • | • | 118 |

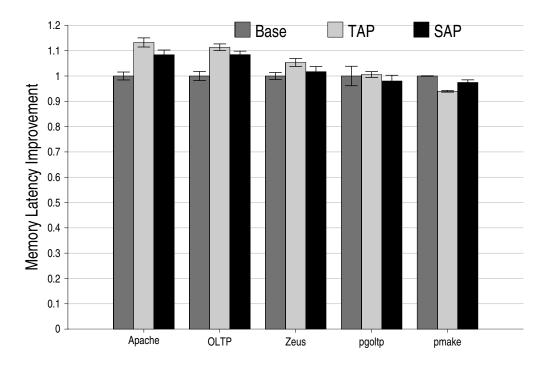

| 6.2.3  | Impact on Average Memory Latency              | ••• |     | •   | •   | ••• | • • | • | • | ••• | • | ••• | • | • | • | 121 |

| 6.2.4  | Branch Predictors                             |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

|        | Computation Transfer Overhead                 |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

| 6.3.1  | Latency                                       |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

| 6.3.2  | On-chip Interconnect Bandwidth                |     |     |     |     |     |     |   |   |     |   |     |   |   |   |     |

| 6.4    | Performance Impact                            |     |     | ••  | •   |     |     |   |   |     |   |     |   |   |   | 131 |

| 6.4.1 Overall Speedup                          |

|------------------------------------------------|

| 6.4.2 Contention Overhead                      |

| 6.4.3 Code Reuse With TAP/SAP                  |

| 6.5 Energy Efficiency                          |

| 6.5.1 Core Utilization                         |

| 6.5.2 Core Energy                              |

| 6.5.3 Inactive Periods                         |

| 6.5.4 Thermal Characteristics                  |

| 6.5.5 Comparison of di/dt                      |

| 6.5.6 Cache Energy                             |

| 6.5.7 Energy Delay                             |

| 6.6 Sensitivity Analysis                       |

| 6.6.1 Evaluating CSP in Conventional Multicore |

| 6.6.2 The Role of the OPMS Micro-Architecture  |

| 6.6.2.1 Runtime                                |

| 6.6.2.2 Power                                  |

| 6.6.2.3 Energy                                 |

| 6.6.2.4 Energy-Delay Product                   |

| 6.6.3 In-order cores                           |

| 6.6.4 L1 Cache Sizes                           |

| 6.7 Related Work                               |

| 6.8 Summary                                    |

|                                                |

| 7 Conclusions 170                              |

| 7.1 Contributions                              |

| 7.1.1 Simultaneously Active Fraction (SAF)     |

| 7.1.2 Over-provisioned Multicore System (OPMS) |

| 7.1.3 Computation Spreading                    |

| 7.2 Future Directions                          |

| 7.2.1 OPMS Management                          |

| 7.2.2 CSP                                      |

| References 177                                 |

# **List of Tables**

| 2.1 | Technology scaling trends of Dynamic Power           | 16  |

|-----|------------------------------------------------------|-----|

| 4.1 | Instruction Footprint                                | 73  |

| 4.2 | OS and User instruction profile                      | 77  |

| 5.1 | Workloads                                            | 90  |

| 5.2 | Baseline processor parameters                        | 93  |

| 5.3 | Micro-architectural Parameters of In-order Cores     | 94  |

| 5.4 | Core power consumptions in the baseline multicore    | 97  |

| 5.5 | Core provisioning in TAP and SAP                     | 99  |

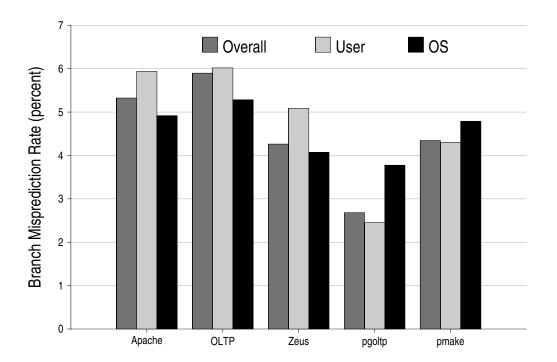

| 6.1 | Percentage Improvements in YAGS Mis-prediction Rates | 126 |

| 6.2 | Increase in Current Variations (lower is better).    | 146 |

# List of Figures

| 2.1  | SAF trends                                                                         | 19 |  |  |  |  |

|------|------------------------------------------------------------------------------------|----|--|--|--|--|

| 2.2  | Speedup from the Symmetric and the Dynamic Multicore                               |    |  |  |  |  |

| 2.3  | Speedup from the Asymmetric Multicore and comparison with the Dynamic Multicore 32 |    |  |  |  |  |

| 2.4  | Impact of over-provisioning in asymmetric multicore speedup                        | 36 |  |  |  |  |

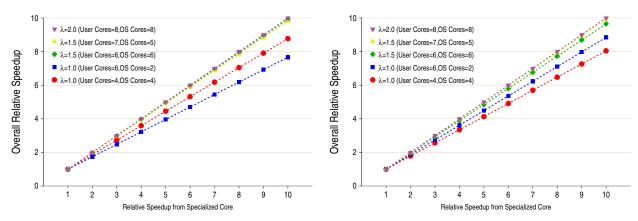

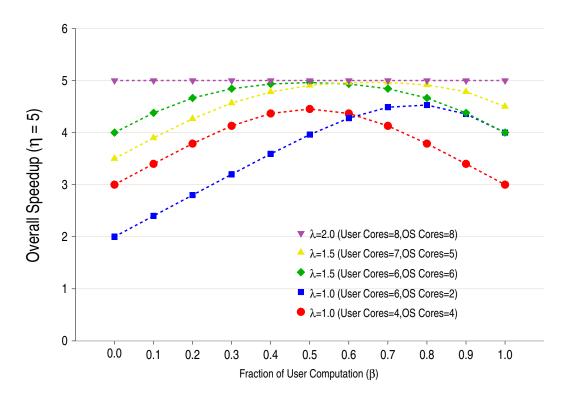

| 2.5  | Impact of Over-provisioning on Speedups from Multithreaded Applications            | 42 |  |  |  |  |

| 2.6  | Speedups in a range of server applications                                         | 43 |  |  |  |  |

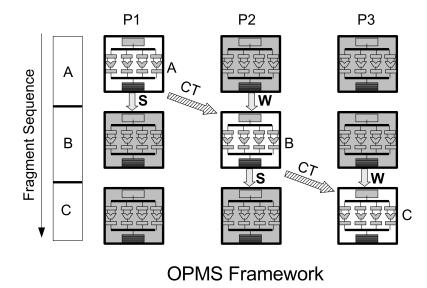

| 3.1  | OPMS Framework                                                                     | 49 |  |  |  |  |

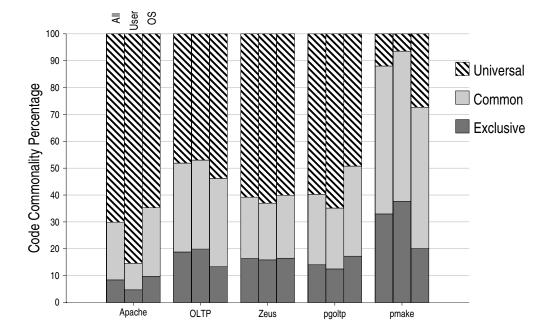

| 4.1  | Multicore Code Reuse Characteristics                                               | 71 |  |  |  |  |

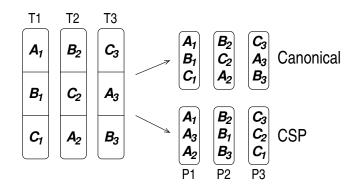

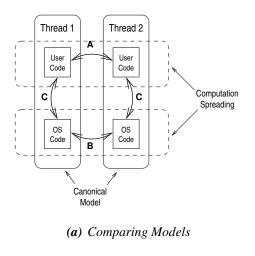

| 4.2  | Computation Spreading: An Example                                                  | 74 |  |  |  |  |

| 4.3  | OS and User Communication Profile                                                  | 78 |  |  |  |  |

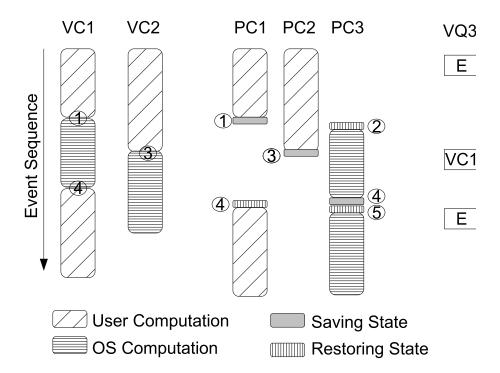

| 4.4  | CSP Implementation: Handling Contention                                            | 83 |  |  |  |  |

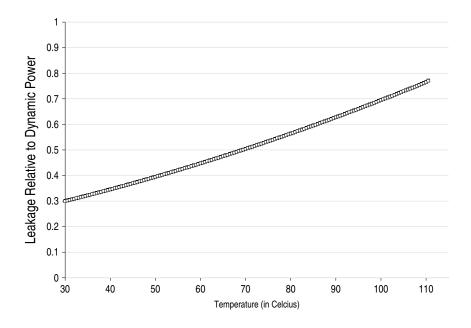

| 5.1  | Temperature Dependence of Leakage                                                  | 96 |  |  |  |  |

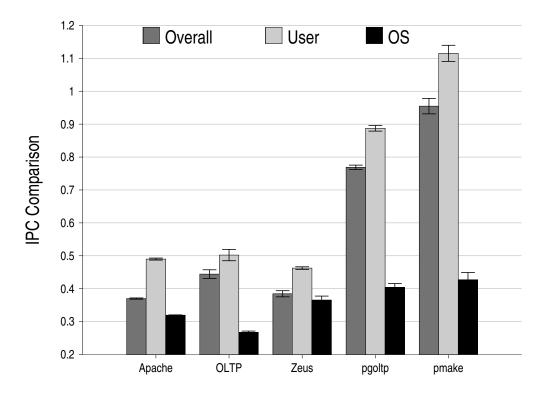

| 6.1  | Workload IPC in the baseline multicore                                             | 03 |  |  |  |  |

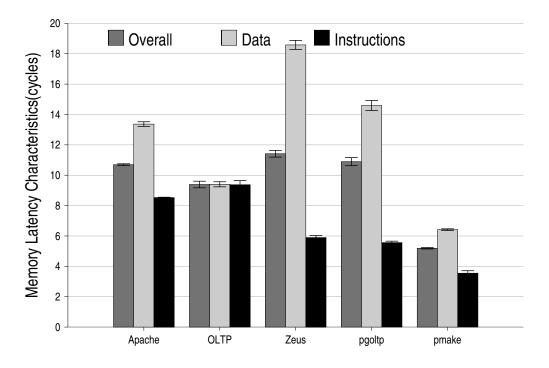

| 6.2  | Average memory latency in the baseline multicore                                   | 05 |  |  |  |  |

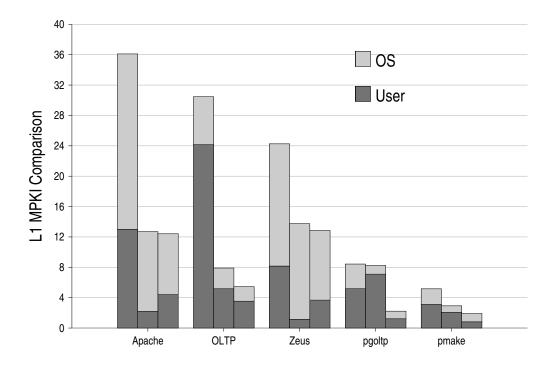

| 6.3  | L1 cache miss profile in baseline system                                           | 06 |  |  |  |  |

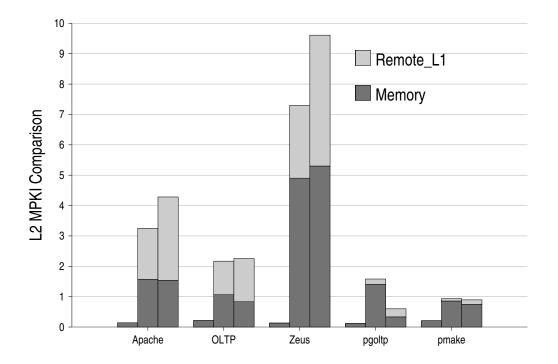

| 6.4  | L2 cache miss profile in baseline system                                           | 08 |  |  |  |  |

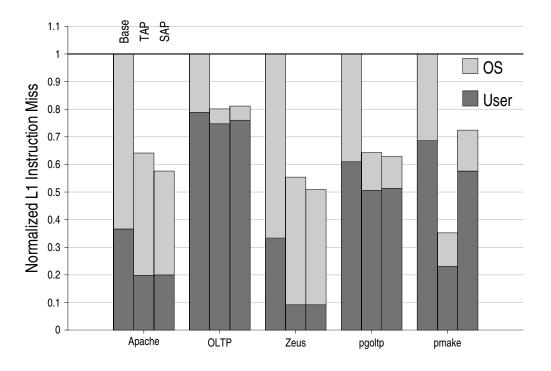

| 6.5  | L1 Instruction Miss Comparison                                                     | 10 |  |  |  |  |

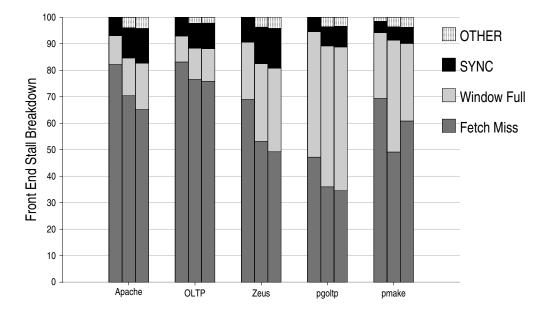

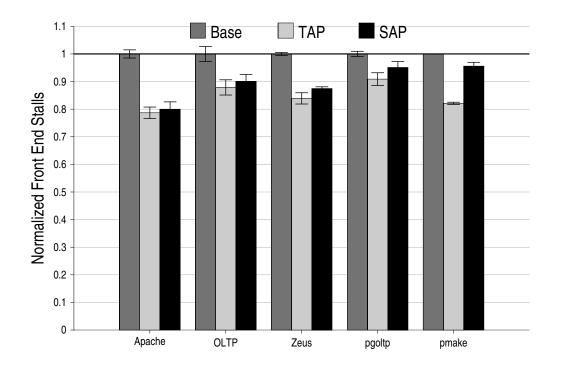

| 6.6  | Comparison of Front End Stall                                                      | 12 |  |  |  |  |

| 6.7  | Comparison of Total Front End Stall Events                                         | 13 |  |  |  |  |

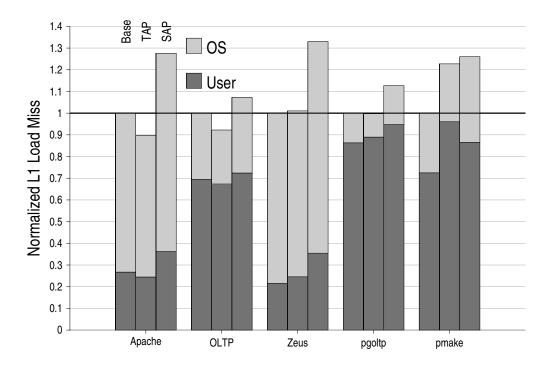

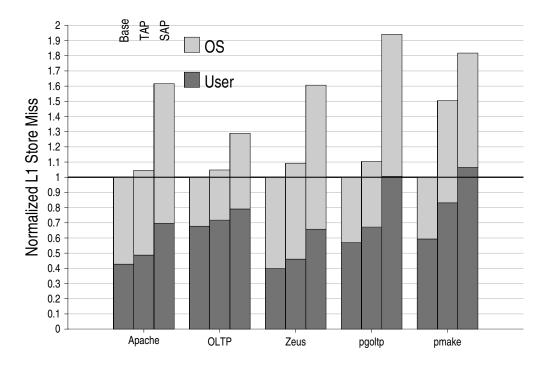

| 6.8  | Normalized L1 Load Miss                                                            | 15 |  |  |  |  |

| 6.9  | L2 Load Access Breakdown                                                           | 16 |  |  |  |  |

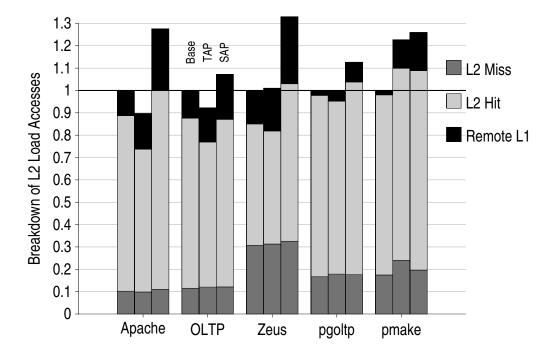

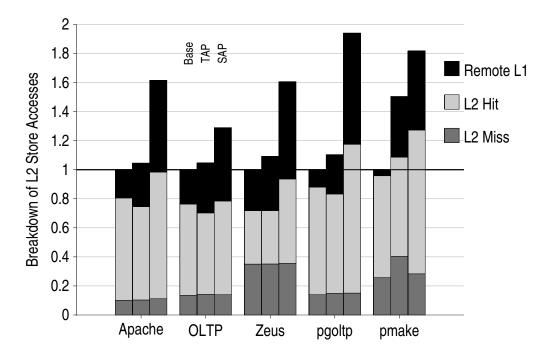

| 6.10 | Normalized L1 Store Miss                                                           | 18 |  |  |  |  |

| 6.11 | L2 Store Access Breakdown                                                          | 19 |  |  |  |  |

| 6.12 | Breakdown of Store Cache-to-Cache                                                  | 20 |  |  |  |  |

| 6.13 | Improvement in Average Memory Latency                                              | 22 |  |  |  |  |

| 6.14 | Improvement in Instruction Reference Latency                                       | 24 |  |  |  |  |

| 6.15 | Improvement in Data Reference Latency                                              | 24 |  |  |  |  |

| 6.16 | Branch mis-prediction Rates from YAGS                                              | 25 |  |  |  |  |

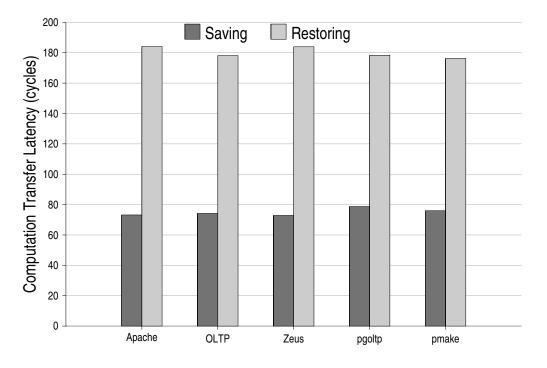

| 6.17 | Computation Transfer Latency Overhead                                              | 29 |  |  |  |  |

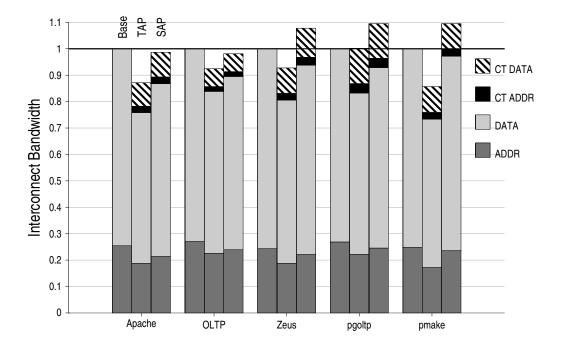

| 6.18 | Interconnect Bandwidth Comparison                                                  | 31 |  |  |  |  |

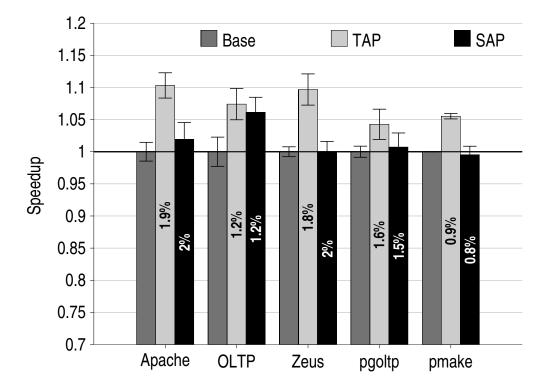

| 6.19 | Speedup Using CSP                                                                  | 32 |  |  |  |  |

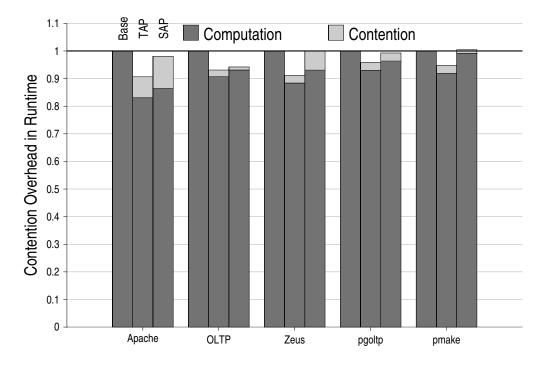

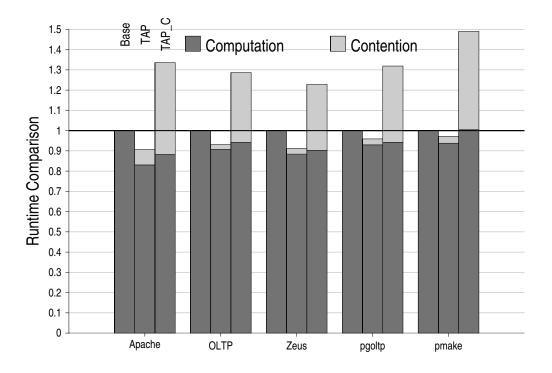

| 6.20 | Runtime Overhead from Contention                      |

|------|-------------------------------------------------------|

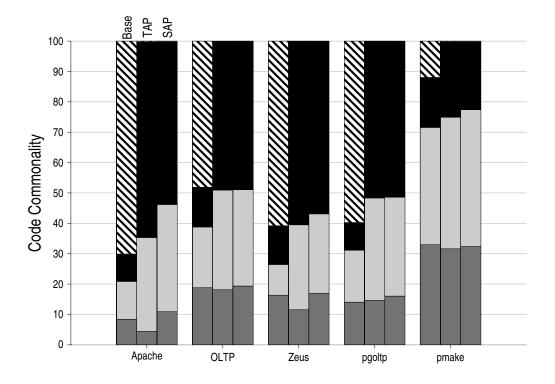

| 6.21 | Code Reuse with TAP and SAP                           |

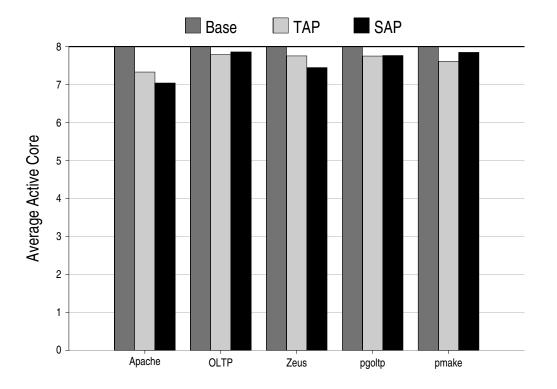

| 6.22 | Comparison of Average Active Cores                    |

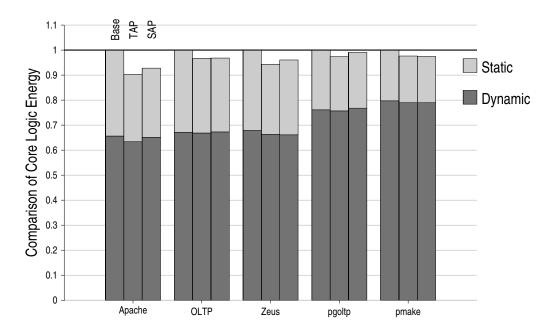

| 6.23 | Comparison of Core Logic Energy                       |

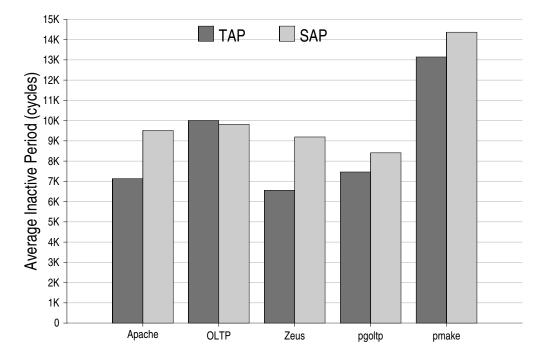

| 6.24 | Average inactive periods in cycles                    |

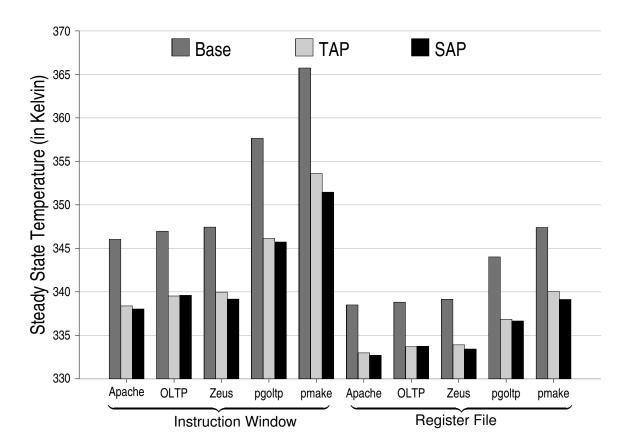

| 6.25 | Comparison of Thermal Characteristics                 |

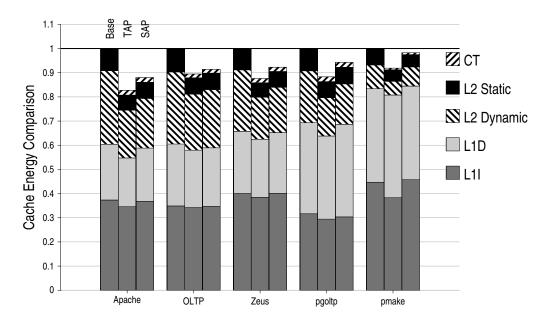

| 6.26 | Cache Energy Consumption                              |

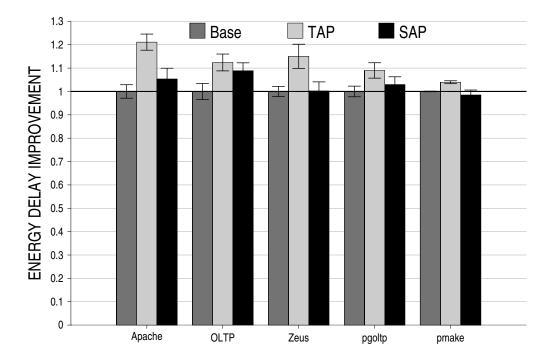

| 6.27 | Improvement in Energy Efficiency                      |

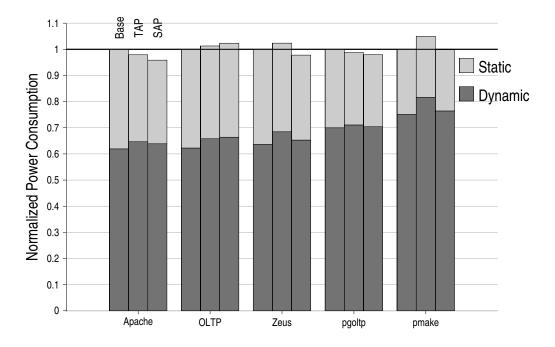

| 6.28 | Normalized Power Consumption                          |

| 6.29 | Runtime Comparison with CSP in Conventional Multicore |

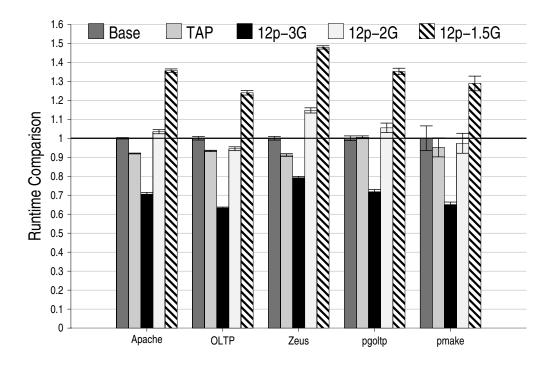

| 6.30 | Runtime Comparison with 12 threads                    |

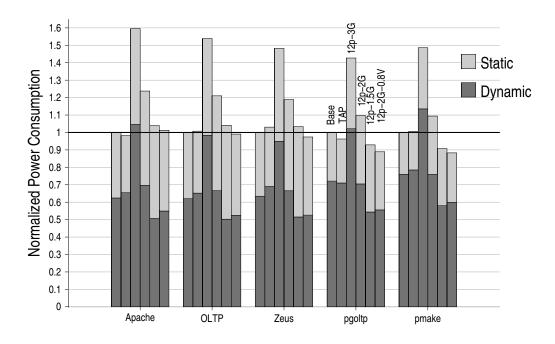

| 6.31 | Power Consumption Comparison                          |

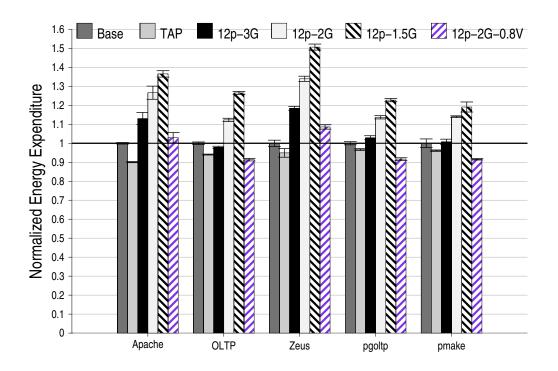

| 6.32 | Energy Expenditure Comparison                         |

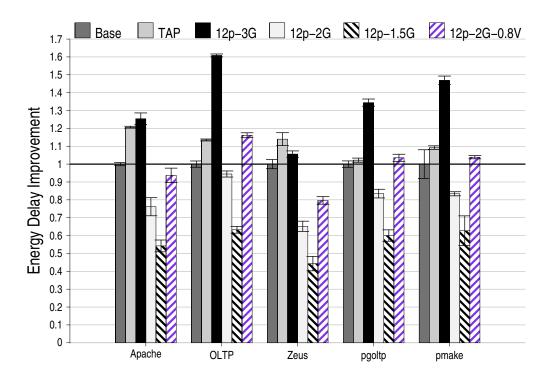

| 6.33 | Energy Delay Comparison                               |

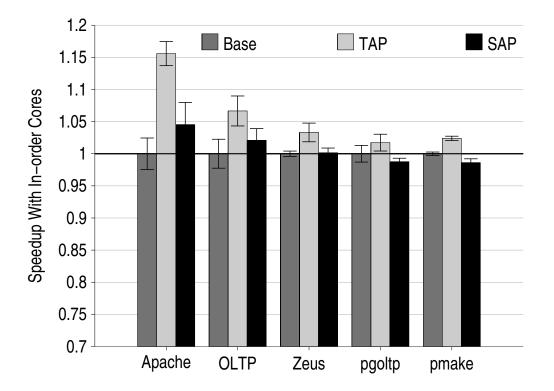

| 6.34 | Speedup With In-order Cores                           |

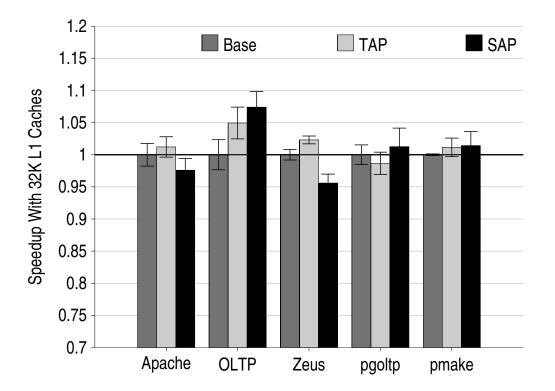

| 6.35 | Speedup With 32KB L1 Caches                           |

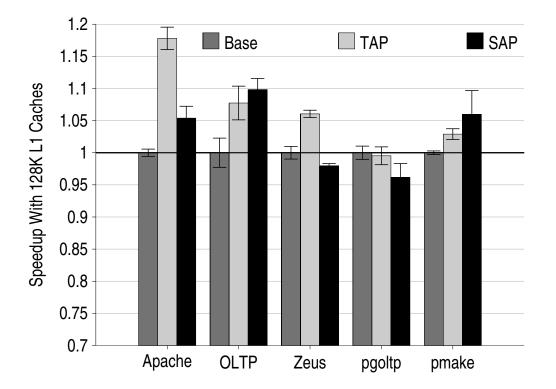

| 6.36 | Speedup With 128KB L1 Caches                          |

Chapter

# Introduction

The design of a microprocessor must conjoin two fundamental technology trends: trends in semiconductor industry that underlies the basic building block of microprocessors, and trends in software that runs on these microprocessors, dictating their functional requirements. Behind many of these technology trends, the market economics plays a critical role and deeply impacts their evolution, including the shape of microprocessors.

The most profound trend in the semiconductor technology is the scaling of transistor devices, allowing to double the number of available transistors on a chip every two years [78]. In addition to this exponential growth in devices, the scaling also comes with an improvement in the performance of each device, enabling more powerful microprocessors in successive generations. Indeed, no other industry in the history has seen the phenomenal growth that the microprocessor industry has demonstrated in the past several decades [118]. This tremendous improvement from the hardware greatly influenced the software, dramatically increasing its diversity and complexity in the pursuit to exploit the performance boost from the hardware, and improve the end-user satisfaction.

While seeking performance improvement was the most dominant requirement from an economic standpoint in the past, more recently, the market economics is increasingly demanding energy efficiency, while prohibiting the rise of complexity and associated design costs, substantially altering the design considerations of microprocessors. Consequently, the traditional strategy of exploiting more transistor resources to build increasingly complex, and power hungry monolithic processor cores, is giving way to the trend of modular designs based on multicores where a single processing core is replicated multiple times on the same die.

The emergence of multicore chips brings forth many new challenges and opportunities. Exploiting the concurrency, and the computation bandwidth afforded by these multicores is a major design challenge for the future systems, encompassing multiple layers of system designers from the hardware architects to the application developers [9]. On the other hand, the superior communication bandwidth and latency between on-chip cores inspire novel techniques to manage the aggregate core resources, so as to satisfy the demand for performance and energy efficiency. Many of these techniques may have been outright infeasible in multiprocessors built from uniprocessor chips, and therefore failed to justify serious considerations before. Yet another challenge revolves around ensuring reliable execution, especially when the inherent reliability from the hardware components is expected to fall with the technology scaling [15, 17].

All these broad problem domains are important and need substantial research, but this dissertation focuses on the second problem: exploiting more resources to improve energy efficiency and performance, without putting additional burden on the power budget. Several current generation multiprocessor chips are already operating near the engineering threshold for power, based on air cooling [94, 101]. With the exponential growth of transistor devices, the ability to put more processing cores on a chip is now poised to easily outpace the corresponding ability to power up these cores simultaneously.

In such a context, this dissertation investigates a multicore design paradigm that, by design, incorporates more processing cores than the number of cores allowed to perform simultaneous

computation without exceeding the chip power budget. The dissertation calls this multicore design paradigm an *Over-provisioned Multicore System (OPMS)* [25], reflecting the unique overprovisioning of processing core resources with respect to the power envelope. Since only a subset of the on-chip cores are active at any given time, an OPMS affords tremendous flexibility in assigning computation on processing cores, facilitating many novel techniques in this broad framework.

After presenting the general framework and implementation of an OPMS, a classic application for this design is proposed and rigorously evaluated in this dissertation, which combines the scheduling flexibility in an OPMS with the superior inter-core communication in multicore systems. Unlike the traditional approach to distribute the collective computation based on threads in a multithreaded application, this dissertation proposes *Computation Spreading (CSP)* [24]. CSP aims to collocate similar computation fragments from different threads on the same core, while distributing dissimilar computation fragments from the same thread across multiple cores. Under CSP, on-chip cores in an OPMS are dynamically specialized via retaining mutually exclusive predictive states, and function like *hardware accelerators* for appropriately assigned computation on them, without requiring any structural modification in their core micro-architecture.

## 1.1 Motivation

This section discusses the two key motivations behind this dissertation work: challenges and opportunities in multicore systems, and the demand for energy efficiency.

### 1.1.1 Challenges and Opportunities in Multicore Systems

The emergence of multicore systems in the recent years, which has now become ubiquitous across the entire computer industry, has spurred several new challenges within the context of delivering energy efficiency and performance improvement. The additional processing cores introduce new perspective in system design as efficient use of aggregate resources is becoming a major engineering challenge. Earlier, in a uniprocessor domain, all resources including caches and memory bandwidth were solely provisioned for the single computation executing on the core. However, in a multicore systems, multiple computations compete for the shared resources, and appropriately allocating resources among these computations has a large impact on overall performance and fairness of the system [27, 49]. Furthermore, the many fold increase in the pool of aggregate private resources like L1 caches and branch predictors, also imposes intriguing design challenges in terms of using them efficiently *as a whole*.

Despite these design challenges, multicore systems also offer new opportunities that compel a fresh look into the fundamental principles of the system design. Most importantly, multicore systems offer superior bandwidth and latency in communication between on-chip cores, as compared to equivalent multiprocessors built from uniprocessor chips [23]. Co-operation among different on-chip cores becomes more practical in these multicore platforms, enabling superior performance and reliability of a wide range of applications [24, 38, 121].

### **1.1.2 Energy Efficiency**

The proliferation of digital systems have led to an ever increasing global energy cost attributed to them. A recent study indicates that the energy cost from servers in data centers have doubled from 2000 to 2006 in US, and now contributes 1.5% of the overall energy consumption, equivalent to the household energy consumption in US [112]. This large rise in energy cost has now crossed the threshold where the operating cost of computers are now poised to overshoot the cost of their ownership [31]. Although many aspects of an entire system play key roles behind this surge in the energy expenditure, a substantial fraction of this growth is attributed to the rising power consump-

tion of microprocessors [31].

The increasing power consumption in a microprocessor introduces a serious problem as the heat generated in a small form factor must be removed briskly, so as to remain within the operating temperature range, necessary for the reliable execution of the devices. However, air cooling used by commodity microprocessors—prevalent in both desktop and server platforms—has an engineering limit of the amount of heat it can remove [55], dictating the power budget. Moreover, economic considerations to save operating cost further restrict the power envelopes in current multicores [91].

With the doubling of transistor devices in microprocessor chips, their power consumptions also increased, but did not double in successive generations, as substantial benefits in energy efficiency was drawn purely from technology scaling [15]. As the size of the transistor scaled with successive technology generations, the energy efficiency also improved from voltage and capacitance scaling. But in recent years, voltage scaling has almost stopped due to various constraints from the device engineering [16,29], limiting the energy efficiency gained from technology scaling. Consequently, system designers are now expected to focus on various techniques at the architectural level to control the power consumption of microprocessors [56].

An indication to fulfill this expectation is seen in several current generation microprocessors that show a trend in increasing functional diversification where a diverse pool of microarchitectures, performing specialized functions, are integrated [55]. Several research proposals have also appeared to advocate more of such specialized components [5, 28, 39]. Broadly termed as *hardware accelerators*, these special purpose circuit components excel in both power and performance metrics. Compared to general purpose components, such custom designed components often deliver orders of magnitude improvement in power-performance for the specific computation they were intended [56]. Several microprocessors already include such hardware accelerators (e.g., the cryptographic unit in Sun's Niagara [82]), and the ITRS roadmap envisions a continuation of this trend [55].

# **1.2 Thesis Contributions**

This dissertation makes several contributions in the context of energy efficient multicore designs. First, it defines an abstract model for the power constraint in microprocessors, and demonstrates its use in reasoning about different multicore configurations in the early phase of their designs. Second, in light of the increasing power constraint in successive technology generations, this dissertation proposes Over-provisioned Multicore System (OPMS), which by design provisions more core resources on a multicore than the maximum possible simultaneously active cores for its target power budget. Such a design is in a stark contrast with the conventional multicores that target full utilization of core resources. Nevertheless, this design paradigm captures the fundamental technology trend where integrating cores comes at a much lower marginal cost than powering them up. Third, this dissertation proposes Computation Spreading: a new model for distributing collective computation from multithreaded applications, and delves into a rigorous evaluation of its performance and energy efficiency.

### **1.2.1** Simultaneously Active Fraction

While the power constraint is rapidly growing in importance for microprocessor designs, estimating the extent of this constraint at an early phase of a microprocessor design cycle imposes a serious challenge [19]. To mitigate this challenge, this dissertation develops an abstract model for the power constraint by expressing it in a more tractable area metric: *Simultaneously Active Fraction (SAF)*. SAF of a chip is defined as the maximum fraction of on-chip devices that can be active at the same time, while still remaining within the chip's power budget, also known as the

#### Thermal Design Power (TDP).

Combining the expression derived for the SAF, and the expected transistor characteristics for several upcoming technology generations [55], the dissertation finds that the SAF is likely to shrink substantially in future microprocessors, limiting the fractional resources that can be active at any given time. Using analytic models, two concrete applications are then presented to illustrate the impact of shrinking SAF in multicore design considerations.

### 1.2.2 Over-provisioned Multicore System

In the light of various technology trends, this dissertation investigates a novel multicore design paradigm, which embodies a class of multicores that by design integrates more cores than allowed by its power budget. Throughout this dissertation, such a multicore is referred as an *Overprovisioned Multicore System (OPMS)* [25]. From a system design perspective, the OPMS design paradigm designates a substantial shift in design considerations from the past, where increasing the processing core utilization was of prime importance. Instead, this dissertation proposes a novel multicore paradigm where power is considered more critical, enabling a dynamic distribution of the available power budget among the on-chip cores. Since only a subset of the available cores is engaged in computation, the inherent flexibility of assigning computation on the cores facilitates various techniques to dynamically specialize the on-chip cores, yielding benefits in both runtime and energy efficiency.

### **1.2.3** Computation Spreading

Finally, this dissertation proposes *Computation Spreading* that combines the scheduling flexibility of an OPMS, and the superior communication in multicore systems, to build a co-operative framework among on-chip cores to perform the collective computation from multithreaded applications [24]. Conventional multicores distribute the computation on such applications based on threads, resulting in a poor utilization of predictive structures that exploit properties of instruction streams (e.g., instruction caches and branch predictors). In contrast, CSP localizes similar computation from multiple threads onto a single core, while distributing dissimilar computation from a single thread onto multiple cores. Consequently, on-chip cores in an OPMS retain mutually exclusive predictive states, and function as *hardware accelerators* when appropriate computations are assigned on them that best exploit those predictive states.

## **1.3 Dissertation Outline**

Rest of the chapters in this dissertation are organized as follows. Chapter 2 presents the model for the Simultaneously Active Fraction, with a detailed discussion on the background concepts of area and power constraints, the expected trends of SAF, and its application in the early phase of a microprocessor design. Chapter 3 introduces the primary contribution of this dissertation — Over-provisioned Multicore Systems (OPMS), presents a broad discussion on its design aspects, and the specific implementation adopted for the rest of the dissertation. Chapter 4 illustrates Computation Spreading with its motivation in the context of multicore designs and OPMS, and the specific flavor of CSP adopted in this dissertation: separating OS and user computation. Chapter 5 describes the detailed methodology used throughout this endeavor. Subsequently, Chapter 6 presents a rigorous evaluation of performance and energy efficiency of the OPMS. Finally, Chapter 7 summarizes the main contributions detailed in the previous chapters, and outlines possible research directions stemming from this dissertation.

l Chapter

# Simultaneously Active Fraction

Driven by the increasing demand for energy efficiency at the system level, power consumption is rapidly emerging as one of the first order design considerations in modern microprocessors [80]. In the general-purpose microprocessor design space, power limited designs designate a significant paradigm shift from the area limited designs of past several decades [48]. While several architectural intuitions deal well with area, allowing a hierarchical and modular design strategy to be effective, considering power consumption at the early phase of a similar design flow imposes a major challenge.

Although one can accurately estimate transistor level power consumption, transcending that estimation at the chip level requires aggregation over many levels of abstraction, substantially complicating the assessment. For example, power consumption of a single transistor may vary widely depending on the micro-architectural circuit component it belongs to. Even within a given small circuit component, the power consumption may vary based on its topological placement, activity and physical characteristics (e.g., width). Consequently, it is practically impossible to accurately estimate the power consumption of a system at an early phase of its design cycle [19].

Given this technical difficulty, this chapter develops an abstract model for the engineering con-

straint imposed on a microprocessor design due to its power consumption. The key objective in this pursuit is *not* to come up with an accurate estimation of power consumption of a particular design, but to develop a first order model of chip level power constraint, and investigate the technology trend of this metric. This dissertation develops this model for power constraint by expressing it as an area constraint. This chapter defines this expression as a metric, referred as the *Simultaneously Active Fraction (SAF)*: the maximum fraction of on-chip devices that can be active at the same time, while still remaining within the chip's power budget, also known as the *Thermal Design Power (TDP)*.

The chapter begins with a background discussion of area and power constraint in the context of a microprocessor design in Section 2.1. Next it develops the first order model of SAF in Section 2.2, and presents quantitative trends of SAF based on prevailing technology characteristics. Next, it describes the role of SAF reduction in future microprocessors in Section 2.3. Then, the chapter presents two concrete examples to demonstrate the use of SAF in the early phase of power constrained multicore designs. First, it incorporates the power constraint in a recent analytic model for determining speedup from multicore chips in Section 2.4. Second, it shows the application of SAF in designing multicores for multithreaded server applications in Section 2.5. The chapter concludes with a summary in Section 2.6.

# 2.1 Area and Power Constraint

This section presents the background concepts of the two key engineering constraints in a microprocessor design: area and power. Fundamentally, the area constraint is well defined, and it is *statically* met by the collective presence of devices, each of them occupying a certain fraction of the area. In contrast, the power constraint is satisfied dynamically, as the mere presence of a device is not sufficient to determine its power consumption. Different ensemble of devices can operate at a wide range of power levels at different times, lending a dynamic nature to the total power consumption. Even at a fixed total power, the selection of devices consuming power may differ. A detailed discussion of these constraints, and the design implications of satisfying them concurrently—a necessary requirement for microprocessor designs—is presented next.

### 2.1.1 Area Constraint

The area of a micro-processor chip is a function of the size of devices, and the total number of devices integrated onto it. The total area constraint can then be expressed as:

$$A_{die} = \sum_{i=1}^{N} D_i$$

where  $A_{die}$  represents the die area constraint, N is the total number of devices integrated on a die, and  $D_i$  is the size of an individual device i. The total available area for a given implementation is determined by various factors such as form factors, expected die yield, wafer size, and economic consideration for the target market place [55]. Despite the complex interaction of several factors, ITRS roadmap predicts a constant die-size for the foreseeable future, especially for high-performance microprocessor units [56].

After the total area constraint or die size is established, it must then be met by the aggregate sizes of integrated devices. As the equation indicates, one can either reduce the size of each device or simply remove the required number of devices to satisfy this constraint. However, within a given technology generation, there is a limit for the minimum device size. Once this minimum size is attained for all the integrated devices, violation of the area constraint can only be rectified by downsizing the device count. Of course, performance considerations may dictate larger device sizes in various critical micro-architecture components [118], thereby requiring further reduction

in the aggregate devices.

### 2.1.2 **Power Constraint**

Similar to the area, the total chip power is an aggregation of power from each device. The total power is constrained by the cost-effective cooling capacity of a high volume micro-processor designs [53]. More recently, the demand in energy efficiency is imposing severe restrictions on the chip power budget [91]. Collectively, these two trends indicate a constant chip power budget, even under optimistic assumptions. This power constraint can be expressed as:

$$Power_{die} = \sum_{i=1}^{N} P_i$$

where  $Power_{die}$  is the chip-level power constraint,  $P_i$  is the power consumed by the device *i*, while *N* is the total number of devices as before. While the minimum area of a transistor device  $(D_i)$  is set by the technology generation, there is no such set minimum for device level power consumption: devices can exist on a die without consuming power. Within a given implementation, the power consumption of on-chip devices also tends to vary substantially [19, 20]. Thus, unlike the area constraint, where the presence of a device results in a reduction of total available area, the mere presence of on-chip devices may not reduce the available power budget. This key distinction allows a variety of design strategies to meet the chip level power constraint (e.g., half of the total devices consuming the entire power budget, while the rest are in zero power mode).

### 2.1.3 Satisfying Area and Power Constraints

A viable microprocessor design must concurrently satisfy both its area and power constraint as determined by the form factor, energy efficiency requirements, economic considerations and so

forth. At a high level, the area constraint limits the number of aggregate devices on a single chip, which in turn will limit micro-architecture components (e.g., processing cores, caches, special purpose accelerators) that can be realized within the die area. On the other hand, for each individual device power level, the chip power constraint, typically referred as its Thermal Design Power (TDP), limits the total number of devices consuming power at that level. As the device power level varies, the total number of devices allowed at that level will also change. Furthermore, the ability to maintain devices at (or near) the zero power level, allows different collection of on-chip devices, and the corresponding micro-architecture they constitute, to consume power at different times.

Therefore, the power constraint of a given implementation can be dynamically satisfied by different subsets of on chip devices. Any given subset of such devices also have a certain area, but their aggregate area is a fraction of the total available chip area. This dissertation defines such a fractional area as the *Simultaneously Active Fraction* (*SAF*) of a chip. Formally, the SAF of a chip designates the largest fraction of the on-chip devices, and their collective area thereof, which is allowed to remain simultaneously active and consume power without violating the chip TDP.

The SAF captures the chip TDP in a more tractable metric for the architects: area. The maximum value of an SAF is 1, where all the on-chip devices can actively consume power. In practice, typical implementations have lower values of SAF. Therefore, from the power perspective, the devices are *over-provisioned* as the power constraint bars concurrent active power consumption in all of them. A key contribution of this dissertation is to build a framework to understand the concept of over-provisioning in the context of multicore designs and their TDP. However, this chapter focuses on a thorough understanding of the SAF, its technology trends, impact on power conservation, and applications of SAF during the early phase of microprocessor designs.

# 2.2 SAF: First Order Model

This section develops the model of SAF, and inspects the technology trends of it. The key objective behind inspecting the SAF trends is to provide an area perspective of the power constraint in future microprocessor designs.

### 2.2.1 Analytic Model

To develop the SAF model, this section begins with a discussion on the fundamental transistor level power characteristics and their recent trends, which are crucial to understand the SAF trends. A basic CMOS transistor device has two different modes of power consumption: *dynamic power* and *static power*.

#### 2.2.1.1 Trends in Dynamic Power

Dynamic power is consumed through the switching of a transistor, which results in charging or discharging of the device. Because of the charging and discharging, a transistor can be modeled as a capacitive load, driven by the supply voltage of the transistor [118]. Based on the switching frequency (f), the dynamic power of a device is given by the following equation:

$$Power_{dynamic} = C \cdot V_{DD}^2 \cdot f$$

where C is the capacitive load and  $V_{DD}$  is the supply voltage.

To understand the transistor level trends in dynamic power, one can simply investigate different parameters in the equation shown above. Clearly, the most dominant factor is scaling down the supply voltage  $V_{DD}$ , which yields a quadratic reduction in power. In the semi-conductor technology, *scaling* can have different implications in different contexts. For example, scaling of voltage and capacitance implies a reduction of these parameters, while frequency scaling usually implies an *increase*. However, for the ease of comprehension, scaling will be used to explicitly indicate a reduction throughout this chapter.

Historically, the supply voltage was scaled, almost in tandem with the device feature size, after the semi-conductor industry adopted constant electric field with technology scaling [15]. However, more recently, the scaling of voltage has slowed down considerably due to the reliability concerns in sub-micron devices, and the inability to scale the threshold voltage [47]. Several leading fabrication vendors are expecting a flat supply voltage in the near future [16, 29]. This diminishing return in power reduction from voltage scaling is the most fundamental reason behind the increasing power consumption in microprocessor chips [15].

On the other hand, scaling the capacitance gives a linear reduction in dynamic power. Although, the capacitance was scaled almost linearly with the feature size, in recent years it is showing signs of slowing down [76]. To understand this slowdown, let us inspect the governing equation for the transistor capacitance:

$$C_{total} = C_{intrinsic} + C_{parasitic}$$

Fundamentally, the intrinsic capacitance ( $C_{intrinsic}$ ) is dependent on the gate length, and scales down as the device size shrinks, but the parasitic component ( $C_{parasitic}$ ) is independent of the gate length [104]. In past technology generations, the intrinsic capacitance made up the bulk of the total capacitance [104], thereby resulting in a near linear reduction of the total capacitance with the technology scaling. On the other hand, the parasitic capacitance is increasing with the technology scaling, and is rapidly becoming a significant fraction of the total capacitance [76]. Consequently, the overall capacitance scaling is now slowing down.

Unlike the supply voltage and load capacitance, the frequency has been increasing in successive

| Characteristics | Ideal/Theoretical         | Real                                                 |

|-----------------|---------------------------|------------------------------------------------------|

| Supply Voltage  | Linear scaling (0.7) [15] | Marginal scaling [16,54]                             |

| Capacitance     | Linear scaling (0.7) [15] | Scaling slowing down, sub-linear [76]                |

| Frequency       | 43% (1/0.7) increase [15] | Target 17%, likely smaller in future multicores [56] |

| Dynamic Power   | 50% improvement [15]      | Limited improvement [16]                             |

Table 2.1: Technology scaling trends of Dynamic Power

technology generations. The scaling of transistor devices leads to a reduction in its intrinsic switching delay, allowing a commensurate increase in the clock frequency [118]. Increasing the clock frequency was also one of the most effective techniques for improving performance. Moreover, the increase in power consumption from the rise in frequency was already more than compensated by the scaling of supply voltage and capacitance, resulting in an overall improvement in device level energy efficiency [15]. However, as the performance improvement from increasing the processor clock frequency started to slowdown, with the concurrent trend in diminishing returns in power consumption improvement from the supply voltage, aggressively increasing the frequency fell out of practice in modern microprocessor implementations. The ITRS predicts only limited increase in frequency for logic components [56], even for high performance microprocessors.

Table 2.1 presents a summary of the above discussion. Combining all these trends, it appears that the improvement in dynamic power is likely to slowdown dramatically over the next several technology generations.

#### 2.2.1.2 Static Power Trends

In contrast to the dynamic power, static power from a transistor is consumed due to a small continuous discharge mechanism, otherwise known as *leakage*. There are several modes of leakage, but they can be broadly classified as sub-threshold, gate, and reverse-biased drain-and-source substrate junction band-to-band-tunneling (BTBT) [1,93]. These leakage mechanisms have strong dependence with several second order device parameters (e.g., oxide thickness, doping concentration, temperature), in addition to the supply and threshold voltage of these devices. Because of these second order effects, it is more challenging to accurately estimate transistor level trends in static power, and its overall contribution to the TDP.

However, the overall static power due to leakage has been steadily growing over the past several technology generations [22, 93]. Sub-threshold leakage, which has a exponential dependence with the threshold voltage, increased rapidly with the scaling of threshold voltage, and typically dominated the leakage currents [47]. More recently, threshold voltage has almost stopped scaling to counter this sub-threshold leakage, but the scaling of other device parameters (e.g., oxide thickness) caused a rise in gate leakage and BTBT. Subsequently, both these two leakage mechanisms now constitute a substantial fraction of the total leakage [1]. Despite this steady rise, several techniques have shown tremendous potential in mitigating the leakage (e.g., high- $\kappa$  metal oxides, double gate devices). Within a technology generation, circuit designers choose the optimum techniques for controlling the leakage energy, determined by the optimization of the overall power-performance of the system [47].

Collectively, the trends in dynamic power and static power imply that the total power from individual devices (referred as  $P_{Device}$  next) is likely to improve very slowly in the next several technology generations.

#### 2.2.1.3 SAF

The total power of a given micro-processor is simply an aggregation of the power consumed by each device on the chip. As the physical characteristics, activity and various key parameters of transistors vary widely across a given integrated circuit, the first-order model adopts a uniform transistor characteristics. Consequently, the model assumes that the power consumed by each in-

dividual transistor is identical across the entire chip. Therefore, at the system level, total aggregate power consumption is obtained by the aggregation of individual device power over the total number of active devices. A more detailed discussion on the justification and limitations of this assumption is presented later in Section 2.2.3.

$$Power_{chip} = Power_{Device} \cdot Number of Active Devices$$

$$= Power_{Device} \cdot (SAF \cdot Total Device Count)$$

(2.1)

The *Total Device Count* is exponentially increasing with each new technology generation, but the *Individual Device Power* (when active) is not decreasing at the same rate. Meanwhile, the total  $Power_{chip}$  remains relatively constant due to the limitations of cost-effective cooling and packaging techniques [53]. Thus, the SAF must decrease. Qualitatively, this reduction of SAF in successive technology generations designates the increasing power constraint at the early phase of a microprocessor design.

In order to provide a system-level perspective for architects, the next section quantitatively analyze these trends across different technology generations and shows the growing power constraint illustrated through the continuous reduction of SAF.

### 2.2.2 SAF Trends: A Quantitative Analysis

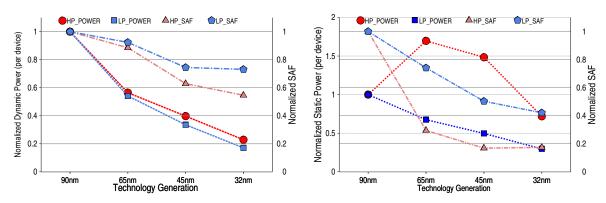

Several technology assumptions are necessary for a quantitative analysis of the SAF trend. For the sake of simplicity, let us consider the performance characteristics of two typical N-MOSFET devices, one designed for high-performance (HP), and the other for low power (LP) [54]. HP devices use a low threshold voltage and a nominal supply voltage, while the LP devices use a higher threshold voltage and a scaled supply voltage. Together they encompass the range of devices, with diverse operating conditions, typically seen in high-performance microprocessors [54]. Furthermore, the estimation assumes that the entire chip is built with these devices, and that the chip size remains constant, resulting in a doubling of the number of devices every generation [53]. Based on the power consumption of a single device, determined using the MASTAR tool [57], the SAF is computed at each technology generation as the fraction of the total devices that account for a given TDP (which is assumed to remain constant across technology generations). The results, normalized to the 90nm generation, are shown in Figures 2.1(a) and 2.1(b).

*(a)* Dynamic power trend and SAF due to dynamic *(b)* Static power consumption trend per device and SAF power exclusively. due to static power exclusively.

Figure 2.1: SAF trends

The trend in dynamic power, and the resulting SAF when considering dynamic power alone, is shown in Figure 2.1(a). The figure assumes a 17% improvement in switching frequency in successive generations based on the ITRS guidelines for logic components [54]. HP\_POWER and LP\_POWER show the power consumption of a single HP and a LP device, respectively, while HP\_SAF and LP\_SAF show the SAF for HP and LP devices, respectively. The improvement in dynamic power efficiency is less than the improvement in device integration capacity, in both types of devices. Consequently, Figure 2.1(a) shows a fall in the SAF in each successive generation. The

decline in the SAF is more pronounced in the HP devices than LP due to relatively smaller gains in the device level power consumption and energy efficiency. In summary, it is expected that the dynamic power, even when considered in isolation, will continue to limit ways to use aggregate resources due to the gradual reduction in the SAF.

Static power due to leakage is an additive power component. Figure 2.1(b) shows the trend in static power per device, along with the SAF when considering only static power. For high performance devices, a dramatic reduction in SAF is observed as, unlike dynamic power, the static power of individual devices is *rising* in successive technology generations, till the 32nm technology node. At the 32nm technology, the adoption of FINFET devices is expected to substantially reduce the sub-threshold leakage, leading to an estimated improvement in static power compared to previous technology generations [7]. Technology experts expect that leakage-induced static power will be mitigated by employing various circuit and process manufacturing techniques such as high  $\kappa$ -dielectric [54], FINFET devices [7], and so forth. However, it is still likely to pose additional constraints on aggregate resource usage.

While the analysis above provides a relative trend, the actual SAF of a real implementation depends on various other factors not considered in this analysis. These factors include several device-level parameters, circuit design techniques, purpose of the transistors (logic vs. memory), percentage of transistors on latency-critical paths, the temperature and activity distribution, among others. Regardless, in the absence of a dramatic alteration of device properties, this downward trend of the SAF will persist and thus processor designers will be forced to develop innovative techniques to reduce the SAF.

### 2.2.3 Limitations

The primary purpose of the SAF model is to provide a first order impact of power constraint in microprocessor designs across multiple technology generations. To this effect, the model assumes a uniform power consumption of transistor devices across the entire chip. In reality, on-chip transistors in a typical implementation operate at a wide range of power levels. Moreover, the power consumed in driving the wires was not considered explicitly. A more complicated model that assumes certain distribution of power consumption among on-chip devices may give a better absolute measure of SAF. However, the applicability of such a complex model becomes limited as a different microprocessor implementation may substantially alter the underlying assumption about the distribution of power consumption among on-chip devices.

Instead, the simplified model proposed in this work attempts to develop the intuition behind the impact of power constraint in future microprocessor designs. The quantitative trend illustrated in the previous section shows the necessary levels of SAF reduction required through architectural means, after accounting for the energy efficiency obtained from the technology scaling exclusively.

# 2.3 Targeting SAF for Power Reduction

Based on Equation 2.1, this dissertation broadly classifies power reduction techniques into two classes that target the individual device power or the SAF, respectively, and discuss each in turn.

### 2.3.1 Targeting Per-Device Power is Insufficient

**Voltage Scaling** The most effective technique for chip power reduction in past technology generations has been voltage and frequency scaling (VFS). Within a technology generation, voltage scaling, in combination with the necessary frequency scaling, yields a cubic reduction in individual device power [118]. However, supply voltage reduction is reaching a plateau in current process technology and is unlikely to continue in future technology generations. For example, voltage scaling exponentially increases the *fault rate* due to particle strikes [122], which is already a serious reliability concern. In addition, with the limited flexibility in lowering the threshold voltage due to leakage concerns, maintaining a significant voltage over-drive is becoming mandatory for tolerating increasing process variation in scaled devices [18]. Therefore, this dissertation makes the fundamental assumption that voltage scaling will soon become infeasible—a conclusion shared by others as well [16, 29, 35].

**Frequency Scaling** Frequency scaling still remains a practical means for reducing dynamic power by simply reducing the clock rates of processing cores and caches<sup>1</sup>. The expectation is that frequency scaling can reduce power without incurring a significant performance impact, since several circuit components expend energy even when they are not doing useful work (for example, while waiting on a load). However, frequency scaling, in the absence of voltage scaling, is unable to fulfill this expectation for several reasons. First, widely employed techniques like aggressive clock gating already target the same power saving opportunities as frequency scaling, and save a significant amount of the overall power (up to 40% by one estimate [58]). Second, since frequency scaling by itself has no effect on static power, the impact on total power saving is further reduced. Thus, *the relative power reduction lags the relative frequency scaling*. Both compute bound and memory bound workloads are negatively impacted by frequency scaling due to this lag in power savings.

Compute bound workloads spend a major fraction of their execution cycles in generating new values and satisfying their inherent data dependencies, with limited stalls from their memory ref-

<sup>&</sup>lt;sup>1</sup>Frequency scaling does not restrict the active computation area, but affects allowable SAF by reducing individual device power.

erences. Core pipeline logic such as functional units and register files remain busy and heavily utilized, and a high throughput from these micro-architecture components directly translates into a higher overall performance in these applications. Frequency scaling decreases the throughput of the core pipeline logic, thereby decreasing the pipeline performance. Therefore, the performance of compute bound workloads can degrade linearly with frequency scaling, defeating the purpose of improving energy efficiency metrics (e.g., energy-delay product).

Unlike compute bound workloads, the performance loss of memory-bound applications is more resilient to frequency scaling [68]. These workloads spend a majority of their execution on waiting for memory references [3], resulting in a low IPC (instruction per cycle), and observe lower activity in their core pipeline logic. Consequently, decreasing the pipeline throughput *does not* degrade the runtime linearly, potentially yielding a benefit in energy efficiency. However, because of lower utilization of core pipeline logic from their low IPC, substantial dynamic power from the core logic can be saved by aggressive clock-gating [58]. Savings in the dynamic power from the total power budget, increases the relative contribution from the static power component, which remains unaffected by frequency scaling. Thus, the effectiveness of frequency scaling in saving total chip power is dampened, leading to a reduction in energy-efficiency benefits in memory bound workloads as well. Collectively, this dissertation finds that frequency scaling alone is detrimental to power-performance characteristics of several workloads (details in Chapter 6).

In a multicore processor, frequency scaling can further be applied on a per-core basis. However, per-core frequency scaling has two additional pitfalls. First, it can lead to unpredictable performance characteristics because of the resulting asymmetric execution substrate [10]. Second, in multithreaded workloads, which often require thread synchronization, threads executing on a slow core can negatively impact the performance of *all* threads (e.g., by increasing the lock wait time), causing loss of overall performance and energy [87]. To avoid these problems in complex multithreaded applications, this dissertation focuses on frequency scaling the entire multicore (Chapter 6).

### **2.3.2 Existing SAF Reduction Techniques**

Given these practical challenges of reducing the individual device power without dramatic performance degradation, SAF reduction is likely to be increasingly important as a key power reduction technique in future technology generations. While it will be important to develop new forms of SAF reduction, it is instructive to briefly review the current techniques for SAF reduction.

**Fine-grained Techniques** The best example of fine-grain SAF reduction is clock gating within a processor core. Clock gating temporarily suspends the switching activity for transistors which are not involved in computation on a given cycle. Similar techniques can be applied to reduce leakage power as well (e.g., dynamic sleep transistors [110]). Such techniques are very effective for reducing SAF, but they have practical limits. In particular, the cost of additional hardware required to manage aggressive clock gating can often outweigh the benefits [58], encouraging designers to strive for additional SAF-reduction techniques, especially coarse-grain techniques that operate at higher levels of the design.

**Coarse-grained Techniques** Because of lower overheads, further SAF reduction is more effective when applied at a coarser granularity. Devoting a substantial fraction of the chip area to caches instead of cores is one method to achieve this objective since, by design, the second or third level (L2 or L3) caches have low activity (only a small fraction of cache lines are accessed in any given cycle). Additional SAF reduction can be achieved by putting large sections of the caches into a sleep state, reducing both leakage and dynamic power [94]. However, provisioning more resources for caches yields diminishing returns in performance, even for workloads with large memory footprints, as demonstrated by recent studies [13, 59, 96].

# 2.4 Application of SAF: Speedup from Power Constrained Multicores

The previous sections have discussed the SAF and its trend based on the prevailing technology characteristics in details. The next two sections will demonstrates two concrete examples to demonstrate the application of SAF in reasoning about power limited multicore designs in their early design phase.

In their recent work on multicore chips, Hill and Marty [46] presented an analytic model to estimate the performance of various workloads on three different categories of multicore designs. Their cost model assumes that on-chip compute resources are limited (e.g., by area, power, or some combination thereof). However, with the increasing dominance of power considerations dictating the microprocessor design, whereas the available resources continue to grow exponentially, the area and power constraint must be decoupled. Decoupling these two constraints allows to model the active compute resources separately from the available resources, and offers a more flexible framework for modeling power and area constraint. Using SAF as a proxy for the power constraint, this section will discuss how to incorporate SAF in the analysis to achieve this decoupling, and its subsequent impact in the results and major conclusions.

## 2.4.1 Background

### 2.4.1.1 Cost Model

A brief discussion on the multicore cost model adopted by Hill and Marty is presented first. A multicore chip is divided into two components: *processor core components* that integrates *n base core equivalents* (*n* BCEs) and non-core components that include shared caches, interconnect, memory controllers and other essential microprocessor structures. Total area devoted to both these components are constant throughout the analysis. The processor core component can be configured in different ways, which will be determined by the specific multicore configuration this analysis inspects. In contrast, the non-core components remain identical across all the multicore configurations. While the configuration of the non-core components can clearly impact the performance, this section focuses on processor core area to understand the broader qualitative trend.

### 2.4.1.2 Performance Model

The performance and workload model for this analysis is driven by Amdahl's law [6]. Under Amdahl's law, the workload is modeled as two distinct phases: a sequential and an *infinitely* parallel phase. The performance obtained from the sequential phase is limited by the performance extracted from a single processor, while the parallel phase is only limited by the number of processing cores used to execute it. For a program that spends f fraction of its time in the parallel phase, on a multicore consisting of n processing cores, the speedup from this law is given by:

$$Multicore_{speedup} = \frac{1}{1 - f + \frac{f}{n}}$$

## 2.4.2 Hill-Marty Model Extension: Incorporating Power Constraint

The cost model described above does not separate the active compute resources from the available compute resources that are limited by the area constraint exclusively. Incorporating the power consumption within this framework, which is perhaps the more significant cost in modern multicore designs, is possible but requires it to closely tie into the area cost. In other words, a designer can limit the are devoted to the computation resources solely for a particular target power consumption. However, modern multicore chips already contain significantly more area than that can be powered up simultaneously, resulting in an SAF < 1. For example, 21% of the total area, implenting the processor cores in Intel Itanium 4, accounts for 59% of the overall power budget [101]. Therefore, for a more realistic modeling of power constraint in this analysis, one must *decouple* the area and power constraint.

As explained in Section 2.1.3, although the area and power constraints must be satisfied simultaneously for a viable implementation, particular mechanisms to satisfy each of them are fundamentally different. The area constraint is statically satisfied by the number of devices present on a chip, dictating the number of processor cores realized from them. In contrast, the power constraint of a given implementation can be dynamically satisfied, dictating which particular cores consume power. Decoupling these two constraints in such a manner allows to better model the current multicore systems that are primarily power limited with abundant area.

Thus, this analysis will include the SAF of this processor core area to represent the power constraint, in addition to the processor core area itself that satisfies the available area constraint. Following this basic modification, the analysis investigates the performance impact of different multicore chips with the variation of the SAF. For example, although the core area will contain n BCEs, depending upon the SAF, the number of BCEs that can be simultaneously employed for active computation will vary. An SAF of 1/2 in a multicore will imply that only n/2 BCEs can be

employed to execute code at any given time. This section will use  $\alpha$  to denote the SAF of the core area, where  $0 < \alpha \le 1$ .

### 2.4.3 Symmetric Multicore

A symmetric multicore consists of structurally identical processing cores. Thus, such a multicore with n BCE area, can be built with n cores (each with unit area), or n/r cores where each core contains r BCE area. The sequential performance of a core built with an area equivalent of r BCE is given by an arbitrary function perf(r), although perf(r) is strictly less than r [46]. Without considering the SAF, the performance of a symmetric multicore is driven by: the sequential performance of a single core (i.e., perf(r)), and the parallel performance of n/r cores (i.e., perf(r).n/r). This speedup is then given by the following equation:

$$Symmetric_{speedup} = \frac{1}{\frac{1-f}{perf(r)} + \frac{f \cdot r}{perf(r) \cdot n}}$$

Now the power constraint restricts the aggregate active area to  $\alpha.n$  BCE area. Therefore, regardless of the amount of existing parallelism in the parallel phase of the code, one can employ  $\alpha.n/r$  cores at most. The choice of r is now restricted in the sense that it cannot exceed  $\alpha.n$ . The speedup of the symmetric multicore considering its SAF is then given by:

$$Symmetric_{SAFspeedup} = \frac{1}{\frac{1-f}{perf(r)} + \frac{f \cdot r}{perf(r) \cdot n \cdot \alpha}}$$

### 2.4.4 Dynamic Multicore

A dynamic multicore is built with structurally similar processing core components, much in the same spirit of a symmetric multicore. However, unlike a true symmetric multicore, a dynamic multicore can logically combine individual processing cores to boost the sequential performance. Thus, in the limit, during the sequential phase of an execution, it can fuse all the processing cores to boost the performance. Alternately during the parallel phase, it can employ all the cores in isolation to exploit maximum parallelism. Without considering the SAF, the speedup in this system will be:

$$Dynamic_{Speedup} = \frac{1}{\frac{1-f}{perf(n)} + \frac{f}{n}}$$

Similar to the case of symmetric multicore, incorporating SAF in this performance estimation boils down to realizing that only  $\alpha$ .*n* BCE area equivalent can be in active state simultaneously. Therefore, both the sequential and parallel speedup boost in a dynamic multicore will be limited by the SAF factor  $\alpha$ .

$$Dynamic_{SAF speedup} = \frac{1}{\frac{1-f}{perf(\boldsymbol{\alpha} \cdot n)} + \frac{f}{\boldsymbol{\alpha} \cdot n}}$$

The basic assumption used here, which is derived from the original analysis by Hill and Marty [46], is that the performance of a dynamic multicore can continue to increase with additional processor cores, regardless of the implementation complexity for supporting such dynamic reconfiguration.

### 2.4.5 Asymmetric Multicore

The program analyzed here consists of two distinct phases: sequential and parallel. Therefore, although an asymmetric multicore allows many forms of structural asymmetry to co-exist, for the purpose of this analysis, the most optimal asymmetric configuration consists of one large core, comprising multiple BCE areas, for executing the sequential phase of the program, and the rest with unit BCE cores for executing the parallel phase. Thus, during the sequential phase, the large

core built with r BCE area is employed, while the parallel phase employs n - r single BCE cores and the large core. Performance estimation without considering SAF will be:

$$Asymmetric_{speedup} = \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{perf(r)+n-r}}$$

Note that the above model presented by Hill and Marty [46] implicitly ignores any synchronization and wait time during execution of the parallel phase. Subsequent extension of this model in this analysis also conforms to this basic assumption.

While incorporating SAF in both symmetric and dynamic multicore performance estimation was simple, and qualitatively maintained the essence of the original model, asymmetric multicore is substantially different. The key contributing factor behind this fundamental difference is the ability to more effectively exploit the core area through the asymmetric design paradigm, and the ability to meet the power constraint by utilizing different fraction of the chip area. As the limitation of SAF restricts active computation to a fraction of the entire available area, in the limit, an asymmetric design can employ custom area component (e.g., a large core for sequential phase) to boost one phase without compromising the other phase. The computation then simply moves around on its designated best fit, without requiring the dynamic re-configuration as in dynamic multicore.

An expression is now developed for the general case of asymmetric multicore scenario. The sequential phase of the program is assigned to the large core with r BCE area. However, during the execution of the parallel phase, one may choose to exploit different sections of the chip, depending on the respective speedups offered. The collective area of those sections may exceed the power constraint when active simultaneously, but meeting the power constraint by selectively employing each fraction allows to exploit an over-provisioned area (see Section 2.1.3).

Different scenarios arise based on the sections of the area employed during the parallel phase

of the execution. First, if the area available after provisioning the large core, which is built with r single BCE cores, is as at least much as allowed by power constraint, then this section of the area can be used exclusively during the parallel phase. The performance in this case would be equivalent to the dynamic multicore, as both the execution phases are assigned to the best possible core area. Collectively, a total of  $r + \alpha \cdot n$  area will be used, but the dynamic distribution of activity allows to satisfy the power constraint by restricting simultaneous activity to only  $\alpha \cdot n$ .

Otherwise, one can either use the large core during the parallel phase, or only use the single BCE cores. The speedup is estimated based on the maximum possible speedup attained among these two choices. Thus, the performance estimation of an asymmetric multicore will be  $^{2}$ :

$$Asymmetric_{SAFspeedup} = \begin{cases} \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{\alpha \cdot n}} & : \quad r + \alpha \cdot n \le n \\ \frac{1}{\frac{1-f}{perf(r)} + \min(\frac{f}{perf(r) + n \cdot \alpha - r}, \frac{f}{n-r})} & : \quad r + \alpha \cdot n > n \end{cases}$$

### 2.4.6 Results

This section now presents quantitative results based on the analytic models developed in the previous section. For each multicore configuration of a given size (i.e., n), there are three different parameters to vary:

- *f*: degree of parallelism,

- *r*: the number of single BCE area occupied by each core in symmetric multicore, and the size of the large core in asymmetric multicore,

- $\alpha$ : the Simultaneously Active Fraction or SAF.

For a given f and  $\alpha$ , the performance of a particular type of multicore will vary depending on r, but will likely become optimal at a particular r (occasionally multiple values of r may also yield

<sup>&</sup>lt;sup>2</sup>Note that the minimum positive value in the denominator gives the maximum overall value.

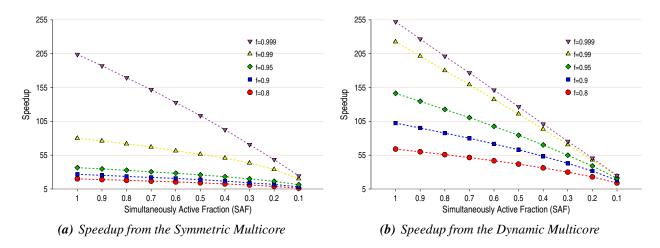

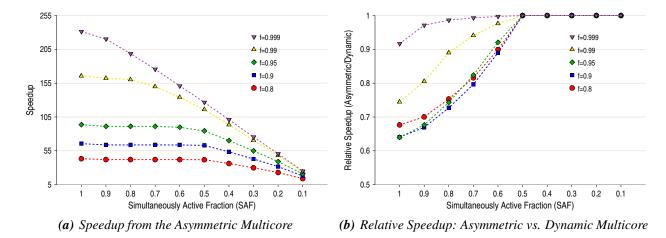

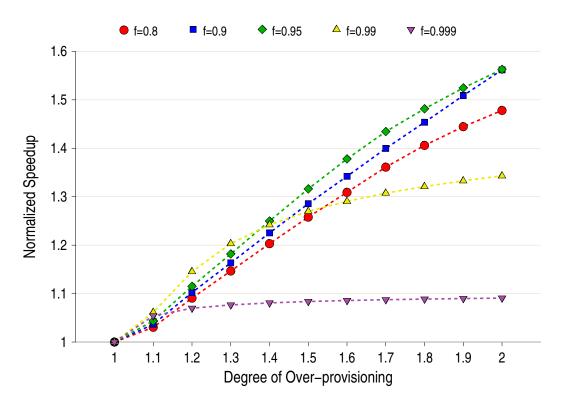

Figure 2.2: Speedup from the Symmetric and the Dynamic Multicore