# TECHNIQUES AND DATA STRUCTURES FOR PARALLEL RESOURCE MANAGEMENT

Jit Biswas

Department of Computer Sciences The University of Texas at Austin Austin, Texas 78712-1188

TR-87-42

November 1987

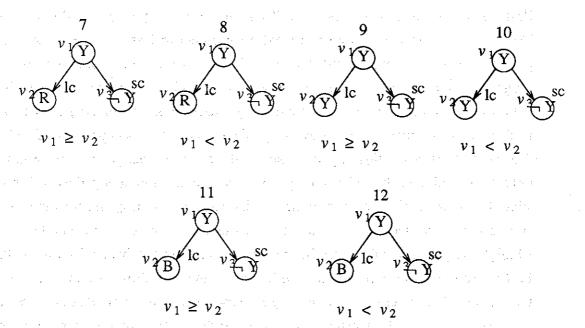

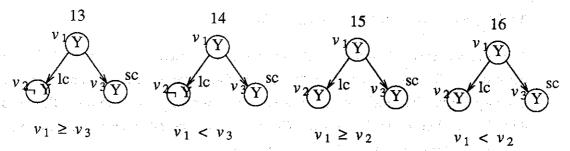

# TECHNIQUES AND DATA STRUCTURES

# **FOR**

# PARALLEL RESOURCE MANAGEMENT

#### APPROVED BY

SUPERVISORY COMMITTEE

Alogan mok Jeff Brunfill MA SMA Copyright

by

Jit Biswas

1987

# TECHNIQUES AND DATA STRUCTURES

FOR

## PARALLEL RESOURCE MANAGEMENT

by

Jit Biswas, B.E., M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 1987

#### Acknowledgements

I would like to gratefully acknowledge the constant encouragement, support and great leeway given to me by my supervisor Dr J. C. Browne. I am also indebted to other members of my committee for their helpful suggestions from time to time. Dr Al Mok and Dr Clement Leung have been sharp critics and I shall always be grateful to them for goading me into seeking nothing but the best in terms of the quality of my work. In addition I would especially like to thank Dr Vipin Kumar who has been a believer and a supporter. He has also been very generous with his time and financial support. Dr Carla Ellis (of Duke University) has been very helpful in pointing me toward relevant literature on concurrent data structures, especially in the initial stages of my work. I really appreciate her guidance.

To Pradeep Jain and Raghu Ramakrishnan I am especially indebted for countless discussion sessions over innumerable cups of coffee. Pradeep's painstaking reading of my dissertation has greatly improved its readability. I also wish to express my gratitude to my colleagues of the Parallel Programming Group, especially Paul Suhler, Steve Sobek, Ashok Adiga, S. J. Kim, Mary McShea, Steve Eubank, Bob O'Dell, Nicolas Graner, T. T. Ramgopal and many others who have suffered through my Wednesday afternoon presentations. I would also like to thank Sanjay Deshpande and V. N. Rao for their suggestions. Finally, I wish to thank my roommate Avi Saha for his support and encouragement during my travails as a graduate student.

This thesis is dedicated to my parents.

## TECHNIQUES AND DATA STRUCTURES

#### **FOR**

d ...

#### PARALLEL RESOURCE MANAGEMENT

| Publication No. |             | - 1      |

|-----------------|-------------|----------|

|                 | <del></del> | <u> </u> |

Jit Biswas, Ph.D.

The University of Texas at Austin, 1987

Supervising Professor: James C. Browne

The problem of managing the resources of a highly parallel system is viewed as the problem of simultaneously updating data structures that hold system state. We approach this problem in an abstract data type framework. Simultaneous update may be attained in two ways: by decomposing abstract states into components and allowing operations to concurrently transform the state of these components in a controlled manner, and by weakening the specification of abstract data types in ways that are acceptable to entities using instances of abstract data types.

This thesis contributes to parallel resource management in both ways. First, we have considered management of system state for computation structures consisting of arrays of computations that differ only in indexing parameters. We have proposed simple decompositions of the externally visible state into simultaneously updatable

components. Second, we have considered the management of system state for weakened priority queues. The two priority structures proposed in this thesis, a concurrent heap and a software banyan, have been found to be efficient and effective.

We have, in addition, contributed in the area of language tools for computations that utilize predefined abstract data type implementations. A mechanism for abstract data type definition is presented. To promote simultaneity of update we have defined a significant extension of the linguistic construct of path expressions and used it as a basis for defining implementation of sequencing within abstract data types. The main advantage of using extended path expressions is that in addition to synchronization requirements, binding of activities to object decompositions may be specified, along with runtime consistency checking, while leaving the object implementation to the underlying system. We have developed algorithms for the automatic synthesis of sequencing and synchronization code.

A task level data flow language designed and implemented by us has provided a context and a testbed for ideas presented in this thesis.

where  $k_{1}$  is the first parameter  $k_{2}$  , which is the  $k_{2}$  -  $k_{3}$  . We still the  $k_{3}$

# **Table of Contents**

| Abstract                                                            | v  |

|---------------------------------------------------------------------|----|

| Chapter 1 - Introduction                                            | 1  |

| 1. The Problem                                                      | 1  |

| 2. The Solution Approach                                            | 1  |

| 3. Results and Contributions                                        | 1  |

| Chapter 2 - Background                                              | 3  |

| 1. Highly Parallel Architectures                                    | 3  |

| 2. Guidelines for Highly Parallel Resource Management               | 3  |

| 3. Control and Data Abstractions                                    | 5  |

| Chapter 3 - Terminology and a Model for Simultaneous Update         | 11 |

| 1. Introduction                                                     | 11 |

| 2. An Analogy - The Joint Account                                   | 12 |

| 3. System Model                                                     | 13 |

| 4. Examples                                                         | 26 |

| 5. Performance tradeoffs in partitioning, binding and restructuring | 33 |

| 6. The Doall Node of TDFL                                           | 36 |

| 7. Conclusions                                                      | 38 |

| Chapter 4 - Language Tools to Support Simultaneous Update           | 40 |

| 1. Introduction                                                     | 40 |

| 2. Work Container Objects                                           | 41 |

| 3. Extended Path Expressions                                        | 46 |

| 4. Work Managers and Their Use                                      | 50 |

| 5. Implementation of Work Managers and Extended Path Expressions    |    |

|                                                                     | 60 |

| 6. Conclusions                                             | 72  |

|------------------------------------------------------------|-----|

| Chapter 5 - Weak Priority Queues                           | 74  |

| 1. Weakened Specifications                                 | 74  |

| 2. The Heap as a Strict Priority Structure                 | 76  |

| 3. Development of the Concurrent Heap Algorithm            | 81  |

| 4. The Banyan as a Simultaneously Updatable Data Structure | 99  |

| 5. Performance Estimates                                   | 112 |

| 6. Related Work and Potential Applications                 | 115 |

| 7. Conclusions                                             | 118 |

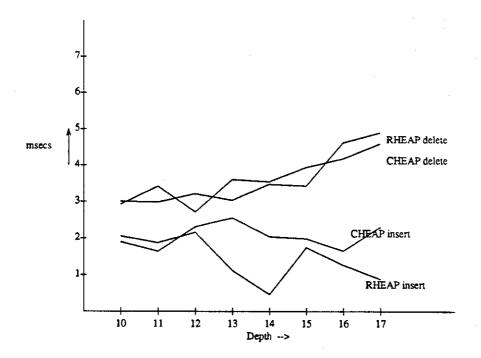

| Chapter 6 - Performance Measurements                       | 119 |

| 1. Introduction                                            | 119 |

| 2. Implementation of the Concurrent Heap                   | 119 |

| 3. A hybrid simulator for the CHEAP and SBAN               | 126 |

| 4. Specialized Hardware for Priority Structures            | 133 |

| Chapter 7 - Contributions and future directions            | 146 |

| 1. Contributions                                           | 146 |

| 2. Significance                                            | 147 |

| 3. Future Work and Possible Directions for Extensions      | 147 |

| References                                                 | 149 |

| Glossary                                                   | 157 |

| Appendices                                                 | 158 |

# Chapter 1 - Introduction

#### 1. The problem

This research addresses the problem of resource management, or the management of system state, for highly parallel large scale multiprocessor systems. The allocation of a resource to a computation, or alternatively the assignment of a computation to a resource, results in a change of state of the system. In order to perform correctly, a data structure that holds system state must obey consistency relations just as any other data structure. In executing the functionality of the state management one must avoid serializing bottlenecks resulting from update of system data structures, since this results in performance bottlenecks.

#### 2. The solution approach

The obvious approach is to apply parallelism to resource management or the management of system state. The requirement is to decompose the data structures defining the state of the system so that the partitions of the decomposition can support parallel or simultaneous update, and to establish algorithms which execute simultaneous updates with maintenance of the consistency specifications for the system state data structures. We approach this problem in an abstract data type framework. We define semantics and consistency properties for the data structures which maintain system state such that these data structures can be partitioned and parallel algorithms defined on them. A fundamental guideline which is the basis for our work is the separation of the external specifications from the implementation specifications for objects (abstract data type instances) implementing system state management.

#### 3. Results and contributions.

We have targeted two particular problem domains of resource management. The first is management of system state for computation structures consisting of arrays of computations that differ only in indexing parameters. In this case we have proposed simple decompositions of the externally visible state into simultaneously

updatable components. The second is the management of priority structures. Parallel abstract data types, including data structures and parallel algorithms implementing priority queues supporting simultaneous update, are defined and characterized. We have also contributed in the area of language tools for computations that utilize predefined abstract data type implementations. An illustrative framework for an abstract data type definition facility is defined. We identify a class of computations which support implementation of the models of computation directly from current programming languages. To promote simultaneity of update we have defined a significant extension of the linguistic construct of path expressions and used it as a basis for defining implementation of sequencing within abstract data types. The main advantage of using extended path expressions is that in addition to synchronization requirements, binding of activities to object decompositions may be specified, along with runtime consistency checking, while leaving the object implementation to the underlying system. We have developed algorithms for the automatic synthesis of sequencing and synchronization code. The two priority structures proposed in this thesis, a concurrent heap and a software banyan, have been found to be efficient and effective. Variants of both algorithms can be easily implemented in specialized hardware, gaining additional performance.

# Chapter 2 - Background

#### 1. Highly Parallel Architectures

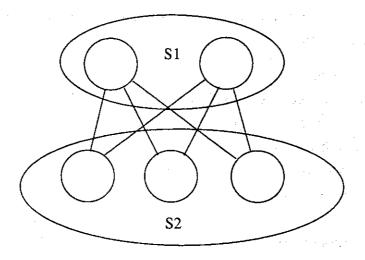

A highly parallel architecture is a MIMD [Flynn '66] multiprocessor architecture that has no inherent limitation upon the number of processors that it can have. These architectures have been traditionally divided into three broad classes. The first class consists of *shared memory multiprocessors* with high speed interconnection networks. Examples are the Butterfly [Butterfly '85], RP3 [Pfister '85], NYU Ultracomputer [Gottlieb '83b] and Cedar [Gajski '83]. The second class is that of distributed memory architectures, where no memory is shared by processors, and information must be sent from one processor to another across hardware channels. The hypercube machine first built at Caltech [Seitz '85] and commercialized by Intel [Intel '87] and other manufacturers are examples of this class. Finally, there are hybrid † architectures, that support memory sharing within clusters of processors and messaging passing, or *messaging* between clusters. Examples are C.mmp [Wulf '72], Cm\* [Swan '77] and FLEX [Matelan '85].

The data structures and algorithms described in this thesis apply to resource management for highly parallel architectures in all three above categories, though our implementation and some of our illustrative examples deal with machines in the first category.

# 2. Guidelines for highly parallel resource management

In our view, the following guidelines are essential for doing resource management for highly parallel architectures.

i) Multiple serialization points. Traditional views of resource management have been centralized. This is because, a resource has always been modelled as a centralized entity with global critical sections. For example, a monitor

<sup>†</sup> Sometimes researchers prefer to classify some of the shared memory multiprocessors as being hybrid, because there is a dichotomy in the amount of time taken between local and nonlocal memory accesses.

[Hoare '74] guarantees that no two processes shall be inside it at the same time, thereby bringing about a global serialization point. Arvind [Arvind '77, '83] breaks away from this restriction with the use of dataflow resource managers, but these managers are defined within the framework of dynamic, instruction level dataflow. We would prefer to have a solution that applies in more general situations.

- ii) Multiple binding times. Activities should be bound to the object of their computation only when such a binding is required. This can be at load time, if the object is frequently required, or at runtime, if the object is not frequently required or shared by several activities.

- iii) Patterns. Frequently occurring patterns of object partitioning and mapping should be optimized and provided in libraries for programmers to use.

- iv) Database concurrency for multiprocessors. The field of concurrency has been very well researched in distributed databases. Well known techniques exist for achieving simultaneous update for databases in a manner that preserves consistency and integrity constraints [Kung '80a]. These ideas may be adapted to achieve concurrency in data structures for resource management on highly parallel architectures.

In order to achieve the above guidelines we partition data structures that hold the state of computations. Partitioning obviously brings about multiple serialization points, since different activities may access different partitions at the same time in an overlapped manner. Binding activities to partitions of an object can be done at different times, to exploit performance advantages. To incorporate patterns, we develop control abstractions around path expressions, which are synchronization specification constructs. Often, it is beneficial to relegate non-urgent tasks of restoration of data structures, to restructuring activities, so that more immediate activities can proceed faster. This is a technique used in the preservation of database indexes. We demonstrate how this technique can be applied to resource management for highly parallel architectures.

Our work is thus centered around control and data abstractions. To put this work in

perspective we now discuss the related literature.

#### 3. Control and data abstractions

## 3.1. Specification of control dependencies

Programs written in sequential programming languages such as Fortran must be carefully analysed to extract dependency information [Kuck '81], to permit the generation of code that exploits features of the target machine. This paradigm of programming and code optimization is still the one with largest following among users of high performance computers.

An alternate paradigm, and one that makes the job of the compiler writer much simpler is to impose certain restrictions upon the constructs that a programmer is allowed to use, and thereby restrict the class of dependence graphs that will be generated at runtime. If these graphs have certain attractive properties, such as having only disciplined access to shared data structures, or having restrictions upon the kinds of cycles permitted, then it is straightforward to perform efficient resource management for them. Data flow languages, for example, VAL [Ackerman '79] Id [Arvind '78], and SISAL [McGraw '85], are so structured that once a program is written in these languages, the parallelism naturally falls out of the program. Another example of this paradigm is the SPMD (single program multiple data) programming style introduced in the programming of the RP3 multiprocessor [Darema '85]. In this approach, each program is written as a single Fortran program with special system calls for parallel constructs. Some of our work has been influenced by this approach and some of the tools that we propose are directly usable within this framework.

In addition, our work has focussed or an alternate paradigm, in that although we provide constructs to the programmer with which to compose programs, the schedulable units of computation are at the task level. The programmer programs in large grain units called tasks, (approximately at the level of subroutines in Fortran, or procedures in Pascal), that are the natural units of computation. We wish to exploit parallelism at the level of tens or hundreds of instructions, rather than that

of a single instruction, as has been the case with traditional data flow. Many regular structured problems, can exploit parallelism at this level. For example, graph algorithms such as the maximum concurrent flow problem [Biswas '86] and problems from computational physics, such as the computation of trajectories of particle in motion in a plasma, [Biswas '87a], have identifiable parallelism at the level of blocks of instructions.

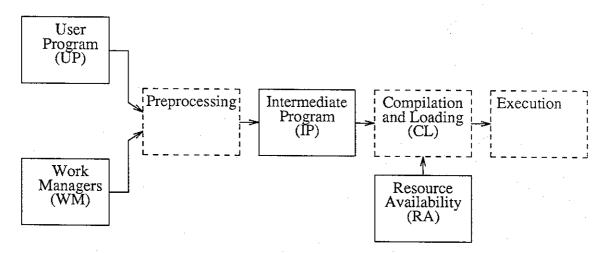

We have designed and implemented a simple graphical task level language called TDFL (Task-Level Data Flow Language) [Suhler '87]. The language provides a set of constructs that programmers are inclined to use frequently. Separation of concerns between the program's specification and its implementation is maintained, since the specification is a graph. Thus irrespective of the sequence in which the nodes of the graph fire, or compute, the outcome of a computation is always the same. Cycles in the program graphs must belong to a restricted class of allowable cycles. We have parallelized the scheduling of ready nodes, and other constructs in the language.

#### 3.2. Specification of synchronization

The genealogy of path expressions start with regular path expressions [Campbell '74], which have *closed* semantics, in the sense that operations in an expression are assumed to execute in mutually exclusive mode, unless otherwise specified. These were succeeded by open path expressions, OPEs, [Campbell '77], that had unconstrained semantics. Thus an unrestricted number of parallel invocations of an operation on an object may be active simultaneously if no explicit restriction is mentioned in the associated OPE. It has been demonstrated [Oldehoeft '84] how to synthesize data flow resource managers of the same ilk as Arvind's, from OPEs, and [Headington '85] to incorporate predicates associated with these path expressions making them open predicate path expressions (OPPEs). The authors also demonstrate how to convert an OPPE into a network of controllers with data flow nodes implemented in a purely message based environment.

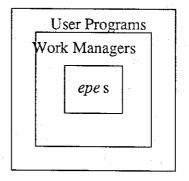

While writing and implementing programs for execution on multiprocessors, we see two levels at which there is the necessity for specifications. The first is at the

level of user programming, i.e. when only what needs to be done is specified. The second is the specification of synchronization between user level programs; here we must specify the allowable sub-sequences of interleavings. For example the writing of a TDFL program is programming at the user level whereas programming the TDFL scheduler itself is at the second level. If we consider the writing of controllers or schedulers as a programming task (which it is), we immediately feel the necessity of automating this task. Synchronization specifications can be provided, to automate the task of code generation for controllers required for the language. Thus if the language has a provision for setting up mutual exclusion dependencies, then it should be possible to specify an appropriate mutual exclusion constraint at a very high level, by means of an appropriate language, and have code for the preservation of the mutual exclusion dependency, generated automatically. Automation of code generation can also be made to apply to other areas such as binding and consistency constraints. In this thesis we examine an extension to path expressions as a means of specifying synchronization, binding and consistency constraints to be satisfied by implementations.

#### 3.3. Data abstraction

The guidelines of section 2 can be met by partitioning implementations of abstract data types (adt s) [Guttag '80]. There are two types of issues here, namely those related to formal properties of adt s and those related to adt implementations. Abstract data types are defined by giving them semantics and abstract properties which the implementation must then satisfy and preserve.

Data structures have always been thought of in sequential settings whereas data-bases have always been thought of in concurrent settings. The key difference is in the application. Most of the earlier work with abstract data types was centered around the abstract semantics of types and their operations. The application of objects such as stacks and queues were in strictly sequential domains. In contrast, databases are shared by definition, and different applications require different kinds of consistency or serializability requirements from their databases.

New application areas such as databases for computer aided design [Bancilhon

'85], atomic data types [Weihl '84], and distributed operating systems [Rashid '86] have introduced a class of objects that we call *simultaneously updatable objects*, with formal properties that are quite different from those of conventional *adt* s. Computations using these objects have consistency requirements that are based on the semantics of *adt* s and *adt* computations rather than syntactic serializability requirements that are to be found in traditional database concurrency control [Papa '86].

Various issues have emerged as being important in characterizing this new class of objects. These are atomicity properties [Weihl '84], object implementation states and correctness of implementations [Shasha '87], new notions on interleavings in computations concerning concurrent objects [Herlihy '87], semantics of conflict and commutativity in shared abstract data types [Schwarz '83] and implementation of shared abstract data types [Bottos '85].

Database concurrency control has furnished a rich body of results, which can be used to characterize formal properties and develop efficient implementations of simultaneously updatable objects. Among the most significant contributions from this area (in relation to our work), are contributions in locking protocols, and those in the concurrent manipulation of data structures used to maintain large database indexes. We briefly discuss the relevant results. The two phase locking protocol [Easwaran '76] is a simple protocol for locking data items in such a way that serializability is preserved. Tree locking protocols [Silberschatz '80], use a simple strategy of progressing down a tree-structured collection of data items, preserving serializability of the resulting computation without locking the entire tree. Concurrency can be enhanced [Korth '83] by granularizing a database in such a way that locks at higher levels of granularity may be released once those at lower levels are obtained.

The results mentioned above have found application in designing concurrent data structures for database indexes. Two techniques predominate, the link based technique and the lock coupling technique. The link based technique [Kung '80b] relies on the property that a very small atomic state change is all that is necessary to preserve the structure and semantics of a binary search tree, for an unrestricted set

of input operations. The basic idea in lock based techniques [Bayer '77] is a direct application of the tree protocol, called lock coupling, i.e. the paradigm that a parent lock (i.e. the lock at a parent node), is released only when a child lock is obtained. These algorithms and their derivatives have been proposed for binary search trees [Manber '83], AVL trees [Ellis '80b] and B Trees [Lanin '86].

Most of the above work concerns software structures. The balanced cube object [Dally '86] is an attempt at reflecting the physical structure of a hardware architecture in a search structure. This object has been proposed as a concurrent object that scales up and down with the size of the hypercube upon which it is currently mapped. Concurrent smalltalk has been used by Dally as a programming language for his object implementation. In our work we demonstrate how general purpose programming languages can be used in similar situations.

The issue of efficient abstract data types has been analysed from the perspective of distributed systems in the work of Bastani et al [Bastani '87]. In addition to the notions of periodic and concurrent maintenance, the authors also use invariants to specify properties of implementations of an abstract data type. If the strongest (weakest) invariant is satisfied then the performance is best (worst). In our approach we also propose weakening of specifications to introduce performance gains in implementations of abstract data types.

Simultaneous update of data structures that maintain system state information is the focus of our work. We have considered two ways of obtaining simultaneous update, decomposition of externally visible or abstract states of an object, and weakening specifications of an object at external and internal levels. In chapter 3 we present our terminology and address the decomposition aspect of simultaneous update. We introduce an event based model consisting of objects and activities, where abstract specifications are provided for each object. Internal or object implementation states are characterized in terms of decomposition functions upon abstract states. Based upon these definitions we develop the notion of correct external histories and internal histories. In chapter 4 we develop tools for obtaining simultaneous update. We propose an abstract data type definition facility and illustrate its use with examples. The augmented synchronization specification language

of extended path expressions is presented in this chapter and code synthesis algorithms provided.

The issue of weakened specifications is addressed in the remaining chapters of this thesis. We identify a specific object class namely priority structures, and characterise under what conditions such structures may be weakened for performance gains. We outline serial and concurrent algorithms for managing priority structures, demonstrating such weakening at external and internal levels. The proposed structures are analysed in chapter 6.

The granularization approach taken in this thesis was inspired by related research in concurrent management of index structures for databases [Lanin '86, Kung '80b, Ellis '85, '83, '80a, '80b]. We know of no existing parallel algorithms for priority structures for general purpose multiprocessors. Specialized hardware has been proposed for priority applications and dictionary machines [Leiserson '79]. This topic is discussed further in section 4 of chapter 6 where we develop systolic structures for priority applications and contrast these with those existing in the literature.

# Chapter 3 - Terminology and a model for simultaneous update

#### 1. Introduction

Informally two activities are said to *simultaneously update* an object if their operations upon that object are overlapped in time. For example two activities simultaneously update a file object if their updates on different records overlap in time. Thus simultaneous update is achievable by partitioning an object into smaller granularity units (records, for example) and overlapping updates to these units in conformance with consistency specifications for updates of records.

In this chapter we define simultaneous update using terminology from a model based upon objects and activities. We are mainly concerned with the definition of a model of computation which separates external specifications from internal specifications so that simultaneous update can be tolerated in the external specifications. We consider two ways of achieving simultaneity of update. The first is partitioning or decomposition of the externally visible state of an object so that the components may be concurrently updated. The second is the introduction of weakened specifications at both external and internal levels. In this chapter and the next we look at the former. In chapter 5 we address the issue of weakened specifications.

First we present in section 2, an analogy using a bank account example to provide an intuitive feel for what we mean by partitioning. In the succeeding section we characterize simultaneous update of objects in terms of a system model for objects and their implementations. We define object specifications using a state machine model with partial functions and annotations using a standard event based model [Weihl '84]. Then we define object implementation states in a similar manner as that introduced by Shasha [Shasha '87] in the context of search structures. We show how an abstract state can be decomposed into a set of components at the implementation level such that these components are concurrently updatable. We generalize the composition of these constituent components back to form the abstract state that they implement. Internal histories are also characterized in sec-

tion 3 and it is shown how an external history may be obtained from an internal history. We compare our system model with the Karp and Miller model [Karp '69].

In section 4 we illustrate our model by the bank account example and two more examples and examine their performance in section 5. We examine the correctness of internal histories and address the role of a scheduler for an object in the process of witnessing and permitting overlaps. To provide a concrete illustration of our ideas we briefly discuss a construct of a task level data flow language and demonstrate how computations resulting from programs written in this language perform simultaneous update. Issues that are related to partitioning are time of update, to take advantage of performance tradeoffs on parallel architectures and restructuring, to perform asynchronous maintenance of object implementations. We characterize multiple binding times and restructuring using the terminology developed.

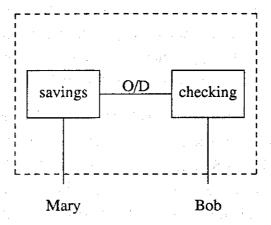

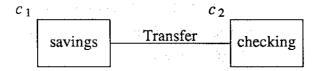

#### 2. An analogy - The joint account

Let us say that Mary and Bob hold a joint account with savings and checking components (see Fig 2.1). We assume that both accounts are protected by an automatic overdraft scheme whereby money is transferred automatically from one to the other in case of inadequate funds in the latter. Let us assume that the bank has been informed that Bob's transactions will always be associated with the checking account and Mary's with the savings account. Initially the checking account contains \$0\$ and the savings account contains \$0\$. The following history is possible: (Events occur chronologically with the i<sup>th</sup> event occurring at time  $t_i$ .)

- $t_1$  Bob requests withdrawal of \$ 50 from the joint account.

- $t_2$  Mary requests deposit of \$ 50 into the joint account.

- $t_3$  A bank employee transfers \$ 50 from savings to checking.

- $t_4$  Bob gets \$ 50.

- t<sub>5</sub> Mary gets acknowledgement.

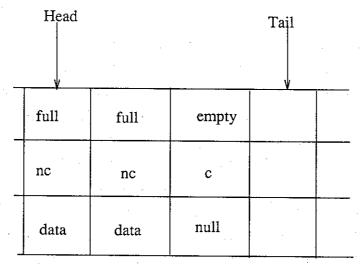

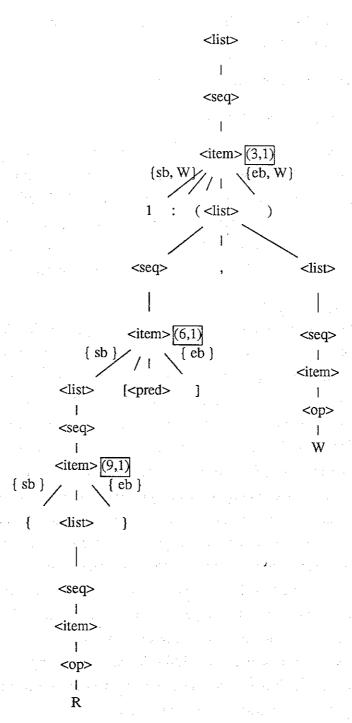

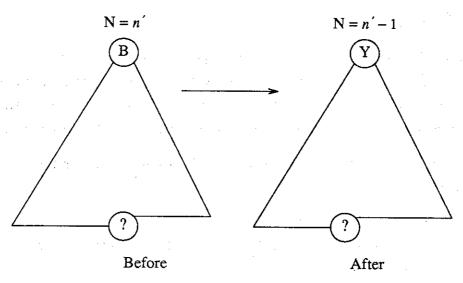

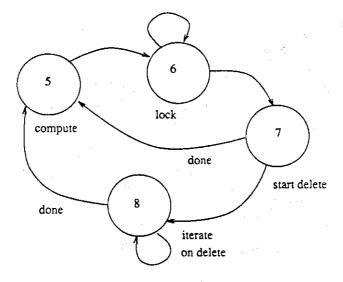

Fig 2.1: The joint account object

Notice that at the time Bob requested withdrawal there was no money in either component of the joint account. However at the time the bank employee performed the transfer, Mary had already requested a deposit and it had been internally recorded. Admittedly the manner in which partitioning is done in the above example is somewhat contrived. However, this example illustrates three points. Firstly the joint account is an object which is simultaneously updated at an abstract level, although internally each update is channelized to a different partition of the object. Within a partition updates are not simultaneous. Secondly the binding of account holders to account components is statically performed, i.e. at creation time of the joint account object. We may have a dynamic or runtime binding of account holders by randomly picking an account component for every request. This illustrates time of binding. Finally we have a maintenance activity namely the "transfer" operation carried out by the bank employee. Such maintenance activities carry out restructuring of the internal state of a bank account in order to support the correct behaviour of the implementation of an account with respect to its specification. Informally this means a client must be able to withdraw money if sufficient funds are in either component of her (his) account.

#### 3. System Model

Our system consists of activities and objects that interact through events. Objects are instances of abstract data types that have internal state and have external

specifications that allow for simultaneous update. (The type definitions themselves are in objects called *managers* that support the *create* operation. We shall see an example of this in the application domain of work management in the next chapter.) A computation is a history of events involving activities and objects.

Formally, a system consists of a quadruple  $\langle OB, AC, \Sigma, C \rangle$ , where  $OB = \{x, y, \dots\}$  is a finite set of objects,  $AC = \{A, B, \dots\}$  is a finite set of activities,  $\Sigma = RES \cup INV \cup PARMS$  (described below) is the set of symbols that cause state transitions, and  $C = \{c_1, c_2, \dots\}$  is a finite set of components that are analogous to memory locations in the sense that they hold the state of object implementations. For each component  $c_i \in C$  there is a domain  $D_i$  or set of possible values that the component can have.

### 3.1 Events, operations and histories

Activities are analogous to processes in that they are threads of control of finite duration that invoke operations on objects. We do not specify activities any further. The behaviour of our system is captured by a sequence of *events* that occur between activities and objects, called a *history*. An event may be an invocation or a termination event. An *invocation event* is a four tuple < invok, args, act, obj > and a *termination event* is a four tuple < resp, results, act, obj > where  $act \in AC$ ,  $obj \in OB$ ,  $invok \in INV$  (the set of invocation symbols),  $resp \in RES$  (the set of termination symbols), and args,  $results \in PARMS$  (the set of parameter values that may be elementary values such as booleans and integers or structured values such as pairs of elementary values). If x is an object and A an activity of a particular event e, then e is said to involve A and x.

A complete history is a sequence of events of a system such that for every invocation event there is exactly one termination event that is matching, i.e. agreeing in the activity and object fields, the termination event appears after the invocation event, there are no other events involving the same activity between these two events<sup>†</sup>, and there are no unmatched events.

<sup>†</sup> The requirement that there is no more than one outstanding invocation event at a time from a single activity arises from our application domain.

# 3.2 The serial specification of an object

The serial specification of an object is a state machine that describes the behaviour of that object in the absence of concurrency. Formally, for each object  $x \in OB$  is associated a quadruple  $\langle S_x, I_x, O_x, T_x \rangle$ , called the *serial specification* of x, where  $S_x$  is a set of states,  $I_x$  is a designated initial state,  $O_x$  is a set of operations and  $T_x$  is a transition function.  $T_x: S_x \times O_x \to_p S_x$  is a partial function describing how the state changes with each permissible operation. The partial nature of  $T_x$  is specified with the help of preconditions discussed below. We shall now characterize the set of operations  $O_x$ .

An operation is a pair of events << invok, args, A, x>, < resp, results, A, x>>, where the first event is an invocation event and the second event is a matching termination event. Preconditions in the specification of the transition function  $T_x$  are predicates associating the state, the arguments and the results in the form of a boolean valued function which must be satisfied for the transition to occur.

## Example 3.1. Serial specification of the two element set object

Let us assume that we have an object  $x \in OB$  that behaves as a set of values with the operations "put" and "get", where the universe consists of two elements "a" and "b". The serial specification of this object is as follows:

```

S_x = \{ s_1, s_2, s_3, s_4 \}

where s_1 = \{ \}, s_2 = \{ a \}, s_3 = \{ b \}, s_4 = \{ a, b \}

I_x = s_1

O_x = \{ o_1, o_2, o_3, o_4, o_5 \}

where o_1 = \langle \langle \text{get}, \text{NULL}, A, x \rangle, \langle \text{ok}, a, A, x \rangle \rangle

o_2 = \langle \langle \text{get}, \text{NULL}, A, x \rangle, \langle \text{ok}, b, A, x \rangle \rangle

o_3 = \langle \langle \text{get}, \text{NULL}, A, x \rangle, \langle \text{ok}, \text{NULL}, A, x \rangle \rangle

o_4 = \langle \langle \text{put}, a, A, x \rangle, \langle \text{ok}, \text{NULL}, A, x \rangle \rangle

and A \in AC

```

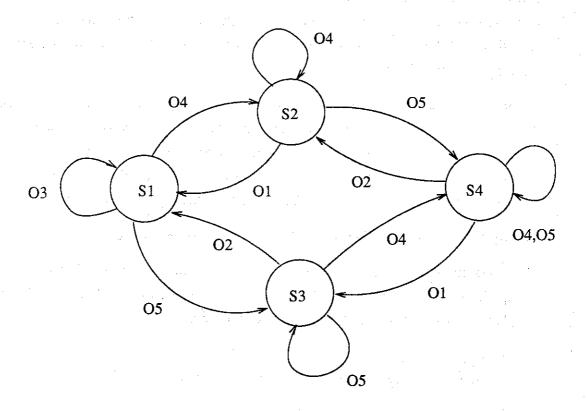

The partial function  $T_x$  is depicted in Fig 3.1. Not every operation is defined at every state in this diagram. Thus it represents a partial function. For the two element set object it is possible to enumerate the states and the operations exhaustively (except for the activity field). For more complex objects such exhaustive enumeration is infeasible and we shall introduce variable names and predicates on these variable names to denote entire sets of states and classes of operations.

Fig 3.1:  $T_x$  for the two element set object x

#### 3.3 Sequences of operations

The serial specification of an object may be extended to apply to sequences of operations in the usual way as follows: If Seq denotes a sequence of operations with Last (Seq) denoting the last (most recent) operation in the sequence and Past (Seq) denoting the previous sequence of operations before the last operation then for a given  $s \in S_x$ :  $T_x$  (s, Seq) =  $T_x$  ( $T_x$  (s, Past(Seq)), Last(Seq)) if  $T_x$  (x,

Past (Seq)) is defined, and is undefined otherwise.

Given a history H, the *projection* of H onto activity A (denoted  $H \mid A$ ) is the subsequence of H restricted to only and all events involving activity A. Similarly the projection of H onto object x (denoted  $H \mid x$ ) is the sub-sequence of H restricted to only and all events involving object x. If H is a history we use  $<_H$  to denote the (total) ordering on its events.

Two operations  $\langle inv_1, res_1 \rangle$  and  $\langle inv_2, res_2 \rangle$  on an object x are said to overlap at x in history H, if either  $inv_1 <_H inv_2 <_H res_1$  or  $inv_2 <_H inv_1 <_H res_2$ .

Simultaneous Update. Given activities A and B, and complete history H, we say A and B simultaneously update object x in history H, if there are two operations  $o_1 = \langle inv_1, res_1 \rangle$  and  $o_2 = \langle inv_2, res_2 \rangle$  that overlap in  $H \mid x$ , such that  $o_1$  involves activity A and  $o_2$  involves activity B.

#### 3.4 Correct histories

The consistency constraint of systems using objects is defined as a predicate upon the states of all the objects. In the most general case [Kung '83], such a constraint is a subset of the cartesian product of all the object state domains. We focus on a class of such consistency constraints, that can be put in conjunctive normal form [Korth '85], where each conjunct involves only a single object.

Thus, given objects  $\{x_1, x_2, \dots, x_n\}$  our consistency constraint is of the form  $CC = \{cc_1 \land cc_2 \land \cdots \land cc_n\}$  where  $cc_i$  involves only object  $x_i$ . Each conjunctive term is stated as an invariant on the corresponding object state, which must be maintained through each state transition in the serial specification of the object. A history involving several objects is equivalent to an arbitrary interleaving of the set of projections of the history upon each object. For example, let us suppose that Bob and Mary have two joint accounts, with Bob requesting transactions before Mary in some (correct) history from both accounts. A history, in which Bob precedes Mary in one and succeeds Mary in the other, is deemed to be an equivalent and correct history. The benefit of restricting ourselves to this class of computations is that we do not have to worry about preservation of consistency across objects.

Since we are not interested in preserving consistency across multiple objects, henceforth we shall restrict our attention to histories that involve a single object. Thus unless otherwise specified, whenever we mention a history H it will be understood that this history involves a single object x, and possibly multiple activities A, B and so on.

Given a history H a reordering transformation of H is a new history H', that is obtainable from H by permuting the events in H, in such a way that

- a) the ordering of events in each operation in H is preserved in H',

- b) there are no simultaneously updating operations in H and

- c) if a termination event  $e_1$  precedes an invocation event  $e_2$  in H, it does the same in H'.

Since H' does not contain any simultaneously updating operations the sequence of events in H' may be transformed into a sequence of operations, Seq, by considering successive invocation - response pairs.

A complete history H involving x is correct if there is a history H' such that H' is a reordering transformation of H, and the sequence of operations Seq composed of the sequence of successive pairs of events in H' is consistent with the serial specification of x. Thus a complete history H involving an object x is correct if a reordering can be found for H that satisfies the serial specification of x. The notion of reordering is also present in the work of Herlihy and Wing [Herlihy '87] who call such histories linearizable.

# 3.5 Object implementation states and internal histories

An object's implementation realizes its abstract specification [Shasha '87]. Thus if the object's transition function maps state s to state s' with a certain set of result values for a given operation, then the implementation maps some underlying representation of state s to some underlying representation of state s' with the same result values. The issue of partitioning primarily deals with an object's implementation.

It is beneficial (as we saw in the joint accounts example) to visualize objects as being coherent entities, while allowing simultaneous update in their implementations. Accordingly, we define an object implementation state to include the notion of *components* of an abstract state of an object. Components may be thought of as constituents of a *decomposition* of the externally visible state of an object that may be simultaneously updated, in a manner that will still preserve the specifications of the object. Components may also be thought of as granules of data that must be treated as unit entities, or sets of unit entities for synchronization purposes.

Formally, corresponding to each state  $s \in S_x$  for some object x is a quadruple < Dec, Cval,  $Dec^{-1}$ , Crel >, called the *object implementation state* of s.

- \*  $Dec: S_x \to 2^C$  is a function assigning to each state s in  $S_x$  a subset of components from C, that is called the *decomposition* of the state s, denoted Dec(s).

- \* Let  $Dec(s) = \{c_{i_1}, c_{i_2}, \dots c_{i_k}\}$  for some  $s \in S_x$ . Then the component value function  $Cval(c_{i_1}, c_{i_2}, \dots c_{i_k}) = (r_{i_1}, r_{i_2}, \dots r_{i_k})$  where  $r_{i_j} \in D_{i_j}$ :  $1 \le j \le k$ .  $r_m$  is also denoted as  $Cval(c_m)$  for  $m \in \{i_1, i_2, \dots, i_k\}$ . Thus Cval is an assignment of values to components.

- \* If  $(r_{i_1}, r_{i_2}, \dots r_{i_k})$  is the tuple of values of components  $(c_{i_1}, c_{i_2}, \dots c_{i_k})$  then  $Dec^{-1}$   $(r_{i_1}, r_{i_2}, \dots r_{i_k}) = s$ . Thus  $Dec^{-1}$  :  $X_{j=1}^k$   $D_{i_j} \to S_x$  is an inverse decomposition function that collapses the values of the components back into the abstract state that the components constitute.

- \* Crel is a set of functions  $\{f_1, f_2, \dots, f_{N(x)}\}$  where each function is a one to one association identifying a pair of components. Thus  $f_i: C \to C: 1 \le i \le N(x)$  are a set of binary component relationship functions. The component relationships capture some relation, logical or structural, between components in a state decomposition. N(x) is a non-negative integer that represents the number of component relationship functions for a given object x. Information provided by the component relation functions (for example Parent, Left\_child, Right\_child of a component representing a node of a tree structured object) is used by restructuring activities (see below) to perform

changes of object implementation states.

An *internal event* is similar to our earlier notion of an event which applied to *external event* or events at the abstract level. The differences between internal and external events are:

- i) An internal event may involve either a *restructuring activity* or a user activity whereas an external event may not involve restructuring activities.

- ii) The set of state transitions caused by pairs of internal events that constitute an internal operation includes those caused by restructuring activities. Thus in addition to the invocation and response symbols and parameter lists for external operations, internal events may also involve a new set of symbols and parameter values, namely those corresponding to restructuring operations.

- iii) An internal operation (a matching pair of internal events) may involve a set of components of an object implementation state, whereas an external event may involve only a single object. For a given activity and a given internal operation at a given component there is associated a set of components called the window of that invocation. The window is often expressed in terms of the component relationship functions in *Crel*. It need not be a function of all three parameters indicated above.

For the sake of clarity we shall not introduce additional notation to represent these new operations, activities and transition symbols. It will be clear from the context whether a history, event, operation, activity etc. is internal or external.

Each internal event is an internal invocation event or an internal termination event. Internal events are four tuples where the first three fields are similar to the corresponding fields in external events (with the provision for internal activities and operation symbols and parameter values). The fourth field in an internal event is a set of components that constitutes the *window* of the corresponding operation invocation.

#### 3.6 Correctness of internal histories

A definition for correct external histories was given in section 3.4. In this section

we consider internal histories and relate them to external histories in terms of correctness. We characterize internal histories, define when an internal history is correct, demonstrate how an internal history can be transformed into an equivalent external history, and thereby how to verify if a given internal history is a correct implementation of a given external history. Our development hinges around a notion of atomicity of window updates. Atomicity is the absence of simultaneous update or overlap. (This restriction will be relaxed in chapter 4).

An *internal history* is a sequence of internal events where each internal termination event is preceded by a matching internal invocation event. A *complete internal history* is an internal history with no unmatched events.

Atomicity assumption. We shall assume that there are no simultaneous updates at the internal level. Thus each pair of matched internal events constitutes an atomic operation that transforms an object implementation state in mutual exclusion. Realization of the atomicity assumption amounts to implementation of mutual exclusion by all operations at each component.

The atomicity assumption allows us to transform a sequence of events into a sequence of operations very easily. Given an internal history h, we simply consider each operation as taking effect at the time of its termination event. Thus the subsequence of termination events in h gives the sequence of operations Opseq(h) in that history, such that if Opseq(h) is applied to the initial object implementation state (ois) of the history, the system will move through precisely the same sequence of object implementation states as it did with h.

Associated with each component is a consistency constraint or an invariant for that component. A correct internal history is an internal history that satisfies the atomicity assumption and causes a state transition if and only if the consistency constraint of each component in the window of each operation is preserved as an invariant. Intuitively an internal operation should not be allowed if it invalidates the consistency constraint at a component. If each operation in an internal history preserves the consistency constraint at each component, the overall consistency constraint of the object must be preserved. Therefore such an internal history is

correct.

#### 3.7 Relating internal histories to external histories

Given a correct internal history h, we say h is an *implementation* of an external history H if the subsequence of Opseq(h) consisting of Opseq(h) with all restructuring operations removed and with the object name replacing the component names in each operation in Opseq(h) is a valid reordering of H.

In example 4.1 in the following section we demonstrate external and internal histories of the joint account object. The latter can be shown to be a correct implementation of the former.

Given the above notation for object implementation states, we can discuss partitioning, binding and restructuring in more concrete terms.

## 3.8 Partitioning, binding and restructuring

Informally, partitioning is described as the task of creating state decompositions or the task of designing an object implementation that consists of *components* that are simultaneously updatable. We shall not attempt to characterize partitioning more formally, since this intuitive notion is adequate for our purposes.

Given a set of activities, A, a state s of an object x, and an object implementation state of s given by the quadruple < Dec, Cval,  $Dec^{-1}$ , Crel >, B is a binding if it is a many to many mapping from A to Dec (s), the set of components in the decomposition of s.

Binding is thus the association between activities and components of an object. Such an association may take place statically, at time of creation of the object, or dynamically, at runtime. A binding of an activity A to an object x is static if B(A) is fixed at the time of creation of x, and this binding never changes. Similarly, a binding is dynamic if it is different at different times in the same history. For example in the case of the joint account object of section 2, B(Bob) = "checking" and B(Mary) = "savings", and this is a static binding.

Partitioning can also take place at different times. For example, an implementation of Balanced Cube object on a Hypercube [Dally '86] dynamically alters the partitioning as the size of the structure grows and shrinks, thus resulting in dynamic partitioning, or the alteration of the number of components of an object implementation state in the course of a computation. We shall see examples of dynamic binding in chapter 4.

Informally, restructuring is the task of changing an object's implementation state without changing the externally visible state of the object. Formally, restructuring is defined as a transformation in the object implementation state from ois to ois' in such a way that the inverse decomposition of both object implementation states are equal to the same object state, s. Note that we do not specify how the transformation is to take place. It could be brought about by a change in the decomposition function or a change in the component value function, or possibly even a change in the component relationships.

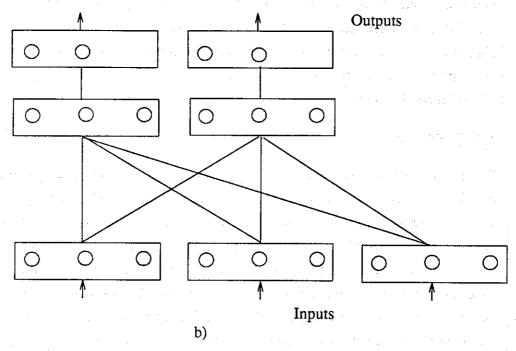

#### 3.9 The scheduler of an object and motivation for path expressions

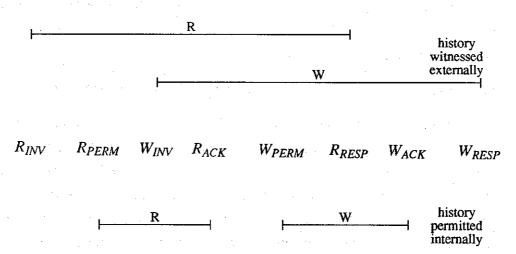

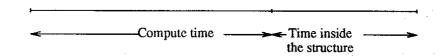

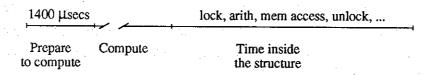

We shall informally define the scheduler for an object as an active encapsulation (because of internal activities such as restructuring activities) that allows certain sequences of events while disallowing others. The scheduler permits internal events to occur by issuing *permissions* to access partitions of an object's implementation state and receiving *acknowledgements* that signify the conclusion of such access. Simultaneous updates refer to overlapping event pairs witnessed by an external observer. An overlap witnessed externally need not correspond to an overlap permitted internally by the scheduler of an object. In fact, we have stipulated (by means of the atomicity assumption) that the only overlaps that occur internally are those that act on different components. Consider an object which may be simultaneously read but must be updated atomically. A valid history for this object is shown in Fig 3.2 (where the subscripts *PERM* and *ACK* denote the internal events *permission* and *acknowledgement* above).

By considering semantics of operations such as those of "read" and "write" we find that we can relax the atomicity assumption in certain cases. In chapter 4 we intro-

duce the language of extended path expressions for specifying when a scheduler may allow concurrent access at an object partition or component. The motivation for path expressions has traditionally come from a desire to specify a different set of concerns from those that motivate dependency relations in a programming language. Path expressions have been used for specifying the synchronization properties of objects (resources) that are in general shared by multiple activities, stating what operations can commute and what operations must be done in serial order. We use path expressions to capture sequencing restrictions in partitions of object implementation states. Our path expressions go beyond specification of synchronization and commutativity to including the capability to partition the set of activities.

Fig 3.2 Valid history for multiple reader single writer synchronization

#### 3.10 Comparison with the Karp and Miller model

At an abstract level our model of an object is similar to that of an instance of an abstract data type created by a Type manager [Browne '84] for the type of that object. The adt implementation details remain hidden. In our model we not only hide the implementation, we also guarantee that the implementation will meet the property of simultaneous update. With respect to the object implementation states we would like to compare our model with that of Karp and Miller.

Karp and Miller [Karp '69] have presented a model to represent a general class of determinate computations. This model provides for computational state to be simultaneously updated by introducing memory locations. A parallel program schema is a triple  $\langle M, A, C \rangle$ , where M is a set of memory locations, A is a set of operations and C is a control defined by means of a state machine. Operations may asynchronously read and update memory locations as long as they preserve the property that two or more concurrent executions of an operation terminate in the order of their initiation. An operation is initiated by means of an initiation symbol, and upon termination produces one of a finite set of symbols denoting the set of possible outcomes for that operation. The values that are to be written into memory and the particular choice of the outcome symbol are functionally determined by the values read from memory. Thus regardless of the relative speeds of execution (times of completion of operations) the outcome of each computation (a string of symbols accepted by this schema) is unique, in the sense that every memory cell contains a single possible sequence of values. This property is known as determinacy.

Determinacy has been further characterized [Weng '75, Kahn '74] as the property that given an arbitrary directed graph with a function  $g_i$  at each node i of p nodes, and some initial conditions, the sequence of values on all arcs is uniquely determined. The streams (sequences of values) in the arcs is precisely the fixed point of the system of equations  $Y_i = g_i$  ( $X_i$ ):  $1 \le i \le p$ , where  $Y_i$  and  $X_i$  represent respectively the output and input stream tuples corresponding to node i. The notion of histories or streams (lacking in the Karp and Miller model) is a notion that we have found very useful.

In contrasting our model of computation with the Karp and Miller model we make the following observations:

\* Our internal operations are analogous to Karp and Miller's operations; however, at any given time there may be only one outstanding initiation of an operation on a component in our model. This is necessitated by the atomicity assumption. This requirement is relaxed through the use of extended path expressions in chapter 4. We do not assume that operations terminate in the

order of their initiation.

- \* Memory locations in the Karp and Miller model are similar to components in our model.

- \* Karp and Miller have a single global control that characterizes the state transitions taking place over the entire schema. In our case the state machines are distributed in the serial specifications of different objects and there is no attempt to unite these state machines into a global state machine.

- \* Since their model is an uninterpreted (based on syntax rather than semantics of the operations) the state transition function in the Karp and Miller model is a total function on all possible outcome symbols. In our model since we have added interpretation and semantics of the abstract data types for our objects we have undefined transitions.

#### 4. Examples

## Example 4.1. The joint account object

The joint account can be expressed in terms of the notation presented in section 3. The state domain is the set of non-negative integers, with the initial state being zero. The operation invocation symbols are "deposit" and "withdraw", each with an integer argument. The response symbols are "ok" and "sorry". The system may contain several objects and activities but we are only interested in the object x which is the joint account object, and the external or user activities Bob, Mary, and the restructuring activity Bank\_Employee. We assume that the Bank\_Employee can detect the state when a client is waiting for a withdrawal and there is not enough money. In such a case the client will receive a response "sorry".

#### Serial specification:

```

S_x: { i | i is an integer \geq 0 }

I_x:0

O_x: \{ \ll \text{ withdraw, } v, A, x >, < \text{ok, } v', A, x \gg,

```

$$\ll$$

withdraw,  $v$ ,  $A$ ,  $x >$ ,  $<$  sorry, NULL,  $A$ ,  $x \gg$ ,  $\ll$  deposit,  $v$ ,  $A$ ,  $x >$ ,  $<$  ok, NULL,  $A$ ,  $x \gg$  where  $v$ ,  $v'$  are integers and  $A \in \{Bob, Mary\}$

$$T_x$$

(s,  $\ll$  withdraw,  $v$ ,  $A$ ,  $x >$ ,  $< \alpha$ ,  $v'$ ,  $A$ ,  $x >$ ) =

$$s - v \text{ if } (s \ge v \land v' = v \land \alpha = \text{"ok"})$$

$$s \text{ if } (s < v \land v' = \text{NULL } \land \alpha = \text{"sorry"})$$

$$undefined \text{ otherwise}$$

$$T_x$$

(s,  $\ll$  deposit,  $v$ ,  $A$ ,  $x >$ ,  $<$  ok, NULL,  $A$ ,  $x \gg$ ) =  $s + v$  if ( $v \ge 0$ )

undefined otherwise

Fig 4.1: An ois for the joint account object

## An object implementation state (Fig 4.1):

We show an object implementation state for which s, the abstract state is 50, and the internal state has 50 in  $c_1$ , which is the savings component, and 0 in  $c_2$ , which is the checking component.

In this case the decomposition function never changes. Thus for all  $s \in S_x$ :  $Dec(s) = \{c_1, c_2\}$  with  $D_1 = D_2 = \{i : i \ge 0\}$  Thus  $Dec(50) = \{c_1, c_2\}$   $Cval(c_1, c_2) = c_3$   $Cval(c_1, c_2) = c_3$  The inverse decomposition  $Dec^{-1}$  is the addition function. Thus:  $Dec^{-1}(c_1, c_2) = c_3$   $Cval(c_1, c_2) = c_3$   $Cval(c_1, c_2) = c_3$   $Cval(c_1, c_2) = c_3$   $Cval(c_1, c_2) = c_3$   $Cval(c_2, c_3) = c_3$   $Cval(c_3, c_3) =$

window (Bank\_Employee, op) =  $\{c_1, c_2\}$  where op  $\varepsilon$  {withdraw, deposit}

Shown below is an internal history h in which Mary makes a deposit of 50 dollars into the savings account, which is transferred to checking to cover Bob's withdrawal.

```

internal history h

< deposit, 50, Mary, c_1 >

< ok, NULL, Mary, c_1 >

< withdraw, 50, Bank_Employee, c_1 >

< ok, NULL, Bank_Employee, c_1 >

< deposit, 50, Bank_Employee, c_2 >

< ok, NULL, Bank_Employee, c_2 >

< withdraw, 50, Bob, c_2 >

< ok, 50, Bob, c_2 >

```

The sequence of operations Opseq(h) of the above history is shown below.

```

Opseq (h)

<<deposit, 50, Mary, c_1>, <ok, NULL, Mary, c_1>>

<< withdraw, 50, Bank_Employee, c_1>, < ok, NULL, Bank_Employee, c_1>>

<< deposit, 50, Bank_Employee, c_2>, < ok, NULL, Bank_Employee, c_2>>

<< withdraw, 50, Bob, c_2>, < ok, 50, Bob, c_2>>

```

The reduced operation sequence of Opseq(h) with the internal restructuring operations removed is shown below.

```

reduced Opseq (h) <<deposit, 50, Mary, c_1>, <ok, NULL, Mary, c_1>> <<withdraw, 50, Bob, c_2>, <ok, 50, Bob, c_2>>

```

The operation sequence of H', a valid reordering of the external history H is shown below.

```

Seq (H') <<deposit, 50, Mary, x >, <ok, NULL, Mary, x >> <<withdraw, 50, Bob, x >, <ok, 50, Bob, x >>

```

Finally we show the external history H and a possible internal history h that is correct implementation of H. The events are shown in chronological order.

```

External history H Internal history h < withdraw, 50, Bob, x > < deposit, 50, Mary, c_1 > < ok, NULL, Mary, c_1 > < withdraw, 50, Bank_Employee, c_1 > < ok, NULL, Bank_Employee, c_1 > < deposit, 50, Bank_Employee, c_2 > < ok, NULL, Bank_Employee, c_2 > < ok, NULL, Bank_Employee, c_2 > < withdraw, 50, Bob, c_2 > < ok, 50, Bob, c_2 > < ok, 50, Bob, c_2 > < ok, NULL, Mary, x >

```

## Example 4.2. The index server object

Often, a set object consists of an ordered set of values, such as a sequence of integers over a given range (or an array holding elements of a set, in such a manner that a sequence of integers represents indices into the array). We introduce a certain kind of object called an *index server object*, abbreviated *iso*, that returns integers from a given range.

Say we have an index server object for the integer interval [lo, hi]. Let  $Z = \{x \mid lo \le x \le hi : x, lo and hi are integers \}$  be an ordered set of integer values. The object domain of the index server object is the powerset of Z, since it may contain any of the  $2^{|Z|}$  possible subsets of Z. The initial state is the set Z. The only operation of interest is an index acquisition. The transition function defines the effect of

removing an index from an iso. The transition function is interpreted as follows: If for some  $v \{ v \in s \}$ , then the precondition that holds at an object state s, of the iso, then a get operation upon the iso returns the value v, modifying the object state s accordingly.

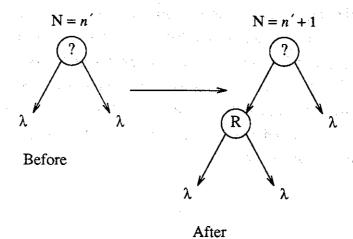

The index server object could be implemented with  $n^{\dagger}$  components  $\{c_1, c_2, \dots, c_n\}$ , each component initialized to hold a partition of Z. Let the  $i^{th}$  component,  $c_i$ ,  $1 \le i \le n$ , have associated state variables  $lo_i$  and  $hi_i$ , such that component  $c_i$  contains the integers  $lo_i$  to  $hi_i$ .

Initially  $Dec^{-1} < Cval(c_1)$ ,  $Cval(c_2) \cdots$ ,  $Cval(c_n) > = Z$ . Thus each component is suitably initialized to "contain" a subset of Z. Taken together the components implement the entire set.

## Serial specification:

$S_x: 2^Z$ , the powerset of Z where  $Z = \{i \mid lo \le i \le hi : i, lo and hi are integers \}$  $I_x: Z$

$$O_x$$

: {  $\ll$  get, NULL,  $A$ ,  $x$  >,  $<$  ok,  $v'$ ,  $A$ ,  $x$  >>,  $\ll$  get, NULL,  $A$ ,  $x$  >,  $<$  sorry, NULL,  $A$ ,  $x$  >>, where  $v'$  is an integer between lo and hi and  $A \in AC$  }

$$T_x$$

(s,  $\ll$  get, NULL,  $A$ ,  $x >$ ,  $< \alpha$ ,  $v'$ ,  $A$ ,  $x \gg$ ) =

$$s - \{v'\} \text{ if } (v' \in s \land \alpha = \text{"ok"})$$

$$s \text{ if } (s = \{\} \land v' = \text{NULL } \land \alpha = \text{"sorry"})$$

$$undefined \text{ otherwise}$$

An object implementation state: (s is the initial state)

$$Dec (s) = \{ c_i : 1 \le i \le n \}$$

Cval

$$(c_i) = \langle lo_i, hi_i \rangle$$

:  $1 \le i \le n$

where  $lo_i = (i-1) * \frac{IndexLimit}{n} + 1$ ;  $hi_i = i * \frac{IndexLimit}{n}$

$$Dec^{-1}$$

( <  $Cval$  ( $c_1$ ),  $Cval$  ( $c_2$ ),  $\cdots$ ,  $Cval$  ( $c_n$ ) > )

$<sup>\</sup>dagger n$  is a parameter to be tuned for performance.

$$= Cval(c_1) \cup Cval(c_2) \cdots \cup Cval(c_n) = Z$$

The above *ois* applies to the initial state. In general the inverse decomposition function gives the external state of the object as follows:

$$Dec^{-1} (< Cval (c_1), Cval (c_2), \cdots Cval (c_n) >) =$$

$$\{ lo_1, \cdots, hi_1, lo_2, \cdots, hi_2, \cdots lo_n, \cdots, hi_n \} = s$$

$$Crel = \{ (c_i, c_{i+1}) : 1 \le i < n \} \cup (c_n, c_1)$$

The window function associates an activity doing a particular operation upon the index server object with a single component, i.e. the one to which the activity is currently bound. The component relationships represent a circular list. Note that our implementation will be capable of yielding only a subset of possible sequences from the set Z. In this sense it does not implement the full behaviour of the set. However it does satisfy the serial specification of the set since the serial specification does not require that all possible sequences should be obtainable.

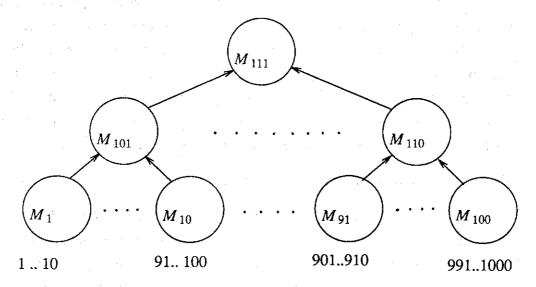

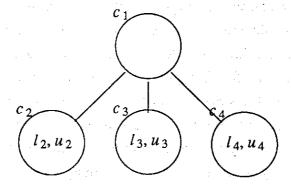

## Example 4.3. The software combining tree

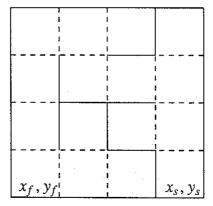

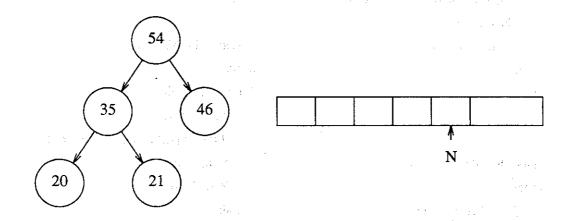

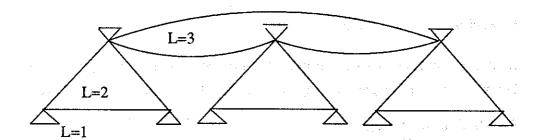

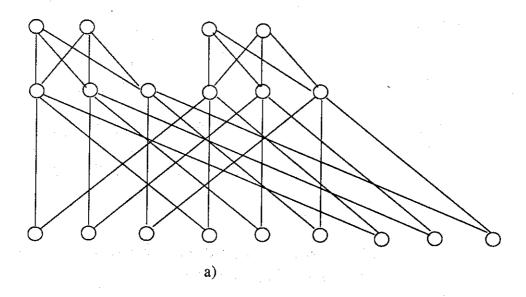

A replace add interconnection network can be regarded as a collection of fan-in trees, or inverted trees with memory cells at the root and processing elements at the leaves. A fan-in tree may get requests much faster than the requests are satisfied, thereby causing the tree to get congested. Congested trees of this nature are severe bottlenecks because they impede the flow of traffic that is otherwise unrelated. Yew  $et\ al\ [Yew\ '87]$  propose to reduce such contention for a given memory cell by distributing accesses to it across several memory cells, and imposing a global structure across these cells. This structure can be simultaneously updated at several points, thereby relieving contention at the bottleneck. The structure selected by the authors is a k-ary tree called a  $software\ combining\ tree$ . However, there is no reason why it should not be some other structure (such as that of the last example). It is clear that in order to reduce contention the authors have introduced structure into the object, and then introduced partitioning. Let d be the depth of the software combining tree, k the arity and k the largest value (assuming the initial value is 1). k denotes the number of processors. Taking the values of k, k, and k from the

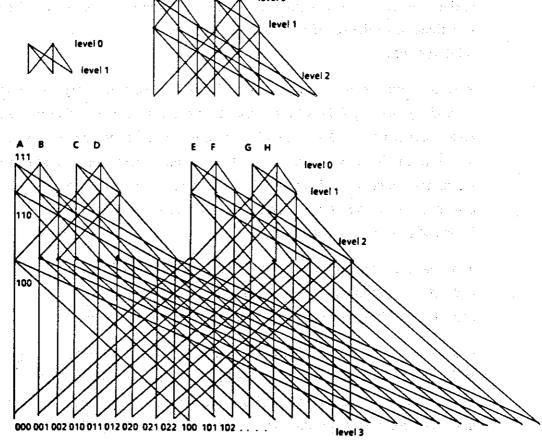

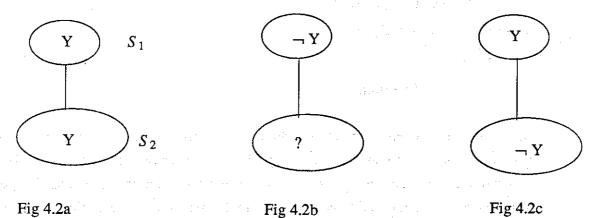

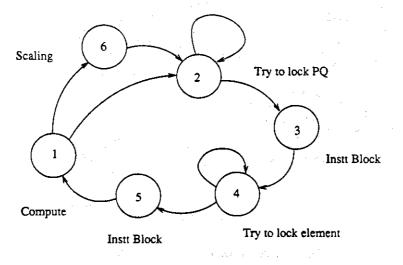

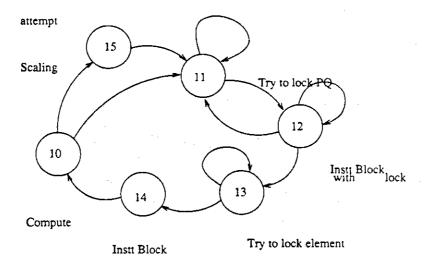

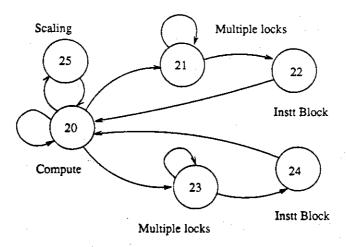

example in [Yew '87], we have L=N=1000, d=2 and k=10, we have 111 memory cells in the tree, with 100 cells at the leaf level. We partition the processors into 100 sets of ten processors each, with each set sharing a leaf level memory cell. When the last processor in each set decrements the contents of its memory cell to zero, it then decrements the value in the parent cell. Thus there are 111 bottlenecks, each with 10 accesses. Fig 4.2 illustrates this software combining tree. We illustrate the ois with a simplified version of this tree with three leaf components and one root component (see Fig 4.3).

Fig 4.2 A software Combining tree with N = 1000, k = 10 and d = 2

Serial specification. The serial specification are the same as those of the *iso*, and therefore not being repeated here.

Fig 4.3: An ois of the software combining tree

## An object implementation state (Fig 4.3):

Dec

$$(s) = \{ c_1, \dots, c_4 \}$$

$Cval (c_k) = \langle l_k, u_k \rangle : 2 \leq k \leq 4, Cval (c_1) = NULL$

$Dec^{-1}$  is the union function which is the same as the inverse decomposition function of the index server object.

$$Crel = \{ \langle c_1, c_2 \rangle, \langle c_1, c_3 \rangle, \langle c_1, c_4 \rangle \}$$

# 5. Performance tradeoffs in partitioning, binding and restructuring

What is unique about the index server object and software combining tree? At an abstract level, both these objects behave exactly as a set data type with the operation get (in the case of a combining network this operation is done by the RepAdd or "replace-add" primitive instruction) being analogous to the operation of removing an element from a set. Thus, if an activity invokes a get operation, and there is no element (i.e. index) in the partition to which it is bound, the operation must not return failure without making sure that there is indeed no index available in any partition of the object. In the case of the iso the linked list of partitions may, if desired, be traversed by a request until a non-empty partition is found, or all partitions are seen to be empty in which case the request returns with a failure.

In the case of a software combining tree, a request that finds a partition empty will

continue to be an outstanding request until all indices are exhausted from all partitions. At this time the request will return with a failure, thus retaining consistency with the abstract specifications. A tree of barriers is used to implement the synchronization necessary for all requesting activities to terminate at the same time. At each internal node of this tree only one activity is pre-selected to propagate a termination request up, and confirmation down the tree. Thus even though a large number of activities may be actually waiting at a barrier, at a given time only few of them are actively waiting at a specific memory location. Thus memory contention is greatly reduced. This is the performance advantage of the software combining tree.

The main questions are:

- i) Under what conditions are such partitioning and binding strategies useful?

- ii) What exactly is gained by having multiple binding times?

These questions are addressed by means of simple performance models.

Say the index server object is mapped onto a distributed memory machine, where the activities are organized as a ring. A natural way to map the circular list of components of an ois is as a ring upon this ring. Let us assume that the number of partitions equals the number of processors, n. We assume that activities are statically bound to partitions, with one activity being assigned to each processor, and that termination is signalled by a token that propagates through the linked list of components (processors). The time taken to complete the consumption of all indices, called the completion time of the index server object, is given by:

$$T_{iso} = Max_{i=1}^{n} \left\{ Tpart_{i} \right\} + n * T_{message}$$

where  $Tpart_i$  is the time to complete consumption of all indices in partition i, and  $T_{message}$  is the time for propagation of a message down one link of the ring. The maximum is taken over all partitions.  $T_{iso}$  is obviously dependent upon the distribution of computation times at partitions. Skewed distributions of computation

<sup>†</sup> A barrier is a shared memory location used to implement a synchronization point for a set of activities.

times at partitions can seriously affect the overall completion time. We therefore propose an alternate implementation using compile time partitioning initially, but with a provision for sharing work at runtime through dynamic binding of activities to partitions. Assuming that k\% of the requests are directed at other partitions where k (a small positive integer less than n) is the distance propagated by a request increases as we near completion of the computation. Thus the distance propagated by the last 1% is larger than that propagated by the last but one 1% and so on. This scheme can capture skewed distributions by distinguishing between the values of k at different components. The analysis of this scheme is a little more complex. Let us assume that the computation time for an index  $T_{index}$ , is much less than the communication time  $T_{message}$ . Thus once communication starts, the time is dominated by the communication time. We also assume that the ith component directs  $k_i$ % of its requests at other partitions. Thus skewed index distributions are captured by skewing the distribution of values given to  $k_i$ . We assume 100 requests are made at each partition.  $T_{message}$  is the average time for a message to travel a single hop in the presence of other messages.

$$T_{iso} = Max_{i=1}^{n} \left\{ (100 - k_i) * T_{index} + \left[ n + (n-1) + \dots + (n-k_i + 1) \right] * T_{message} \right\}$$

$$= Max_{i=1}^{n} \left\{ (100 - k_i) * T_{index} + \left[ \frac{n(n+1)}{2} - \frac{k_i(k_i + 1)}{2} \right] * T_{message} \right\}$$

#### 5.1 Restructuring

The above analysis assumes one activity per component. There could be many activities per component, exemplified by several processes on a single processor. Indeed, it would be very inefficient if in the presence of skewed data, as above, each activity were to incur the messaging overhead shown above. Instead, we propose restructuring activities that dynamically alter the bounds of the implementation of partitions of the index server object. The analysis of restructuring is as follows. At each processor we have a fixed number of activities and a restructuring activity. Activities are statically bound. Termination is signalled by messages between restructuring activities. Assuming the computation is equally distributed

by the restructuring, the time for the index server object is the time for R rounds of message exchanging to accomplish a uniform distribution of indices.

$$T_{iso} = \frac{Number\ of\ Indices}{n} * T_{index} + n * R * T_{message}$$

#### 5.2. Degrees of simultaneity and contention

Two other performance measures by which simultaneously updatable objects can be rated are the degrees of simultaneity and the degree of contention. The degree of simultaneity of an object is the number of operations that it allows to proceed concurrently, or in an overlapped fashion. The degree of contention is the number of activities that may potentially access an object partition. For example, the degree of simultaneity of an index server object implementation, is precisely the number of partitions, n. The degree of contention is 1 in this case. The degree of simultaneity for the software combining tree with arity k and depth d is the number of leaves in the tree, i.e.  $k^d$ . By dividing L, the largest value, into  $k^d$  memory cells, and binding a different set of processors to each memory cell, we have guaranteed that the maximum number of contending requests at a single cell is  $\frac{\min(L,N)}{k^d}$ . This is the degree of contention of the software combining tree. We shall use these performance measures once again in chapter 5 when we characterize the performance of the concurrent heap.

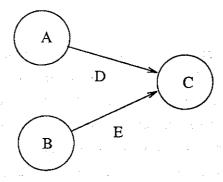

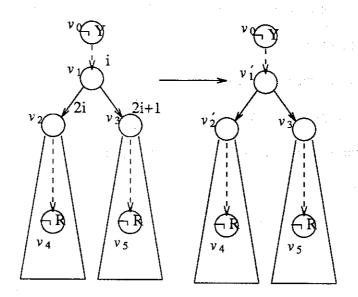

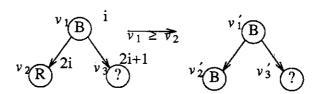

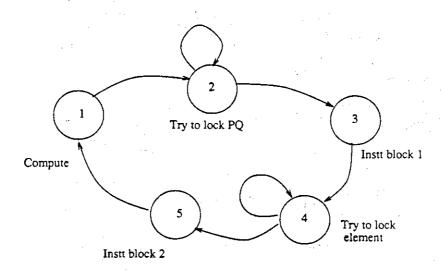

#### 6. The Doall node of TDFL

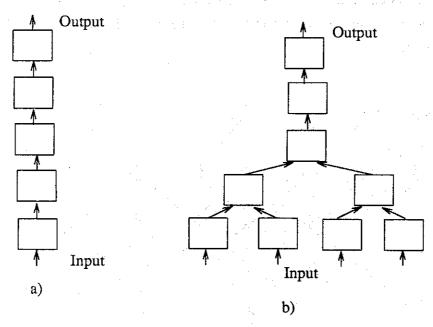

The Task-Level Data Flow Language (TDFL) is a graph oriented language for converting existing sequential programs to run in parallel, or writing entirely new programs. Computations in this language are expressed as static or dynamic directed graphs. Each node contains a subroutine-sized task and each arc holds data tokens that cause nodes to fire and emerge from nodes that have fired (Fig 6.1). The task functions are written in standard high-level languages. At any given time in the execution of a TDFL program, several nodes may be in execution, having consumed tokens from their input arcs and in due course, providing tokens on their output arcs. This language has been used to write application programs for a shared memory multiprocessor machine, with good speedups over a range of applications

and close to linear speedup in one application [Biswas '87a]. Further details of this language and its implementation appear in [Suhler '87].

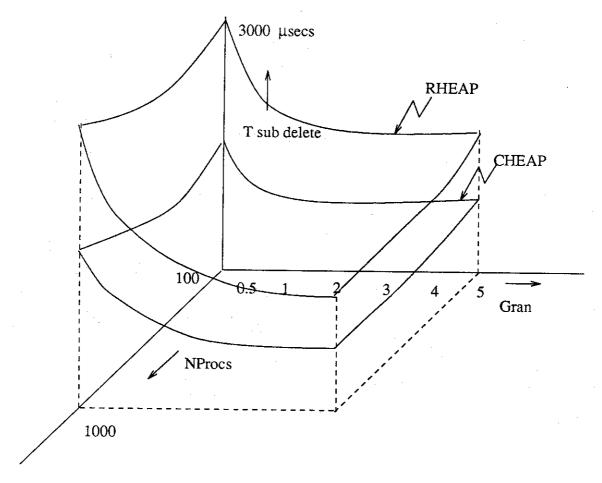

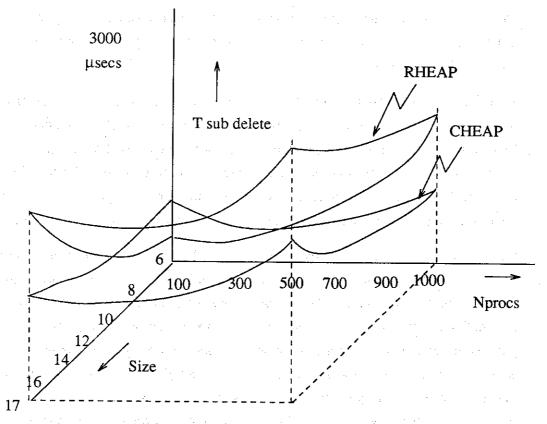

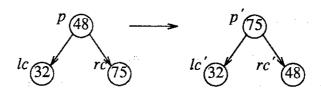

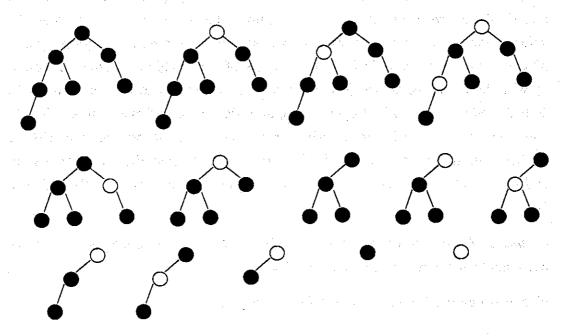

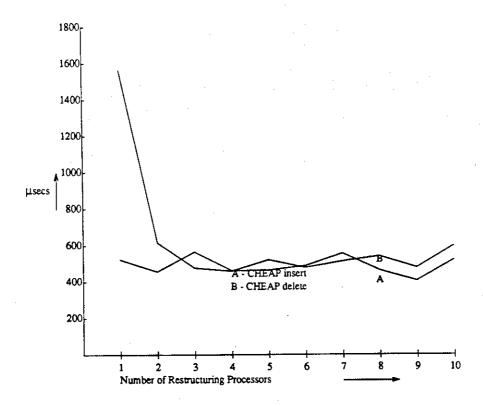

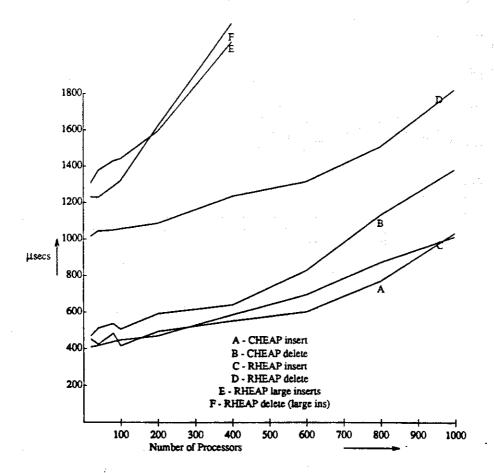

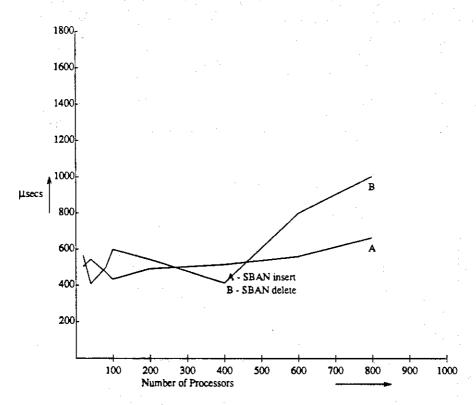

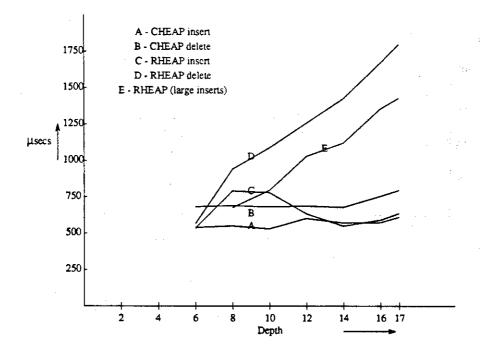

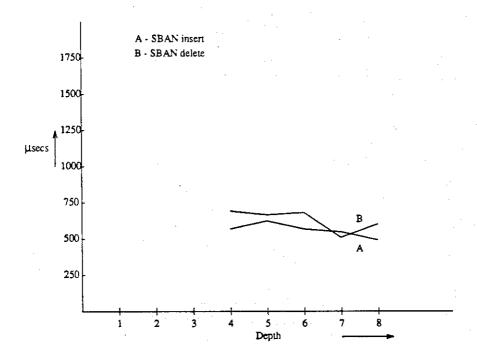

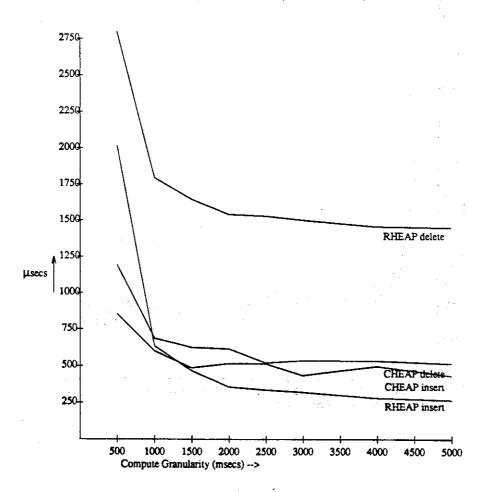

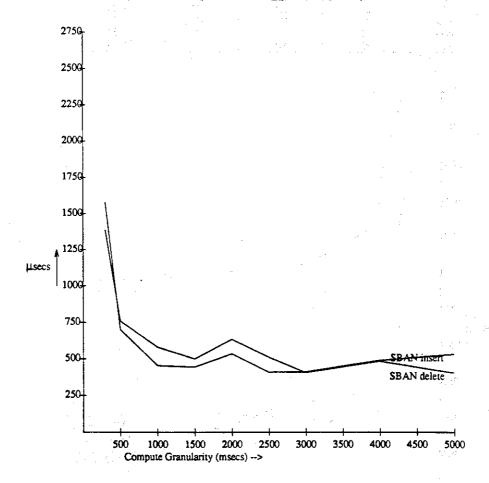

Fig 6.1